Содержание

- 2. Системное программирование Капитонов Александр Георгиевич, доцент кафедры специализированных компьютерных систем

- 3. Архитектура и система команд

- 4. Архитектура и система команд Машинные команды — явно заданные инструкции, которые: управляют пересылкой информации внутри компьютера,

- 5. Архитектура и система команд Память : первичная (primary storage) — быстродействие которой определяется скоростью работы электронных

- 6. Архитектура и система команд Интерфейс : совокупность средств, обеспечивающих сопряжение устройств и программных модулей как на

- 7. Архитектура и система команд Архитектура ЭВМ — система команд, организация аппаратного обеспечения, ее реализующего, стандарты и

- 8. Архитектура и система команд Принципы фон - неймановской архитектуры Принцип хранимой программы. Линейное пространство памяти. Последовательное

- 9. Архитектура и система команд Команды: ◆ арифметические; ◆ логические; ◆ передачи данных; ◆ перехода; ◆ пропуска;

- 10. Архитектура и система команд Формат команды ◆ поле префиксов — элемент команды, который уточняет или модифицирует

- 11. .data . . . string1 db '0123456789',0ah,0dh,'$' string2 db '0123406789','$' . . . .code . .

- 12. Архитектура и система команд Типы операндов : ◆ байт; ◆ слово; ◆ десятичный операнд; ◆ разряд;

- 13. Архитектура и система команд Двоичная система исчисления 2310 = 1∙16 + 1∙4 + 1∙2 + 1∙1

- 14. Архитектура и система команд Двоичная система - сложение 01000001 65 00101010 42 01101011 107 00111100 60

- 15. Архитектура и система команд Дополнительный код - вычитание 00110101 53 11001010 -53 в инверсном коде 00000001

- 16. Архитектура и система команд Дополнительный код Для представления отрицательного двоичного числа в дополнительном коде необходимо инвертировать

- 17. Архитектура и система команд Шестнадцатиричная система исчисления 2310 = 1∙16 + 7∙1 = 1∙161 +7∙160 =

- 18. ASCII (American National Standard Code for Information Interchange)

- 19. Структурная схема МП семейства Р6

- 20. Режимы работы процессора архитектуры IA-32 Режим реальных адресов, или просто реальный режим (real mode) — режим

- 21. Программная модель IA-32 Программная модель описывает видимые для программиста объекты архитектуры процессора: пространство адресуемой памяти до

- 22. Организация памяти ОЗУ организовано как последовательность ячеек — байтов. Один байт состоит из восьми битов. Каждому

- 23. Формирование физического адреса в реальном режиме Характеристики механизма адресации физической памяти в реальном режиме: Диапазон изменения

- 24. Формирование физического адреса в реальном режиме

- 25. Формирование физического адреса в реальном режиме Недостатки организации памяти в реальном режиме: сегменты бесконтрольно размещаются с

- 26. Регистры общего назначения Регистры общего назначения используются в программах для хранения: операндов логических и арифметических операций;

- 27. Регистры общего назначения РОН могут быть неравнозначны и при использовании определенных инструкций могут иметь специальное значение:

- 28. Сегментные регистры Любая программа состоит из трех сегментов: кода, данных и стека. Имеется 6 сегментных регистров

- 29. Регистры состояния и управления 2 регистра, постоянно содержащие информацию о состоянии как самого процессора, так и

- 30. Регистр флагов

- 31. Флаги состояния Флаг переноса (carry flag) CF: 1 — арифметическая операция произвела перенос из старшего бита

- 32. Флаги состояния Флаг знака (sign flag) SF: 1 — старший бит результата (бит 7, 15 или

- 33. Флаг управления Флаг направления (directory flag) DF. Определяет направление поэлементной обработки в цепочечных операциях: от начала

- 34. Системные флаги Флаг трассировки (trace flag) TF: 1 — процессор генерирует прерывание с номером 1 после

- 36. Скачать презентацию

Применение облачных технологий в образовательном процессе профессиональной образовательной организации

Применение облачных технологий в образовательном процессе профессиональной образовательной организации Свойства информации. Измерение информации. Кодирование информации. Помехоустойчивое кодирование. Код хемминга. (Лекция 2)

Свойства информации. Измерение информации. Кодирование информации. Помехоустойчивое кодирование. Код хемминга. (Лекция 2) Типы данных и операторы

Типы данных и операторы СУБД MySQL. Язык обработки данных SQL

СУБД MySQL. Язык обработки данных SQL Компьютерные вирусы и антивирусные программы

Компьютерные вирусы и антивирусные программы Основы программирования. Представление графов

Основы программирования. Представление графов Клиент- серверное взаимодействие

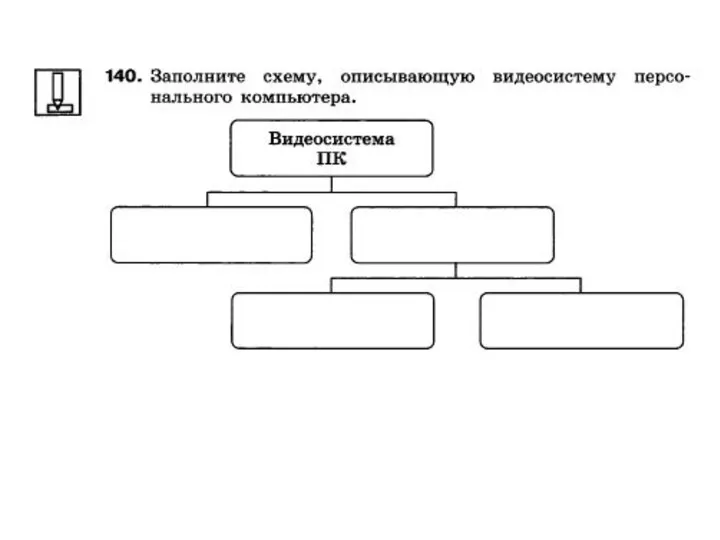

Клиент- серверное взаимодействие Задачи на графические изображения

Задачи на графические изображения Урок - презентация по теме: INTERNET - плюсы и минусы!

Урок - презентация по теме: INTERNET - плюсы и минусы! Порядок подачи заявления на изготовление сертификата электронной подписи на портале Удостоверяющего центра

Порядок подачи заявления на изготовление сертификата электронной подписи на портале Удостоверяющего центра Табличний процесор. MS Excel

Табличний процесор. MS Excel Компьютерная графика. (Лекция 1)

Компьютерная графика. (Лекция 1) Интернет-термины

Интернет-термины Информационные системы и технологии. PDM - системы. Лекция 11

Информационные системы и технологии. PDM - системы. Лекция 11 Коммуникационные технологии

Коммуникационные технологии Антивирусные программы и программы архиваторы

Антивирусные программы и программы архиваторы Организация интернет-СМИ

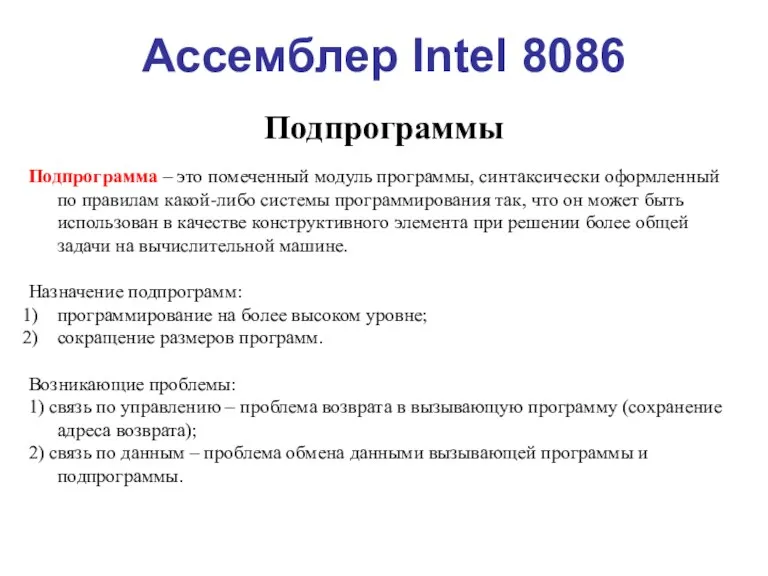

Организация интернет-СМИ Программирование на ЯВУ. Ассемблер Intel 8086. Лекция 9

Программирование на ЯВУ. Ассемблер Intel 8086. Лекция 9 Transonic Flow Over a NACA 0012 Airfoil

Transonic Flow Over a NACA 0012 Airfoil Solid - принципы с примерами PHP

Solid - принципы с примерами PHP Технологии спектрального уплотнения каналов в ВОСП

Технологии спектрального уплотнения каналов в ВОСП Информационные ресурсы сети Интернет

Информационные ресурсы сети Интернет История развития вычислительной техники

История развития вычислительной техники 20231013_graficheskiy_redaktor

20231013_graficheskiy_redaktor Градивни шаблони

Градивни шаблони Основы алгоритмизации и программирования. Лекция 15. Динамические структуры данных

Основы алгоритмизации и программирования. Лекция 15. Динамические структуры данных Программирование разветвляющихся алгоритмов. Начала программирования

Программирование разветвляющихся алгоритмов. Начала программирования Информация. Измерение количества информации

Информация. Измерение количества информации