Содержание

- 2. Методы распределения памяти с использованием дискового пространства Виртуальная память

- 3. Оверлеи Уже достаточно давно пользователи столкнулись с проблемой размещения в памяти программ, размер которых превышал имеющуюся

- 4. Достоинства и недостатки оверлеев Достоинства Возможность запускать программы размером большим, чем размер оперативной памяти; Не требуется

- 5. История возникновения виртуальной памяти Развитие методов организации вычислительного процесса в этом направлении привело к появлению метода,

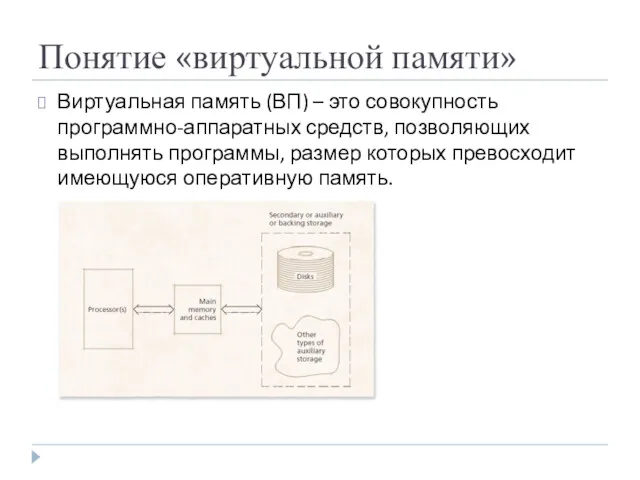

- 6. Понятие «виртуальной памяти» Виртуальная память (ВП) – это совокупность программно-аппаратных средств, позволяющих выполнять программы, размер которых

- 7. Менеджер виртуальной памяти Реализацией механизма виртуальной памяти занимается специальный менеджер. Менеджер виртуальной памяти выполняет три основные

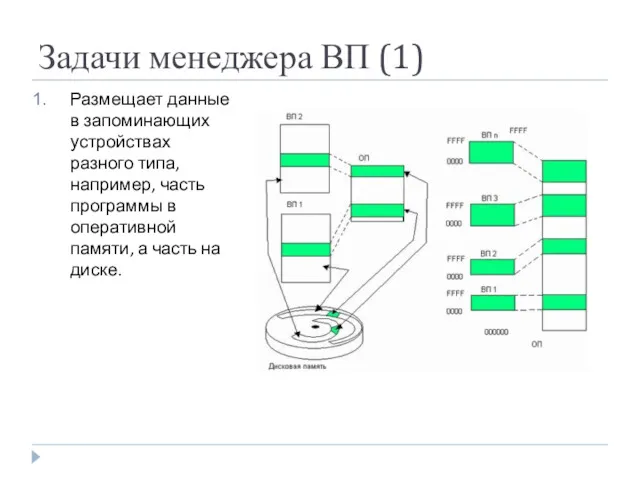

- 8. Задачи менеджера ВП (1) Размещает данные в запоминающих устройствах разного типа, например, часть программы в оперативной

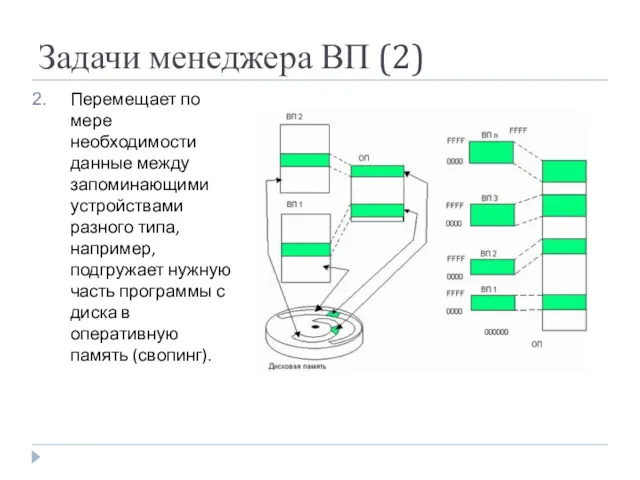

- 9. Задачи менеджера ВП (2) Перемещает по мере необходимости данные между запоминающими устройствами разного типа, например, подгружает

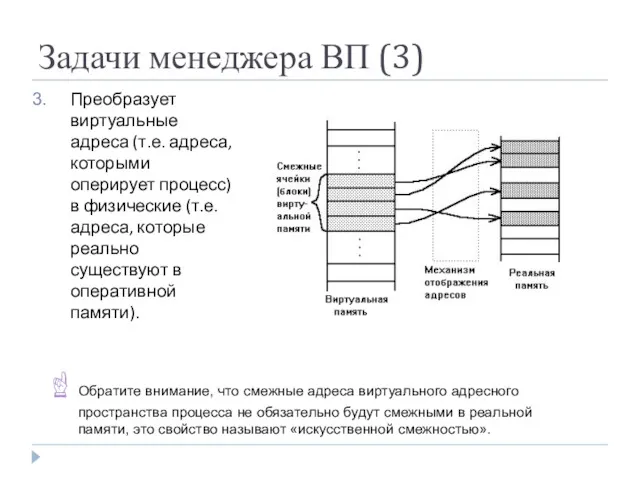

- 10. Задачи менеджера ВП (3) Преобразует виртуальные адреса (т.е. адреса, которыми оперирует процесс) в физические (т.е. адреса,

- 11. Способы организации виртуальной памяти страничное распределение сегментное распределение сегментно-страничное распределение

- 12. Методы распределения памяти с использованием дискового пространства Страничное распределение

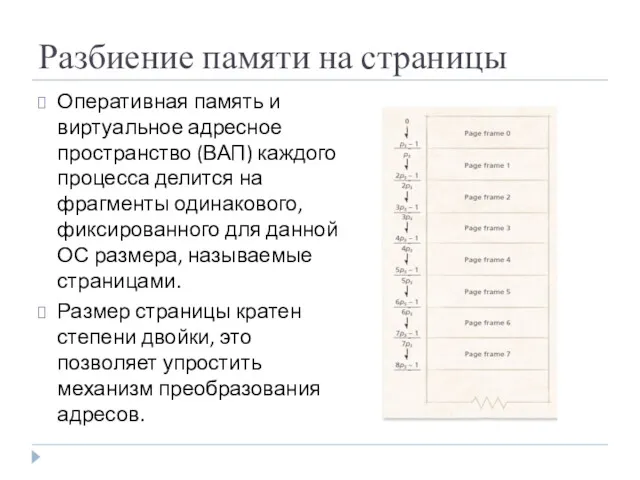

- 13. Разбиение памяти на страницы Оперативная память и виртуальное адресное пространство (ВАП) каждого процесса делится на фрагменты

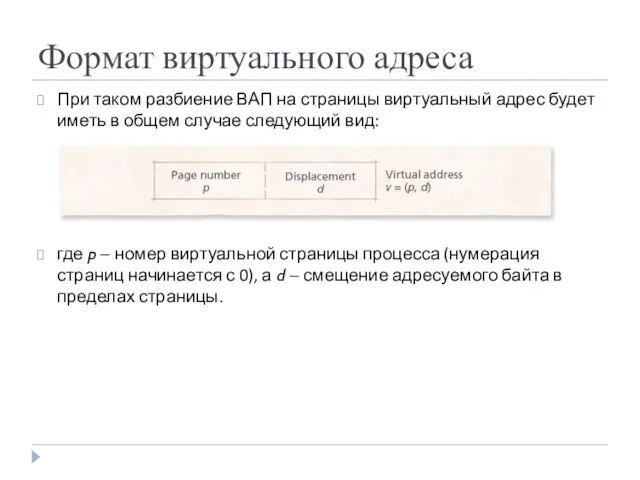

- 14. Формат виртуального адреса При таком разбиение ВАП на страницы виртуальный адрес будет иметь в общем случае

- 15. Таблица страниц процесса Система отображения виртуальных адресов в физические сводится к системе отображения виртуальных страниц в

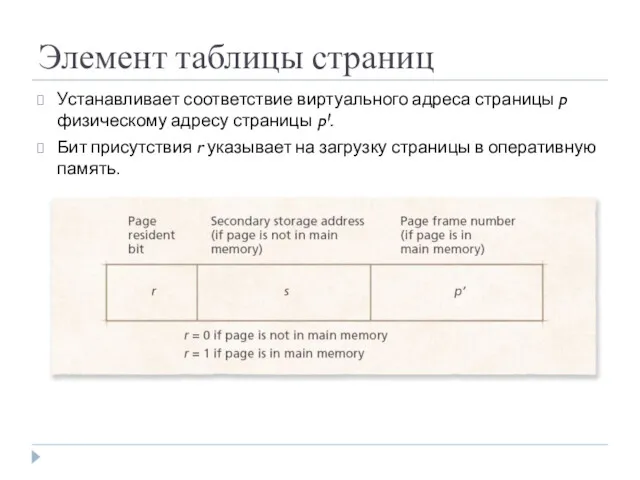

- 16. Элемент таблицы страниц Устанавливает соответствие виртуального адреса страницы p физическому адресу страницы pꞋ. Бит присутствия r

- 17. Перемещение страницы из вторичной памяти в первичную При каждом обращении к памяти происходит чтение из таблицы

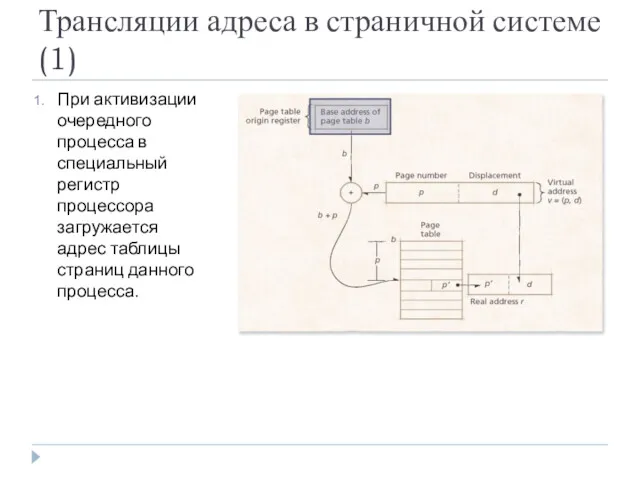

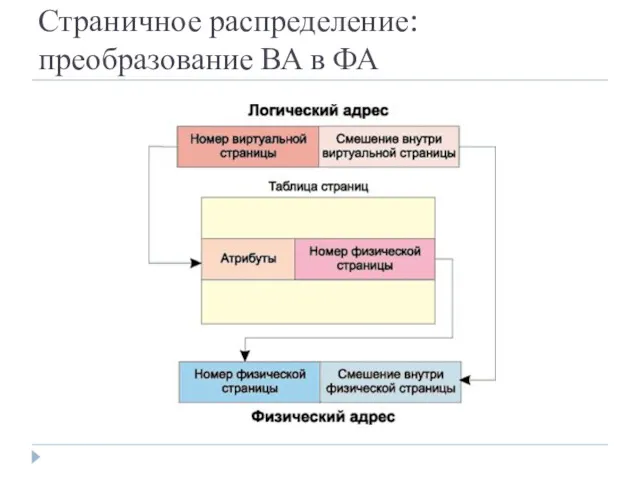

- 18. Трансляции адреса в страничной системе (1) При активизации очередного процесса в специальный регистр процессора загружается адрес

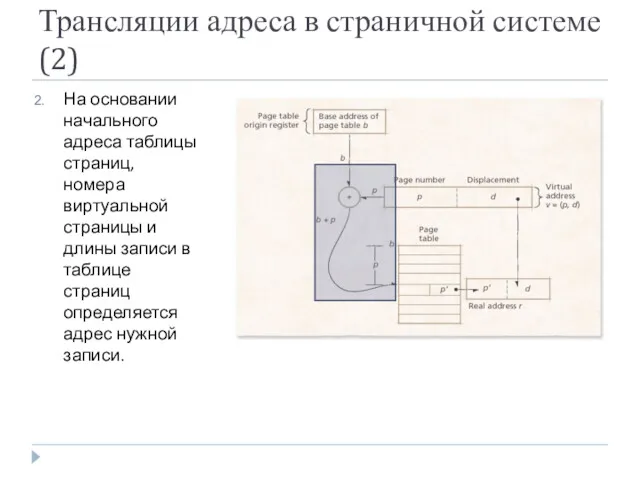

- 19. Трансляции адреса в страничной системе (2) На основании начального адреса таблицы страниц, номера виртуальной страницы и

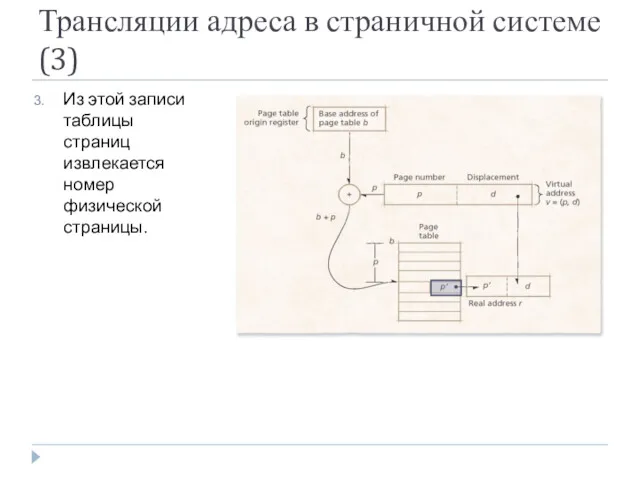

- 20. Трансляции адреса в страничной системе (3) Из этой записи таблицы страниц извлекается номер физической страницы.

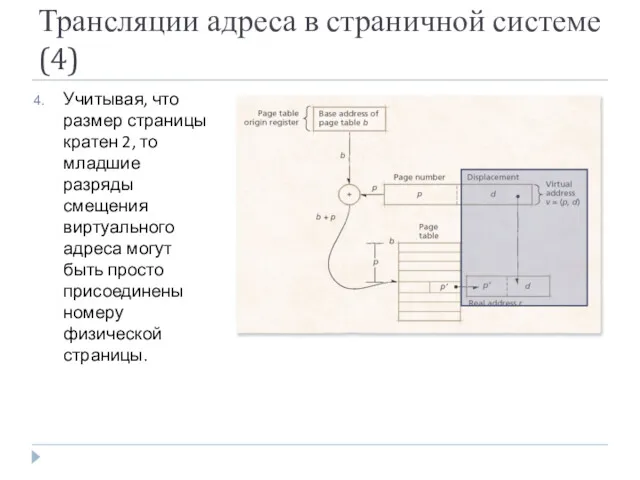

- 21. Трансляции адреса в страничной системе (4) Учитывая, что размер страницы кратен 2, то младшие разряды смещения

- 22. Страничное распределение: преобразование ВА в ФА

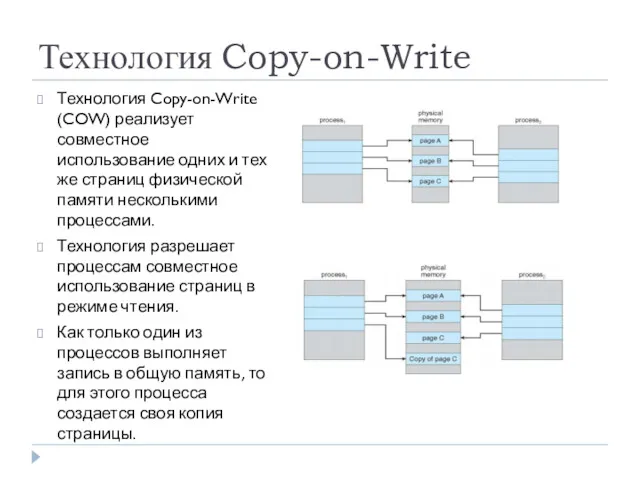

- 23. Технология Copy-on-Write Технология Copy-on-Write (COW) реализует совместное использование одних и тех же страниц физической памяти несколькими

- 24. Применение Copy-on-Write Технология Copy-on-Write применяется в UNIX-системах для экономии памяти и ускорения запуска дочерних процессов. Когда

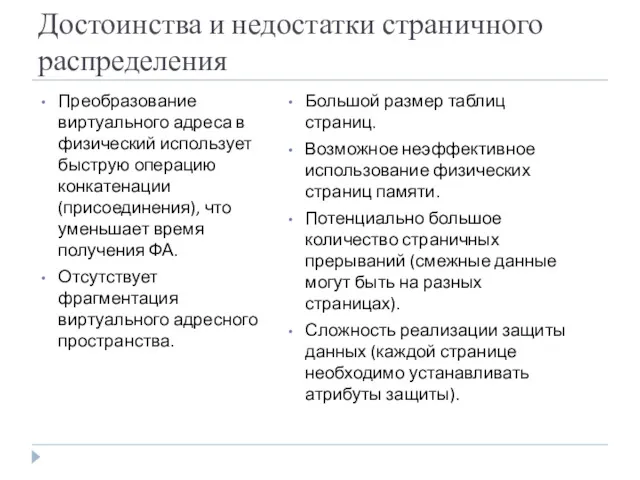

- 25. Достоинства и недостатки страничного распределения Преобразование виртуального адреса в физический использует быструю операцию конкатенации (присоединения), что

- 26. Выбор размера страницы при малых страницах: меньшая внутренняя фрагментация страниц и повышается эффективность использования оперативной памяти;

- 27. Расчет размера таблицы страниц Характеристика вычислительной системы: 32 битное виртуальное адресное пространство размер страницы – 4Кбайта

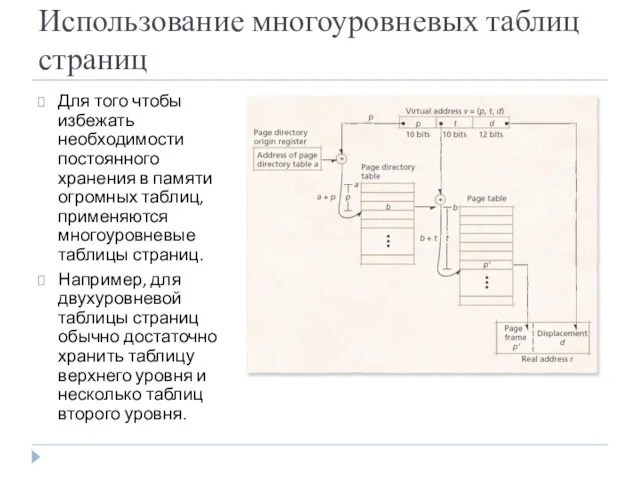

- 28. Использование многоуровневых таблиц страниц Для того чтобы избежать необходимости постоянного хранения в памяти огромных таблиц, применяются

- 29. Примеры реализации многоуровневых таблиц страниц Количество уровней в таблице страниц зависит от конкретных особенностей архитектуры. Можно

- 30. Вопрос Какой будет формат физического адреса при использовании трехуровневой таблицы страниц?

- 31. Методы распределения памяти с использованием дискового пространства Ускорение преобразования страничных адресов

- 32. Ускорение преобразования страничных адресов При каждом обращении к памяти выполняется табличное преобразование виртуального адреса в физический

- 33. Ускорение преобразования страничных адресов Ассоциативный буфер трансляции

- 34. Ассоциативный буфер трансляции Для ускорения процесса преобразования адреса современные процессоры используют ассоциативный буфер трансляции (translation look-aside

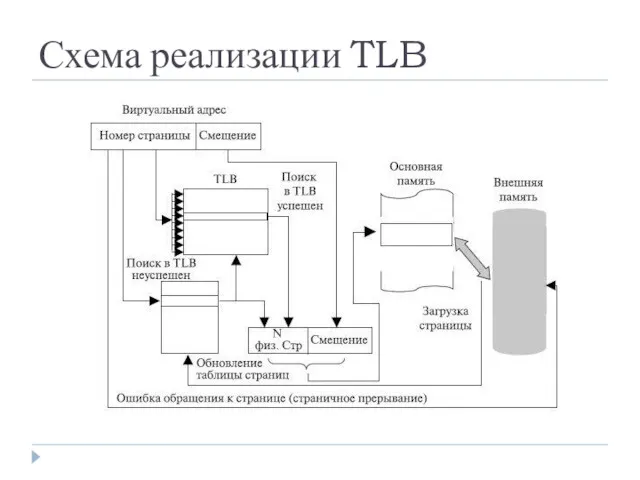

- 35. Схема реализации TLB

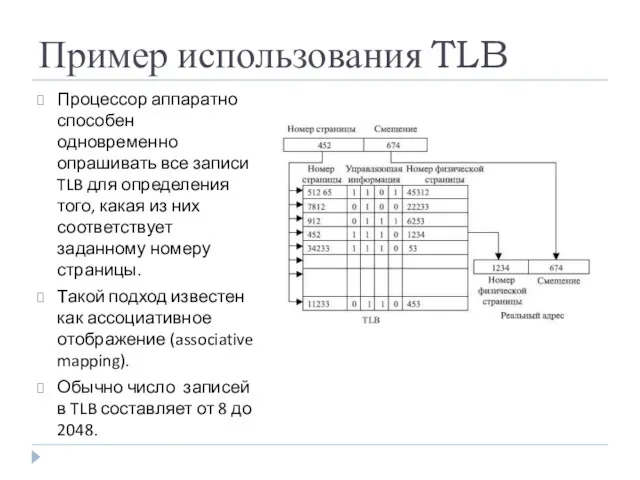

- 36. Пример использования TLB Процессор аппаратно способен одновременно опрашивать все записи TLB для определения того, какая из

- 37. Повышение эффективности TLB Результативность поиска в TLB определенного размера с ростом размера ВАП процессов и уменьшением

- 38. Проблемы использования TLB При переключении процессов нужно добиться того, чтобы новый процесс не видел в ассоциативной

- 39. Zero level paging Таблица страниц отсутствует вообще. TLB-буфер очень большой, чтобы хранить все (или большинство) преобразований

- 40. Ускорение преобразования страничных адресов Инвертированные таблицы страниц

- 41. Инвертированные таблицы страниц Несмотря на многоуровневую организацию, хранение нескольких таблиц страниц большого размера по-прежнему представляют собой

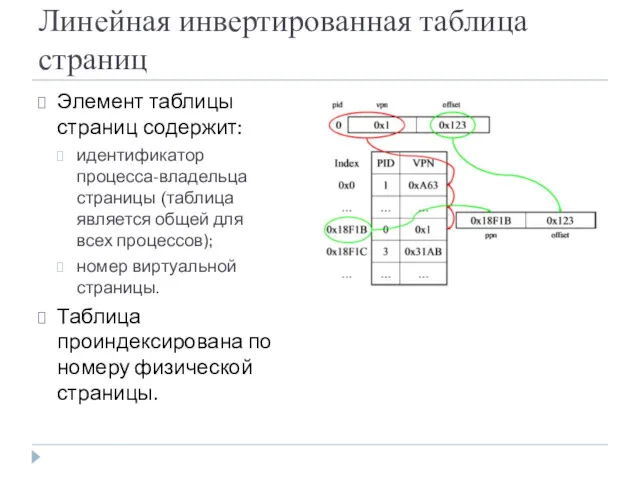

- 42. Линейная инвертированная таблица страниц Элемент таблицы страниц содержит: идентификатор процесса-владельца страницы (таблица является общей для всех

- 43. Проблемы использования инвертированных таблиц страниц Несмотря на экономию оперативной памяти, применение линейных инвертированных таблиц имеет существенный

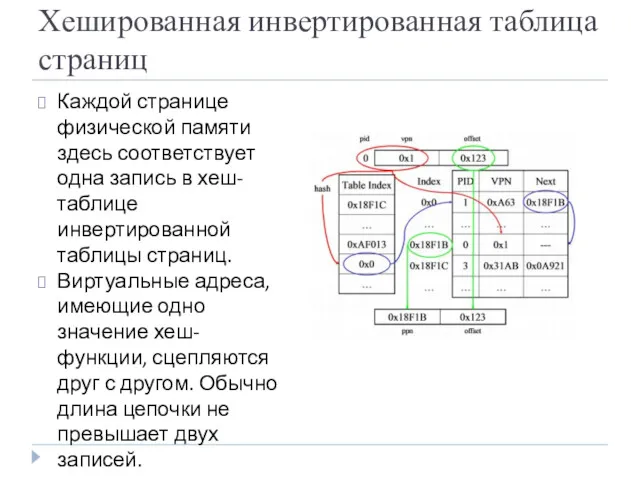

- 44. Хешированная инвертированная таблица страниц Каждой странице физической памяти здесь соответствует одна запись в хеш-таблице инвертированной таблицы

- 45. Вопрос От чего зависит размер инвертированной таблицы страниц?

- 46. Методы распределения памяти с использованием дискового пространства Сегментное распределение

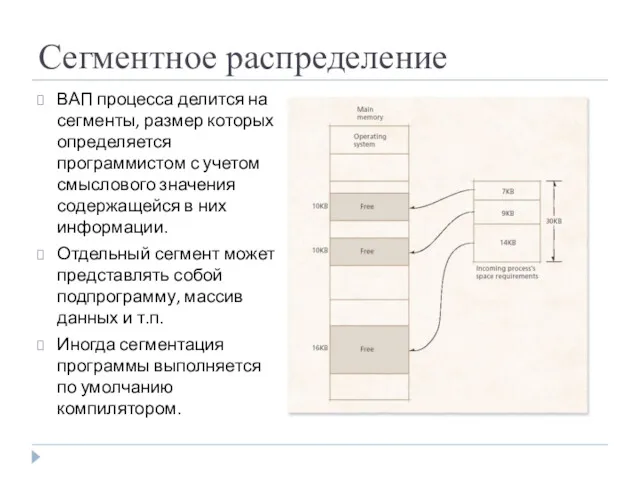

- 47. Сегментное распределение ВАП процесса делится на сегменты, размер которых определяется программистом с учетом смыслового значения содержащейся

- 48. Формат виртуального адреса При таком разбиение ВАП на сегменты виртуальный адрес будет иметь в общем случае

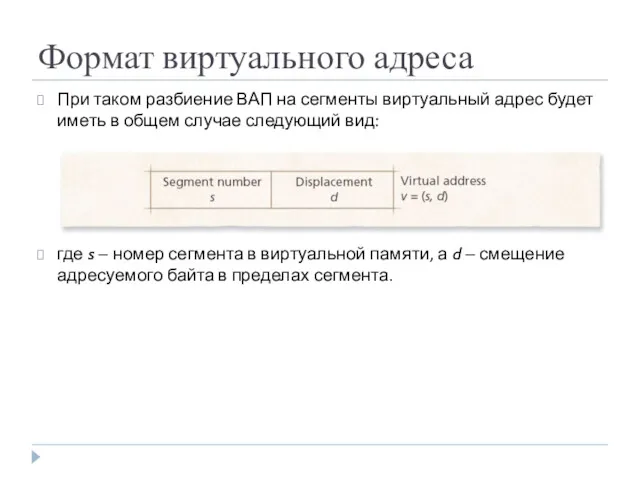

- 49. Таблица сегментов процесса Точно так же, как и при страничной организации используются таблицы страниц, при сегментной

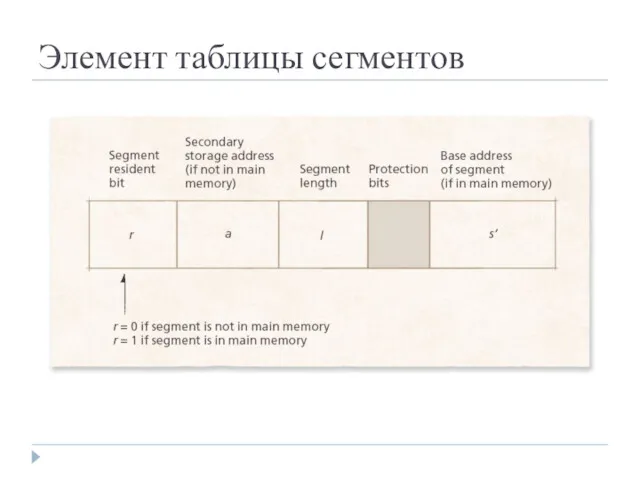

- 50. Элемент таблицы сегментов

- 51. Перемещение сегментов из вторичной памяти в первичную Система с сегментной организацией функционирует аналогично системе со страничной

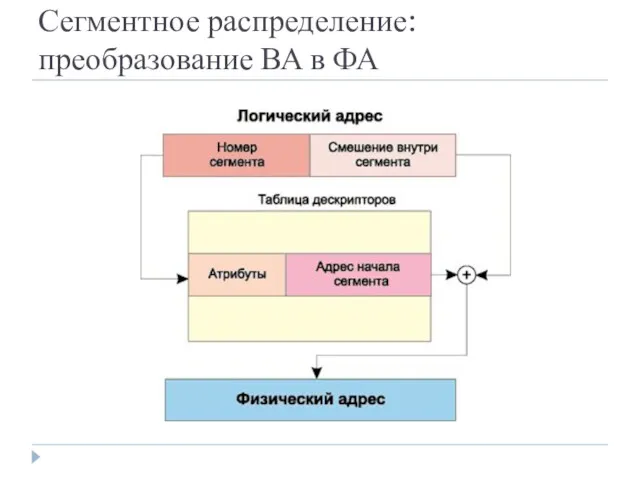

- 52. Сегментное распределение: преобразование ВА в ФА Система с сегментной организацией функционирует аналогично системе со страничной организацией:

- 53. Трансляции адреса в сегментной системе (1) При активизации очередного процесса в специальный регистр процессора загружается адрес

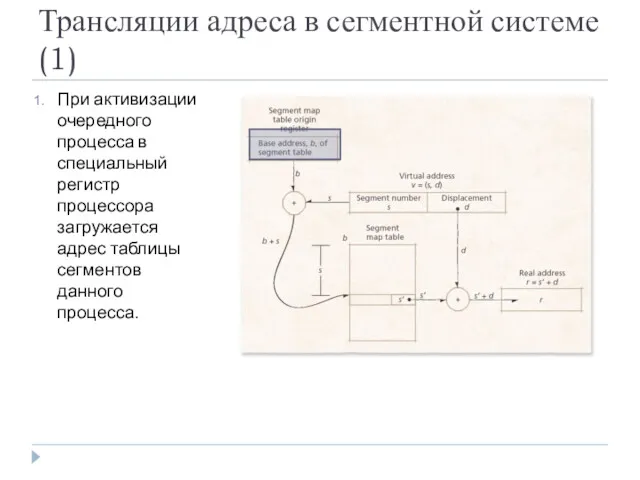

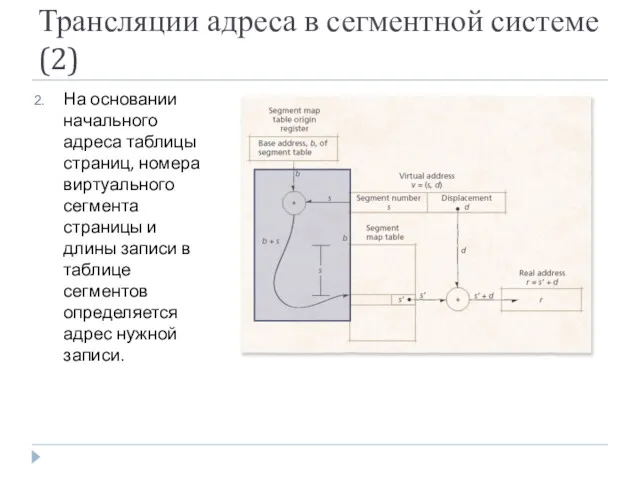

- 54. Трансляции адреса в сегментной системе (2) На основании начального адреса таблицы страниц, номера виртуального сегмента страницы

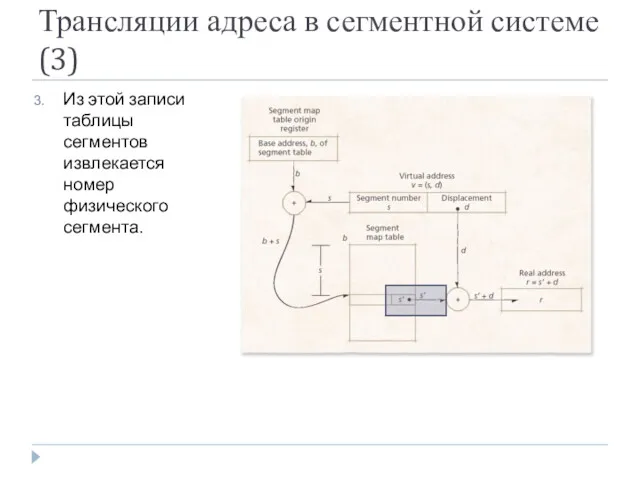

- 55. Трансляции адреса в сегментной системе (3) Из этой записи таблицы сегментов извлекается номер физического сегмента.

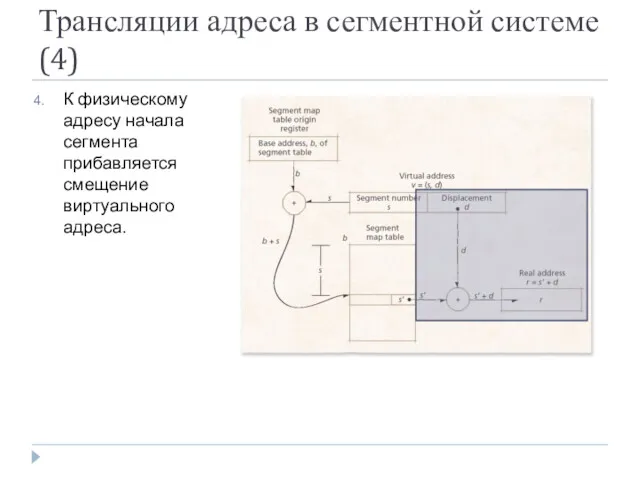

- 56. Трансляции адреса в сегментной системе (4) К физическому адресу начала сегмента прибавляется смещение виртуального адреса.

- 57. Сегментное распределение: преобразование ВА в ФА

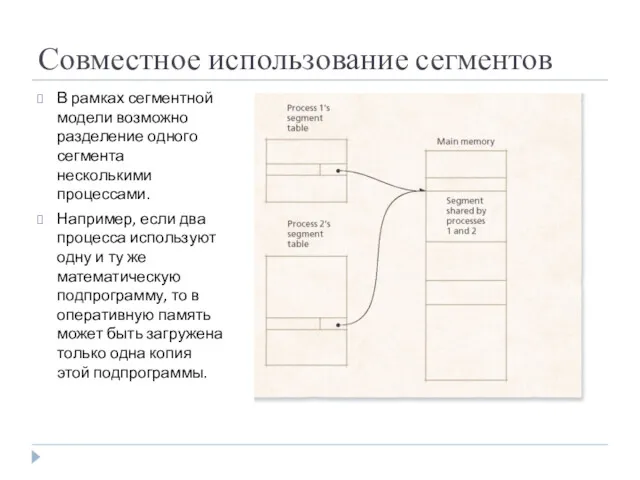

- 58. Совместное использование сегментов В рамках сегментной модели возможно разделение одного сегмента несколькими процессами. Например, если два

- 59. Достоинства и недостатки сегментного распределения Более эффективное использование физической (оперативной) памяти. Потенциально меньшее количество прерываний по

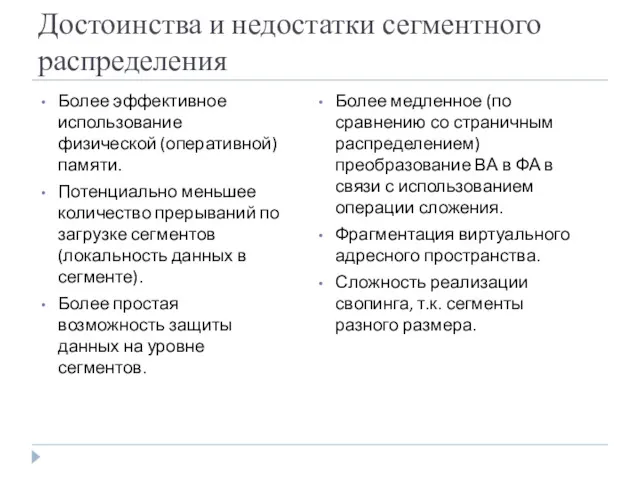

- 60. Задание Сравните страничное и сегментное преобразования для 16-битной системы.

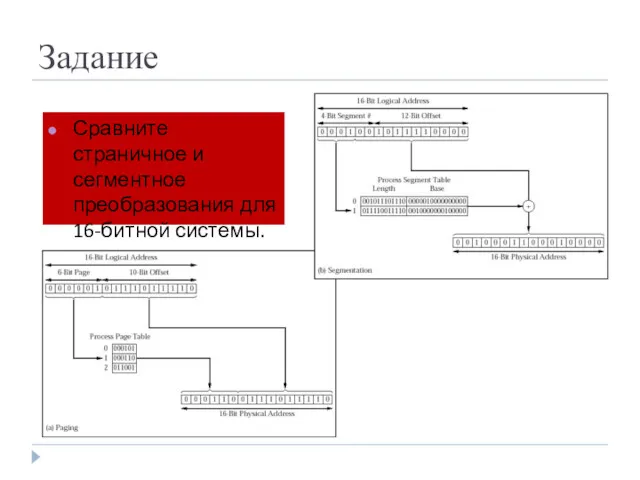

- 61. Методы распределения памяти с использованием дискового пространства Сегментно-страничное распределение

- 62. Сегментно-страничное распределение Данный метод представляет собой комбинацию страничного и сегментного распределения памяти и, вследствие этого, сочетает

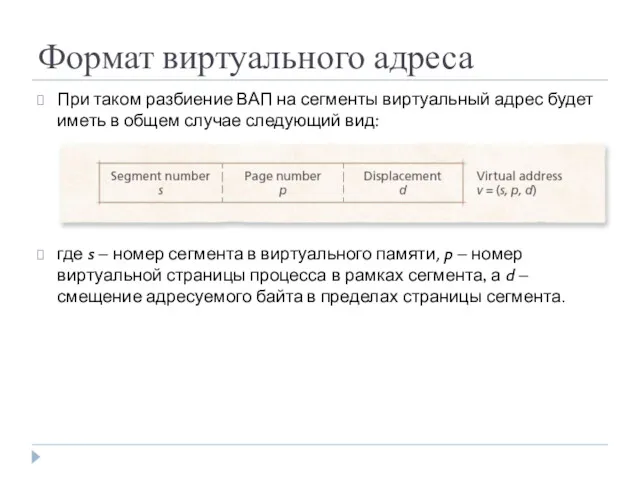

- 63. Формат виртуального адреса При таком разбиение ВАП на сегменты виртуальный адрес будет иметь в общем случае

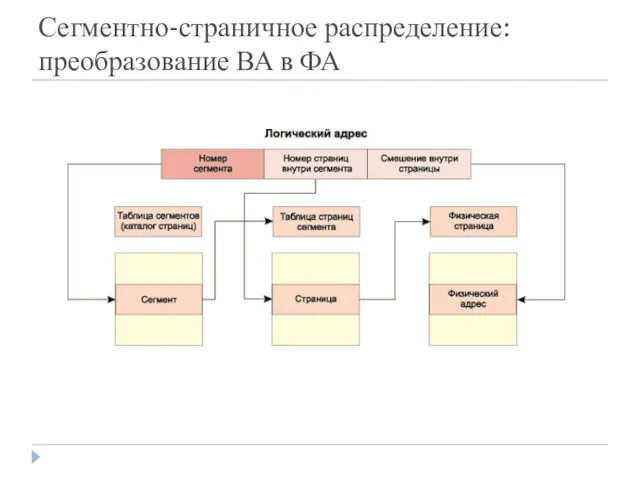

- 64. Таблицы сегментов и страниц Для каждого процесса создается таблица сегментов, в которой указываются адреса таблиц страниц

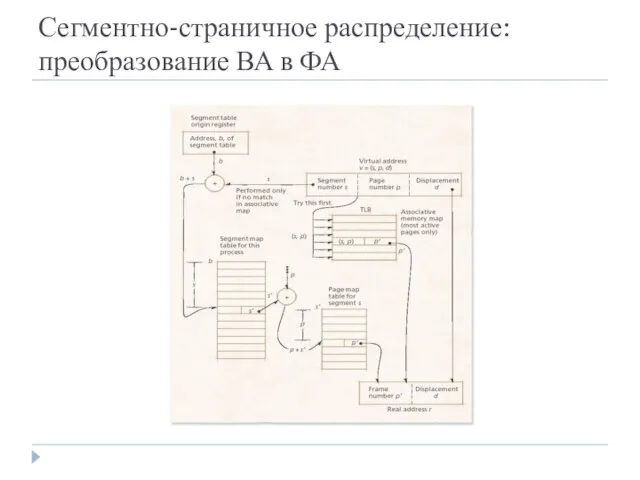

- 65. Сегментно-страничное распределение: преобразование ВА в ФА

- 66. Сегментно-страничное распределение: преобразование ВА в ФА

- 67. Достоинства сегментно-страничного распределения Сегментно-страничная виртуальная память сочетает достоинства обоих предыдущих подходов: быстрое преобразование виртуальных адресов в

- 69. Скачать презентацию

Построение диаграмм и графиков в электронных таблицах

Построение диаграмм и графиков в электронных таблицах Знакомство с Word

Знакомство с Word Знаковые системы. Кодирование информации

Знаковые системы. Кодирование информации SAFA results: Operators Russian Federation

SAFA results: Operators Russian Federation Microsoft Word мәтінді құру және редакциялау

Microsoft Word мәтінді құру және редакциялау Приложение ВК

Приложение ВК Создание оригинал-макета визиток

Создание оригинал-макета визиток История становления и развития теории систем

История становления и развития теории систем Создание презентации в программе PowerPoint

Создание презентации в программе PowerPoint Операторы. Перегрузка операторов (лекция 5)

Операторы. Перегрузка операторов (лекция 5) Лабораторные занятия. Особенности лабораторной работы по информатике

Лабораторные занятия. Особенности лабораторной работы по информатике Кодирование информации

Кодирование информации Инсталляция и деинсталляция программного обеспечения

Инсталляция и деинсталляция программного обеспечения Тип даних множина

Тип даних множина Измерение информации. Единицы измерения информации

Измерение информации. Единицы измерения информации Логические основы компьютера

Логические основы компьютера Системный администратор. Примеры использования команды PING

Системный администратор. Примеры использования команды PING Архивы пользователя

Архивы пользователя Задача потребительского выбора. Задачи нелинейного программирования

Задача потребительского выбора. Задачи нелинейного программирования Code validation

Code validation Сравнительный анализ дизайна сайтов

Сравнительный анализ дизайна сайтов Протокол IPv4

Протокол IPv4 Электронная почта. История создания

Электронная почта. История создания Популярность Mова игр на примере Dota 2

Популярность Mова игр на примере Dota 2 The Essence of C++ with examples in C++84, C++98, C++11, and C++14

The Essence of C++ with examples in C++84, C++98, C++11, and C++14 Microsoft word-бұл құжаттарды құру, қарап шығу, өзгерту және басып шығару үшін арналған Microsoft Office

Microsoft word-бұл құжаттарды құру, қарап шығу, өзгерту және басып шығару үшін арналған Microsoft Office Компьютерные вирусы и защита от них

Компьютерные вирусы и защита от них Теории медиаобразования

Теории медиаобразования