Содержание

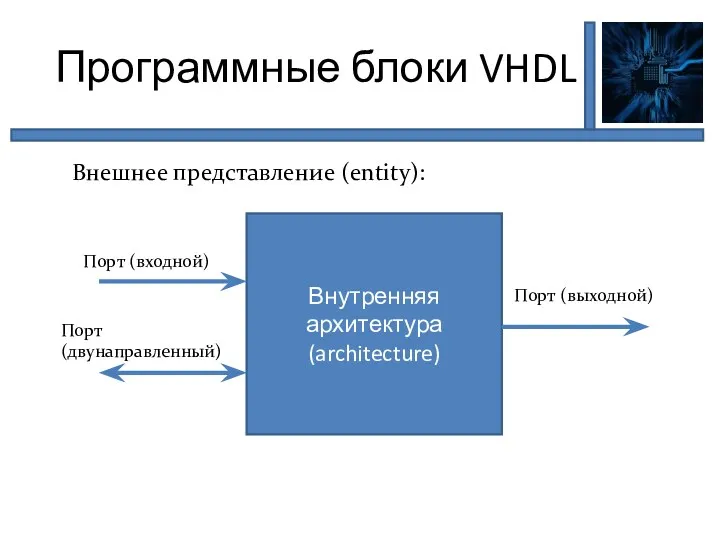

- 2. Программные блоки VHDL Внутренняя архитектура (architecture) Внешнее представление (entity): Порт (входной) Порт (двунаправленный) Порт (выходной)

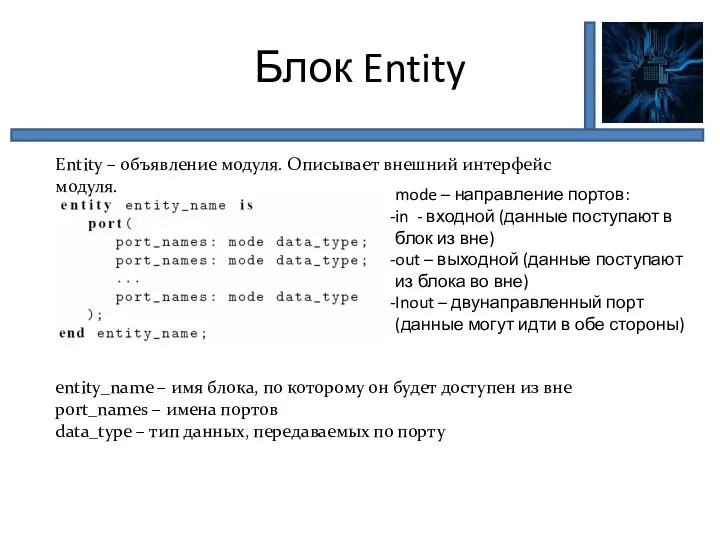

- 3. Блок Entity mode – направление портов: in - входной (данные поступают в блок из вне) out

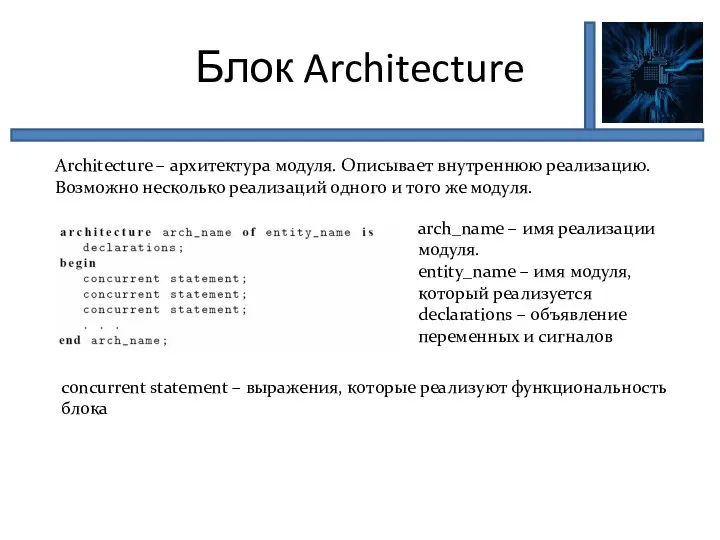

- 4. Блок Architecture Architecture – архитектура модуля. Описывает внутреннюю реализацию. Возможно несколько реализаций одного и того же

- 5. Подключение внешних библиотек и пакетов Подключение библиотеки: LIBRARY library_name; library_name – имя подключаемой библиотеки Подключение пакетов

- 6. Элементы языка VHDL Комментарии . Начинаются с -- Идентификаторы. my_signal, My_Signal – одно и тоже. Нету

- 7. Использование signal в Architecture ARCHITECTURE OF IS SIGNAL clk: bit; BEGIN Concurrent Statements END ARCHITECTURE; Структура

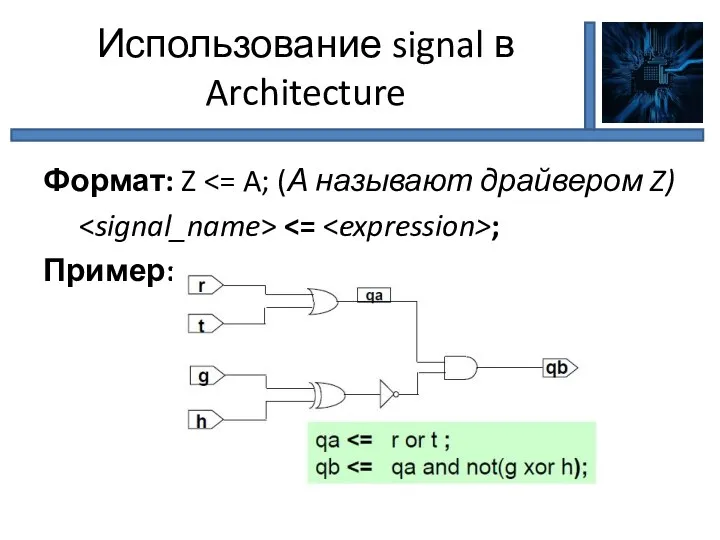

- 8. Использование signal в Architecture Формат: Z ; Пример:

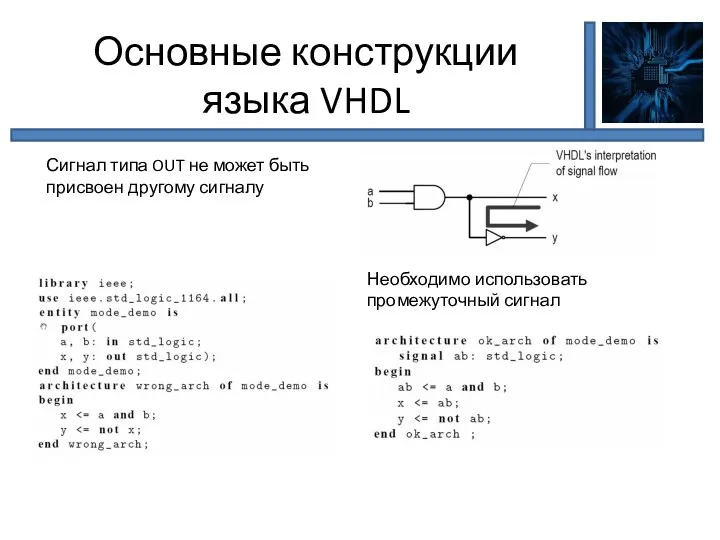

- 9. Основные конструкции языка VHDL Сигнал типа OUT не может быть присвоен другому сигналу Необходимо использовать промежуточный

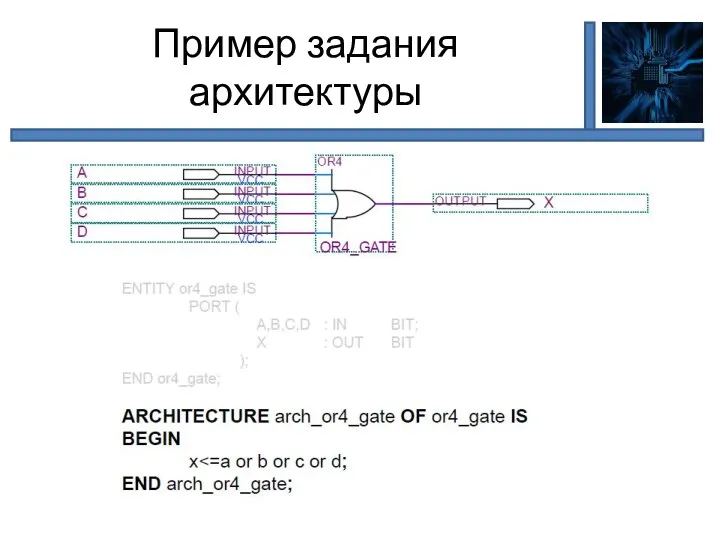

- 10. Пример задания архитектуры

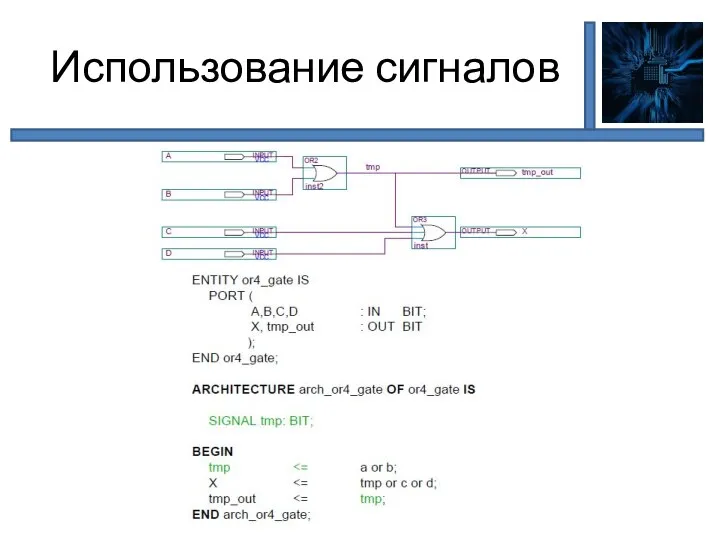

- 11. Использование сигналов

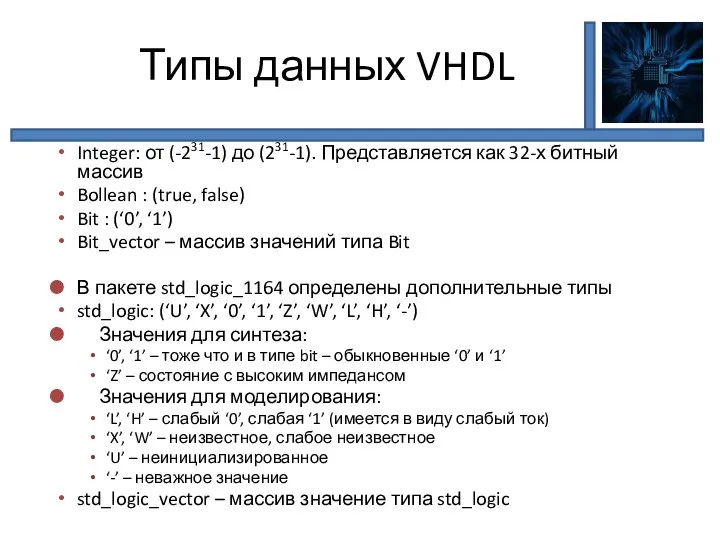

- 12. Типы данных VHDL Integer: от (-231-1) до (231-1). Представляется как 32-х битный массив Bollean : (true,

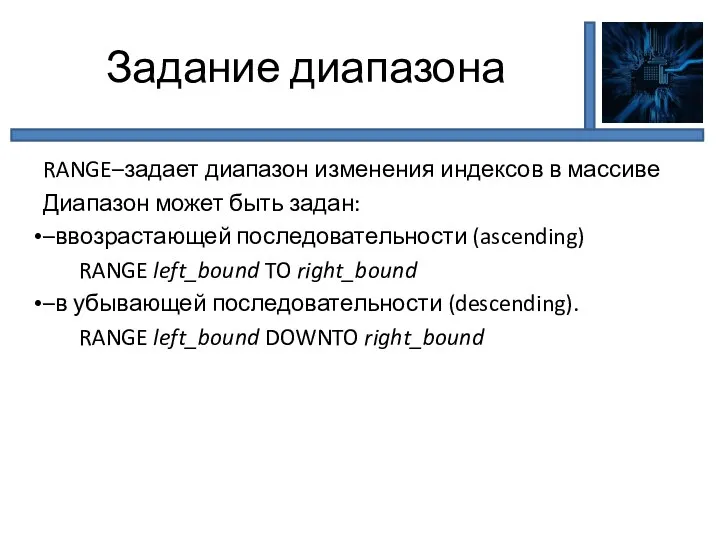

- 13. Задание диапазона RANGE–задает диапазон изменения индексов в массиве Диапазон может быть задан: –ввозрастающей последовательности (ascending) RANGE

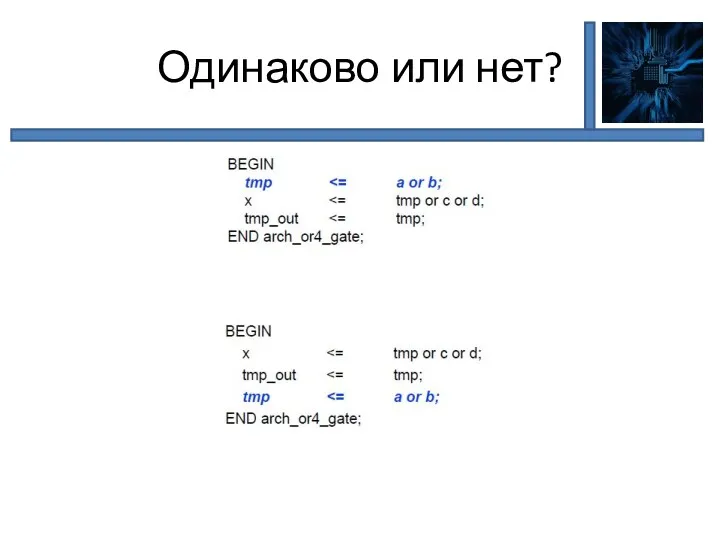

- 14. Одинаково или нет?

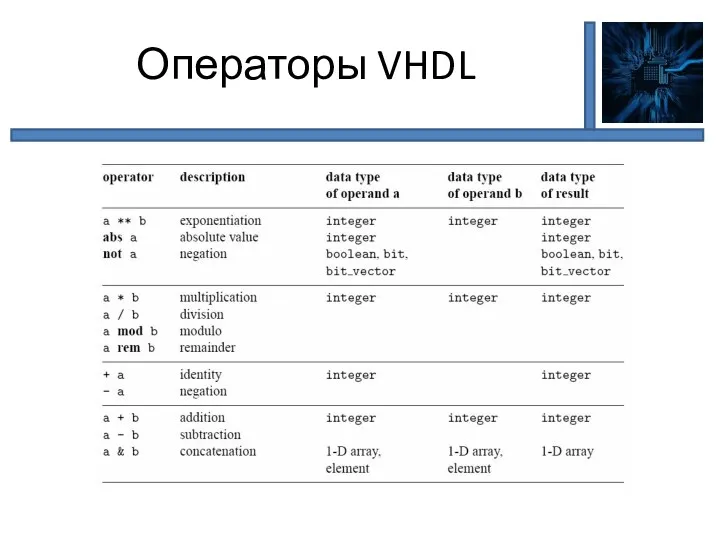

- 15. Операторы VHDL

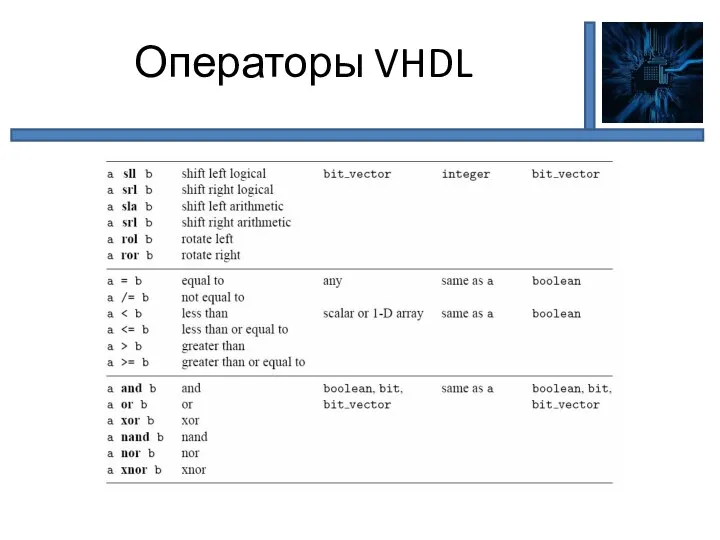

- 16. Операторы VHDL

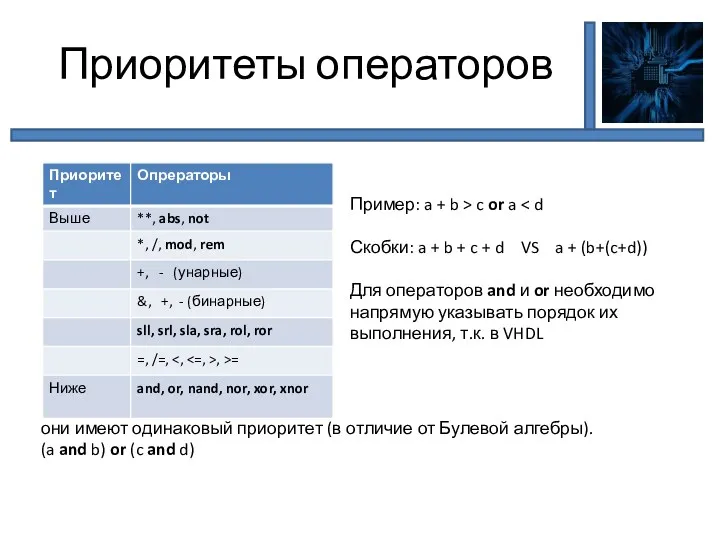

- 17. Приоритеты операторов Пример: a + b > c or a Скобки: a + b + c

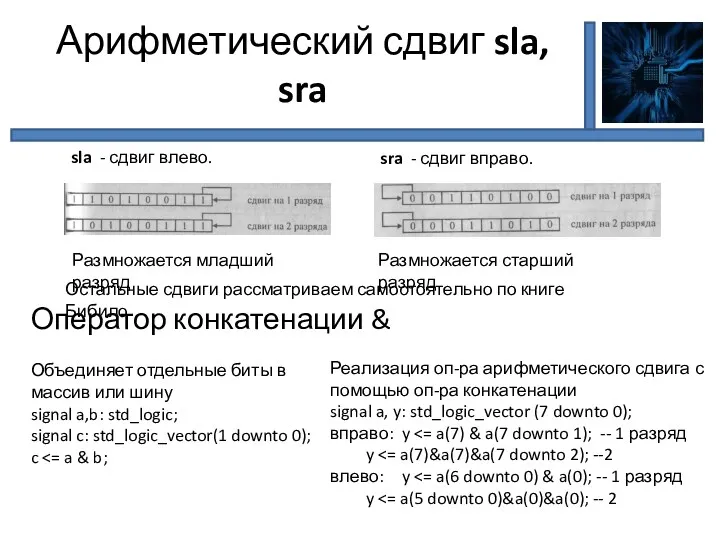

- 18. Арифметический сдвиг sla, sra sla - сдвиг влево. sra - сдвиг вправо. Размножается младший разряд Размножается

- 19. Присвоение значения массиву signal a: std_logic_vector (7 downto 0); a Позиционная привязка: a Привязка по имени:

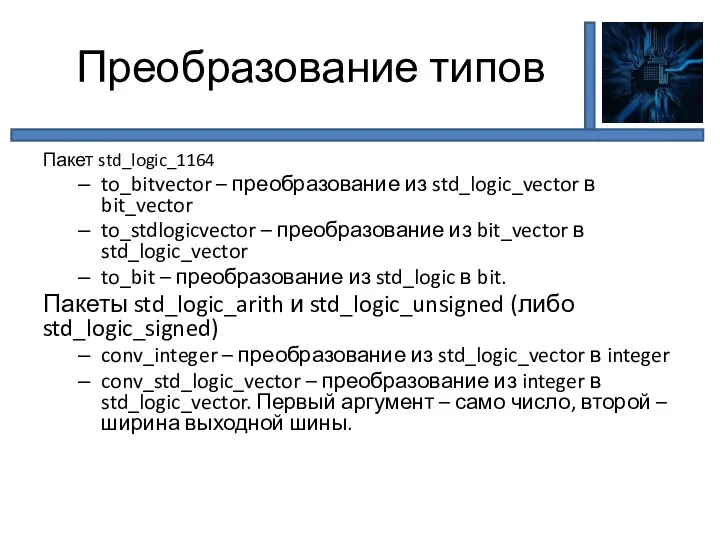

- 20. Преобразование типов Пакет std_logic_1164 to_bitvector – преобразование из std_logic_vector в bit_vector to_stdlogicvector – преобразование из bit_vector

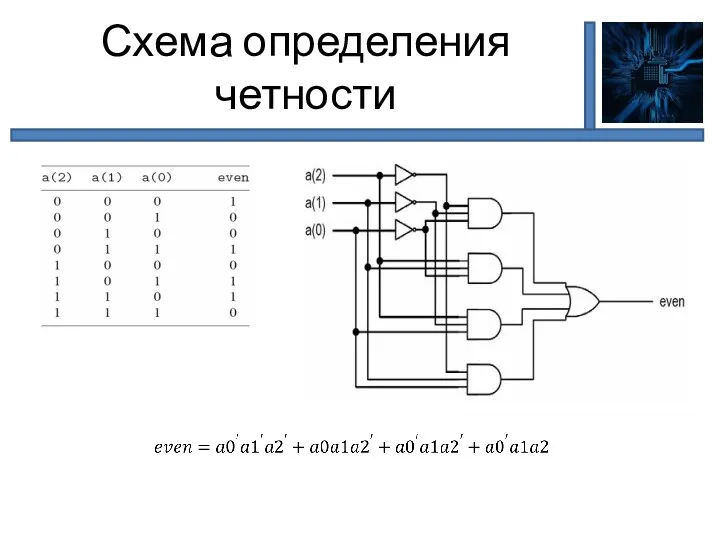

- 21. Схема определения четности

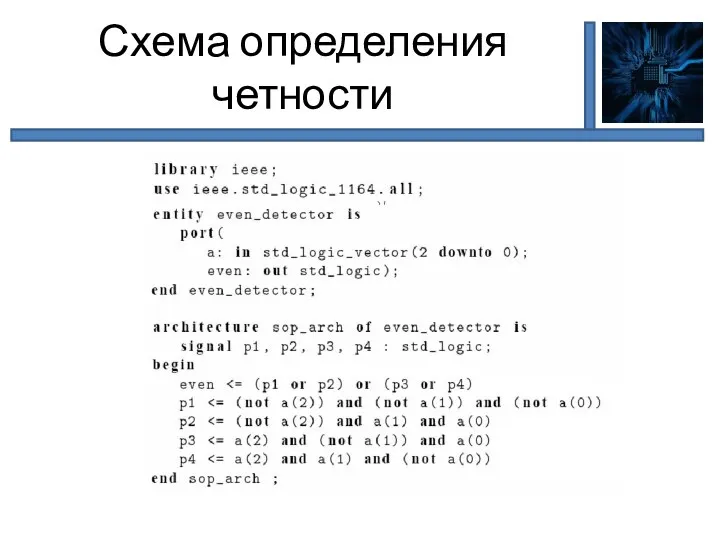

- 22. Схема определения четности

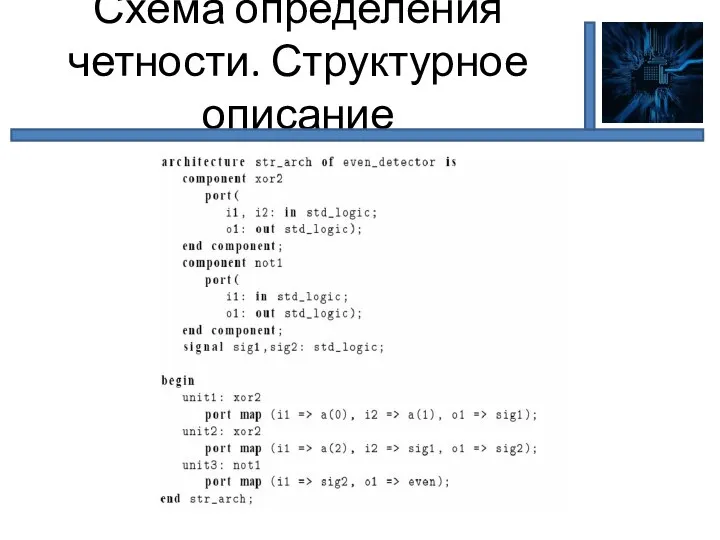

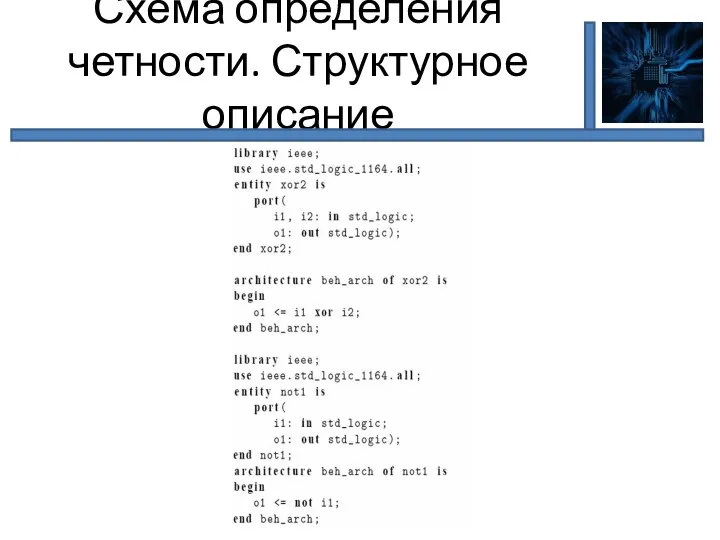

- 23. Схема определения четности. Структурное описание

- 24. Схема определения четности. Структурное описание

- 25. Схема определения четности. Структурное описание

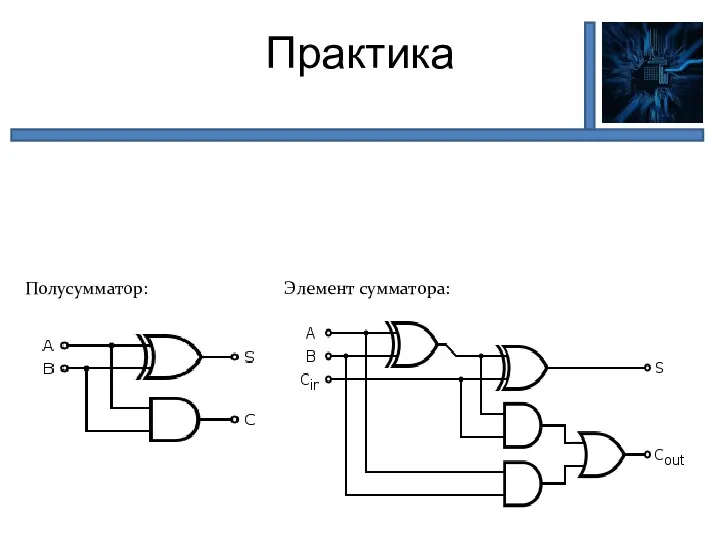

- 26. Практика Полусумматор: Элемент сумматора:

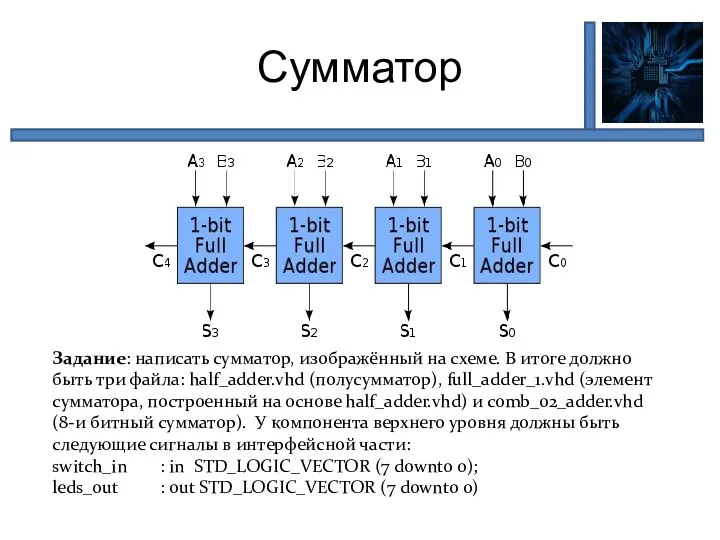

- 27. Сумматор Задание: написать сумматор, изображённый на схеме. В итоге должно быть три файла: half_adder.vhd (полусумматор), full_adder_1.vhd

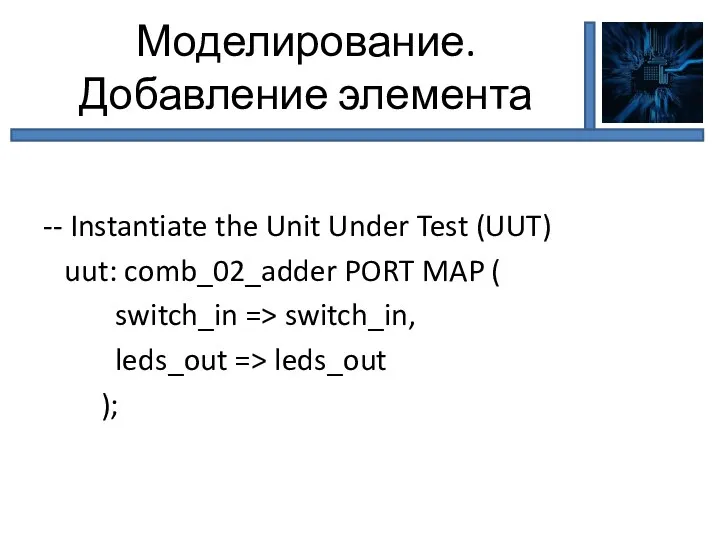

- 28. Моделирование. Добавление элемента -- Instantiate the Unit Under Test (UUT) uut: comb_02_adder PORT MAP ( switch_in

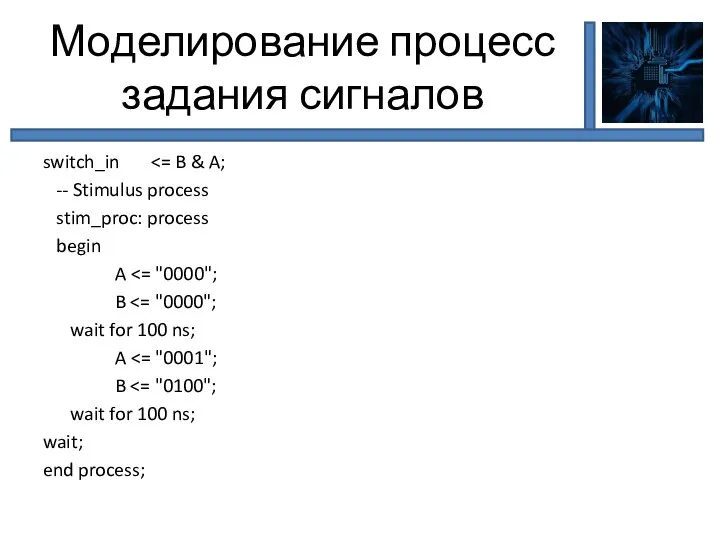

- 29. Моделирование процесс задания сигналов switch_in -- Stimulus process stim_proc: process begin A B wait for 100

- 30. Моделирование Задание: написать testbench (adder_1_tb.vhd) для 8-ми битного сумматора

- 31. Реализация сумматора на плате Atlys Создайте проект для реализации сумматора: входы к переключателям, а выходы –

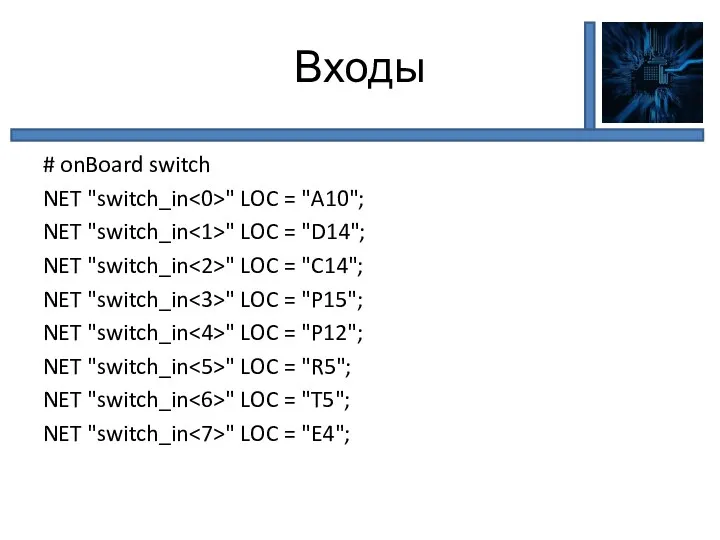

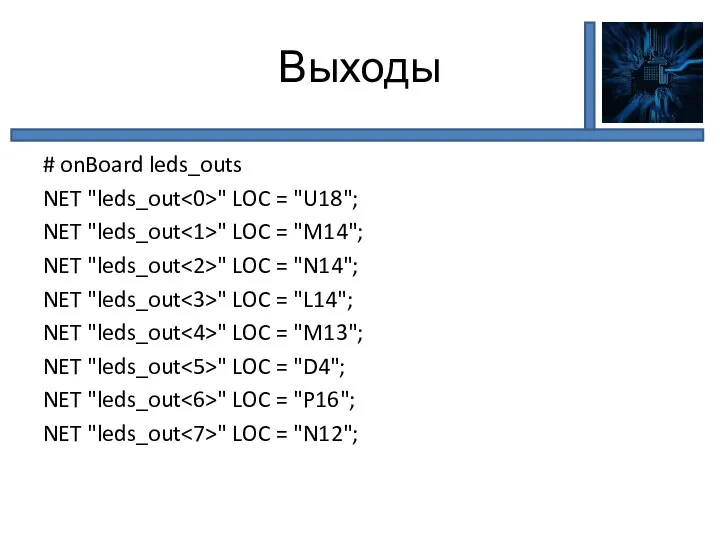

- 32. Входы # onBoard switch NET "switch_in " LOC = "A10"; NET "switch_in " LOC = "D14";

- 33. Выходы # onBoard leds_outs NET "leds_out " LOC = "U18"; NET "leds_out " LOC = "M14";

- 35. Скачать презентацию

20231112_uroki_bezopasnosti_v_seti

20231112_uroki_bezopasnosti_v_seti Краткая история семейства UNIX. Занятие 01

Краткая история семейства UNIX. Занятие 01 класс. 04.02.22

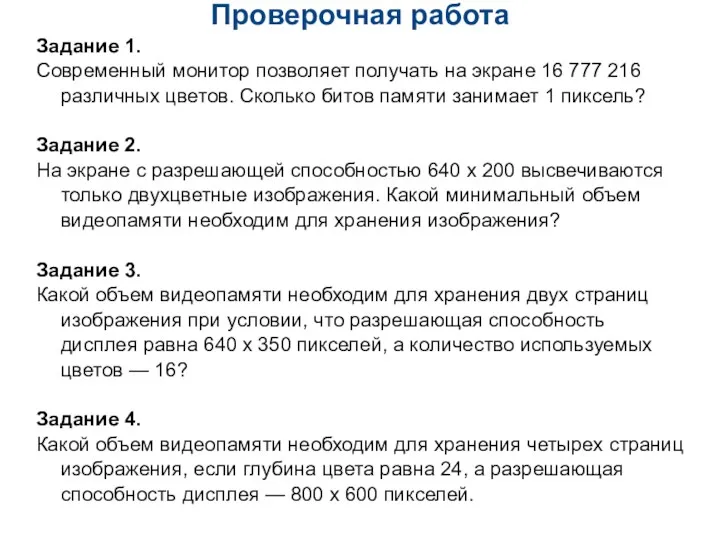

класс. 04.02.22 Проверочная работа для 9 класса по теме Кодирование графической информации

Проверочная работа для 9 класса по теме Кодирование графической информации Історія розвитку обчислювальної техніки. Характеристика різних поколінь ЕОМ. Основні галузі застосування комп'ютерів

Історія розвитку обчислювальної техніки. Характеристика різних поколінь ЕОМ. Основні галузі застосування комп'ютерів Создание сайта. Пошаговая инструкция

Создание сайта. Пошаговая инструкция Ветвления. Программирование на языке Python

Ветвления. Программирование на языке Python Информатизация в архивном деле

Информатизация в архивном деле Передача пакетных данных в сетях 2G/3G

Передача пакетных данных в сетях 2G/3G Антивирусные программы

Антивирусные программы Коммуникативная природа информационного общества

Коммуникативная природа информационного общества Сети передачи данных

Сети передачи данных Физическая защита данных на дисках. Защита от вредоносных программ

Физическая защита данных на дисках. Защита от вредоносных программ Программы статистической обработки данных

Программы статистической обработки данных Теоретико-системные основы математического моделирования

Теоретико-системные основы математического моделирования Модульно-рейтинговая технология обучения базовому курсу информатики

Модульно-рейтинговая технология обучения базовому курсу информатики Razdel_6_Ponyatie_resursa_v_OS

Razdel_6_Ponyatie_resursa_v_OS Графические возможности языка Visual Basic

Графические возможности языка Visual Basic Программные сети

Программные сети Урок-презентация по теме Условия выбора и сложные логические выражения к учебнику Информатика и ИКТ: 9 класс/Семакин И.Г. и др

Урок-презентация по теме Условия выбора и сложные логические выражения к учебнику Информатика и ИКТ: 9 класс/Семакин И.Г. и др Знакомство с графическим редактором Adobe Fhotoshop

Знакомство с графическим редактором Adobe Fhotoshop Протоколы и стандарты компьютерных сетей

Протоколы и стандарты компьютерных сетей CAD/CAM services

CAD/CAM services Электронный листок нетрудоспособности на территории Ленинградской области

Электронный листок нетрудоспособности на территории Ленинградской области Архиваторы. Сжатие данных

Архиваторы. Сжатие данных Подходы к измерению информации

Подходы к измерению информации Программирование циклов

Программирование циклов Системы автоматизированного проектирования в электроэнергетике (общие сведения)

Системы автоматизированного проектирования в электроэнергетике (общие сведения)