Содержание

- 2. Архитектура ЭВМ Джон фон Нейман Архитектура ЭВМ Вычислительные и логические возможности Аппаратные средства Программное обеспечение Система

- 3. Принципы фон Неймана Использование двоичной системы счисления в вычислительных машинах Программное управление ЭВМ. Память компьютера используется

- 4. Структура архитектуры ЭВМ Так работала машина фон Неймана…

- 5. Классификация Флинна Майкл Флинн

- 6. Представители классификации SISD CRAY-1 SIMD Intel ParagonMIMD

- 7. Классификация Фенга n – число бит в машинном слове, обрабатываемых параллельно при выполнении машинных инструкций. m

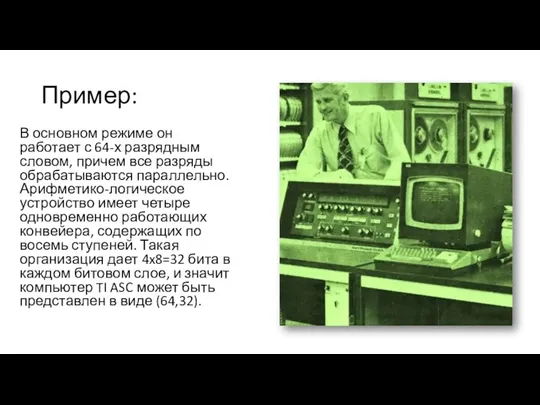

- 8. Пример: В основном режиме он работает с 64-х разрядным словом, причем все разряды обрабатываются параллельно. Арифметико-логическое

- 9. Классы по Фенгу Разрядно-последовательные пословно-последовательные (n=m=1). Разрядно-параллельные пословно-последовательные (n > 1 , m = 1). Разрядно-последовательные

- 11. Скачать презентацию

Обработка детали по управляющей программе

Обработка детали по управляющей программе викторина

викторина Лучевая диагностика в нефрологии и урологии

Лучевая диагностика в нефрологии и урологии Momente

Momente Особенности развития ребенка с нарушением интеллекта в раннем возрасте

Особенности развития ребенка с нарушением интеллекта в раннем возрасте Труд людей весной. 1 класс

Труд людей весной. 1 класс Вести со всей планеты

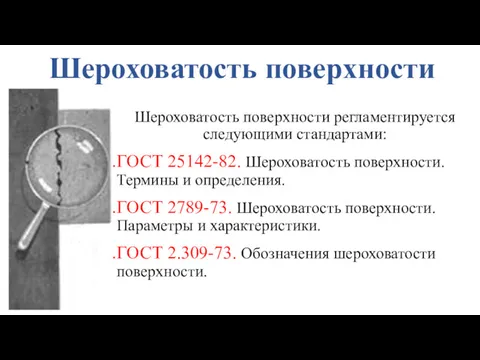

Вести со всей планеты Шероховатость поверхности

Шероховатость поверхности Аутоиммунные энцефалиты

Аутоиммунные энцефалиты Царство бактерии

Царство бактерии Как родилась книга.

Как родилась книга. Классный час с презентацией на тему Олимпиада 2014

Классный час с презентацией на тему Олимпиада 2014 Основы журналистики

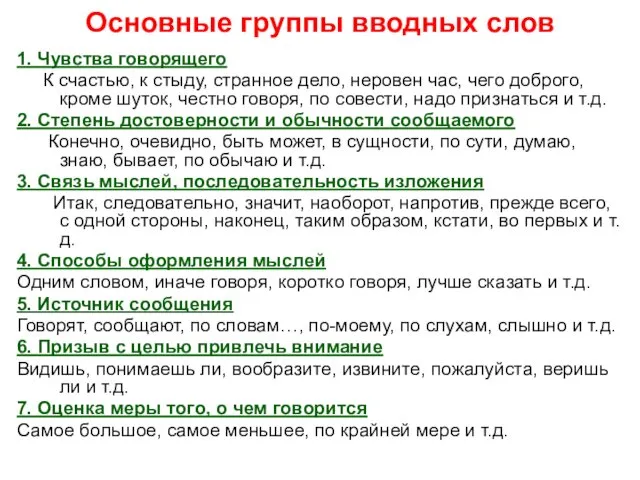

Основы журналистики Основные группы вводных слов

Основные группы вводных слов Холодильники

Холодильники Принцип работы цифрового фотоаппарата

Принцип работы цифрового фотоаппарата Дополнительный_материал_11.45_15.02.2024_118afd64

Дополнительный_материал_11.45_15.02.2024_118afd64 ЛОЛ Веснушки при МБОУ Весеннинской ООШ – участники Всероссийской акции Внимание, дети!.

ЛОЛ Веснушки при МБОУ Весеннинской ООШ – участники Всероссийской акции Внимание, дети!. Каковы причины Первой мировой войны?

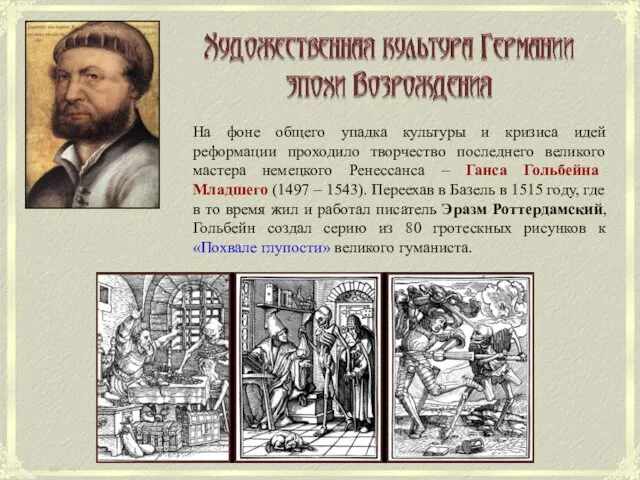

Каковы причины Первой мировой войны? Ганс Гольбейн Младший

Ганс Гольбейн Младший Газонефтеводопроявление (ГНВП)

Газонефтеводопроявление (ГНВП) Питание и режим рек.

Питание и режим рек. 9_Презентация задание вода

9_Презентация задание вода - 4 ЛЕКЦИИ-Функции и методы менеджмента

- 4 ЛЕКЦИИ-Функции и методы менеджмента Tense Simple (Indefinite) (Простое), Progressive (Continuous) (Продолженное)

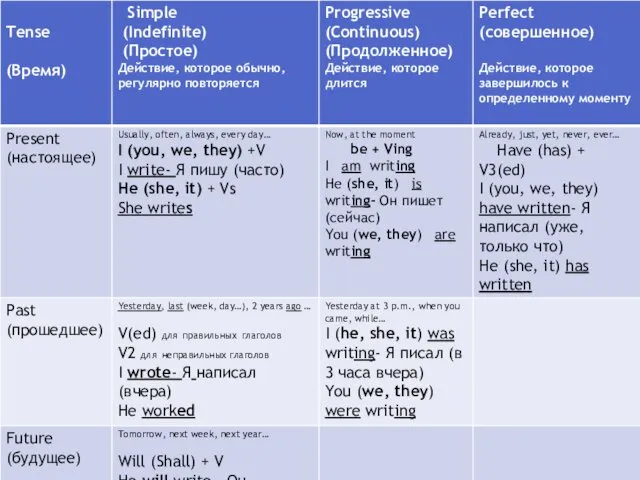

Tense Simple (Indefinite) (Простое), Progressive (Continuous) (Продолженное) Диггерство. Понятие диггерство

Диггерство. Понятие диггерство Метапредметные результаты освоения ООП

Метапредметные результаты освоения ООП Описание опыта работы по теме: Развитие познавательной активности учащихся на уроках химии

Описание опыта работы по теме: Развитие познавательной активности учащихся на уроках химии