Содержание

- 2. Мобильный телефон GSM

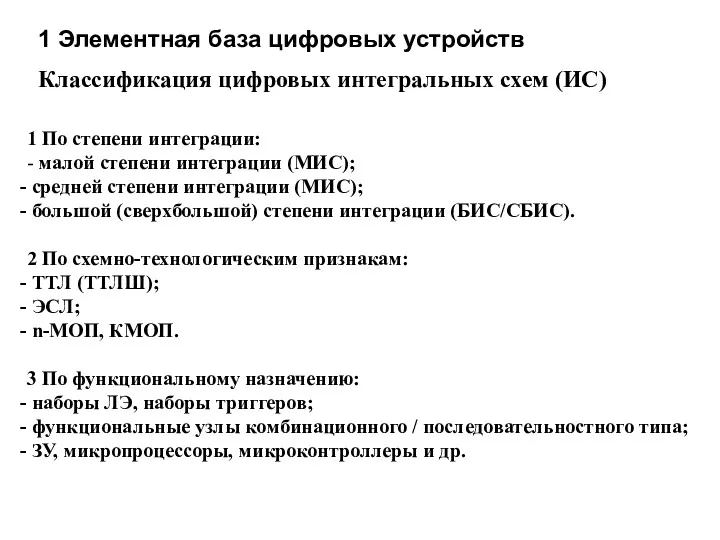

- 3. 1 По степени интеграции: - малой степени интеграции (МИС); средней степени интеграции (МИC); большой (сверхбольшой) степени

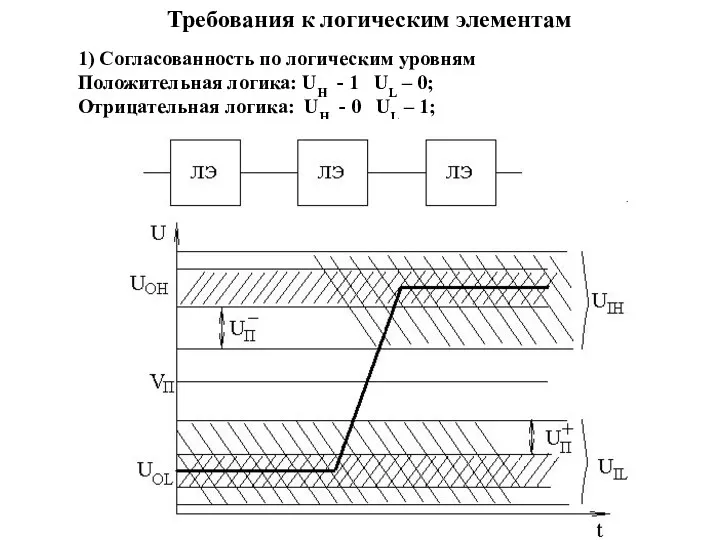

- 4. Требования к логическим элементам 1) Согласованность по логическим уровням Положительная логика: UH - 1 UL –

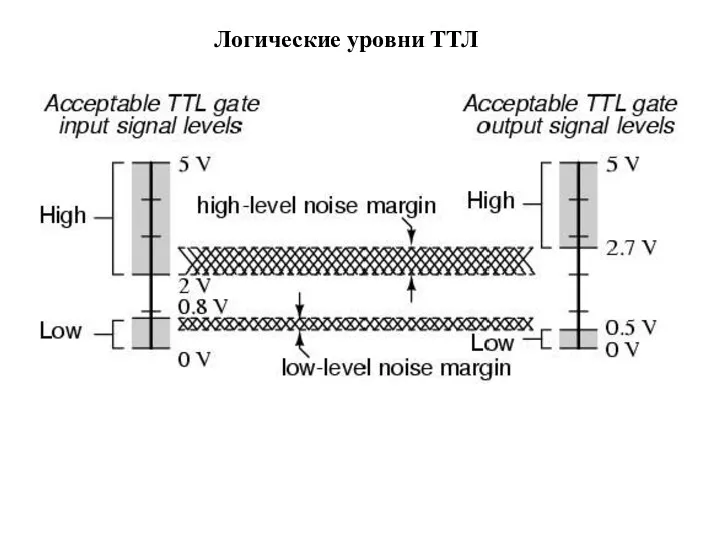

- 5. Логические уровни ТТЛ

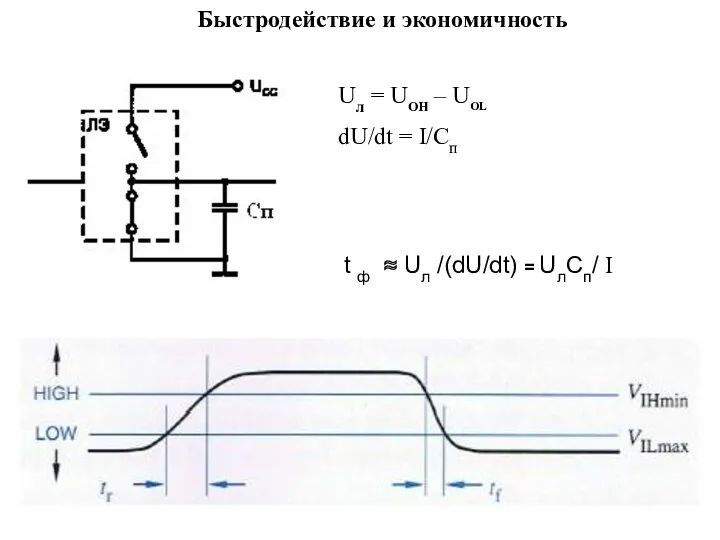

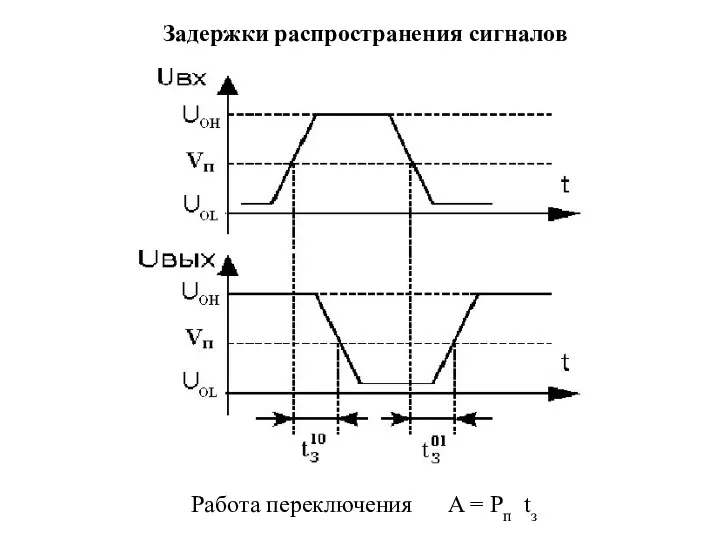

- 6. Быстродействие и экономичность Uл = UOH – UOL dU/dt = I/Cп t ф ≈ Uл /(dU/dt)

- 7. Работа переключения A = Pп tз Задержки распространения сигналов

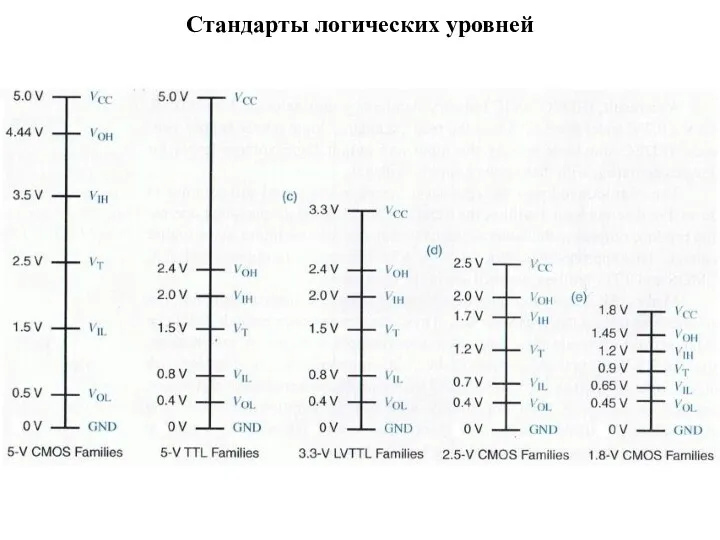

- 8. Стандарты логических уровней

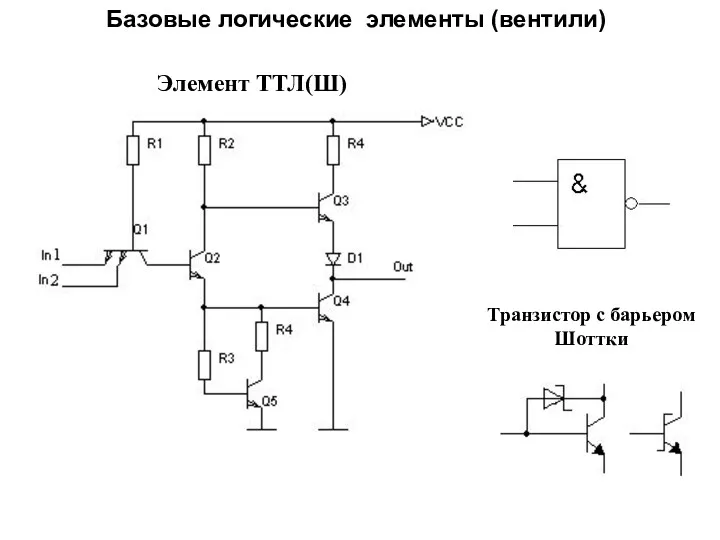

- 9. Элемент ТТЛ(Ш) Транзистор с барьером Шоттки Базовые логические элементы (вентили)

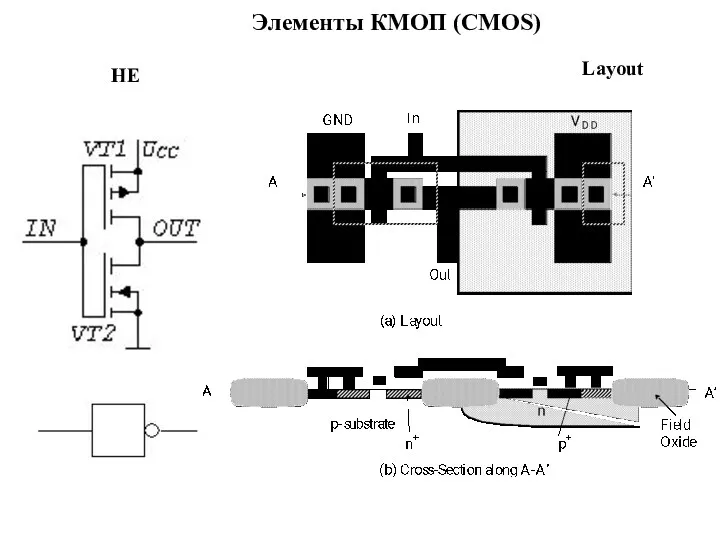

- 10. Элементы КМОП (CMOS) НЕ Layout

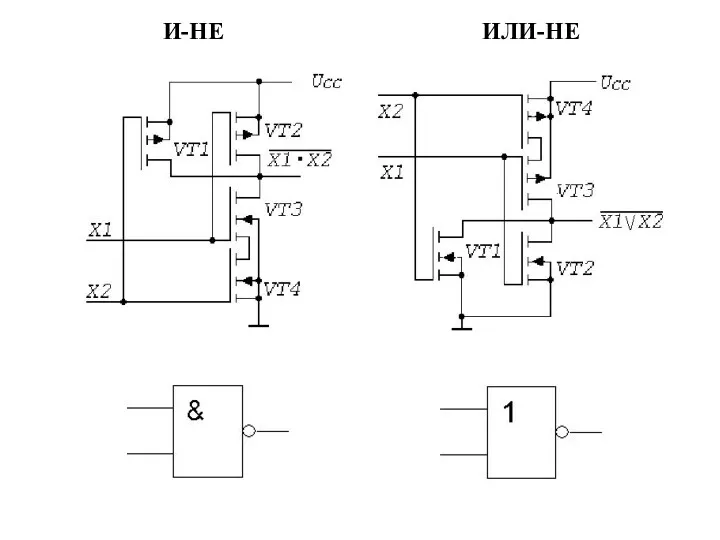

- 11. И-НЕ ИЛИ-НЕ

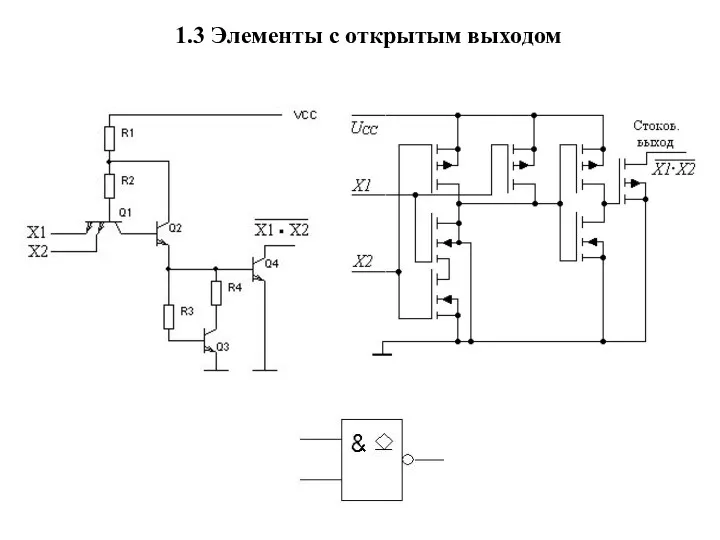

- 12. 1.3 Элементы с открытым выходом

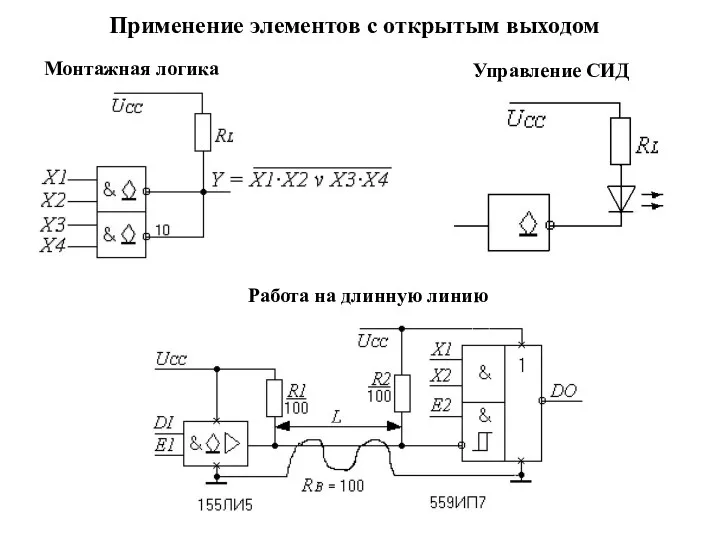

- 13. Применение элементов с открытым выходом Монтажная логика Работа на длинную линию Управление СИД

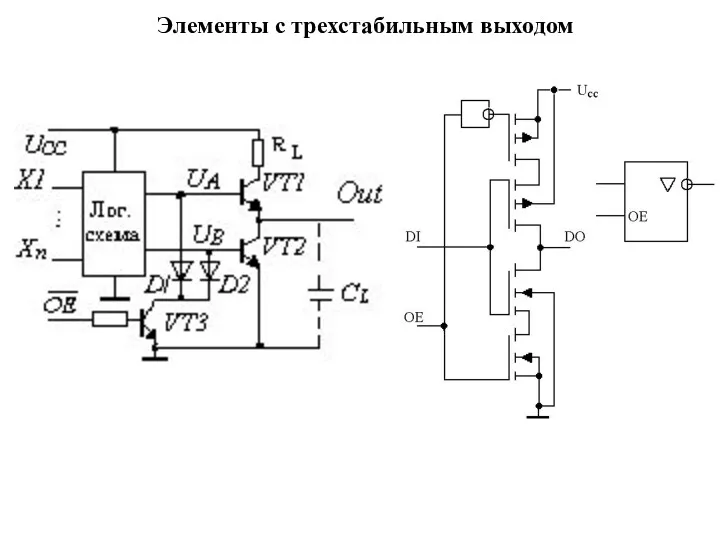

- 14. Элементы с трехстабильным выходом

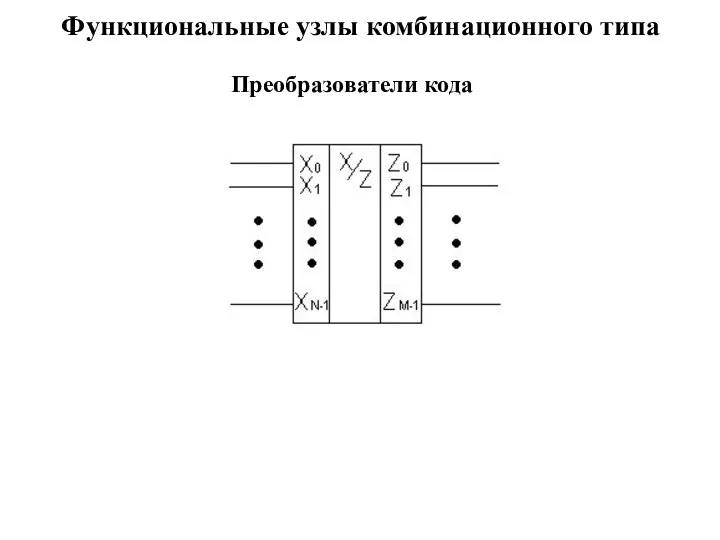

- 15. Функциональные узлы комбинационного типа Преобразователи кода

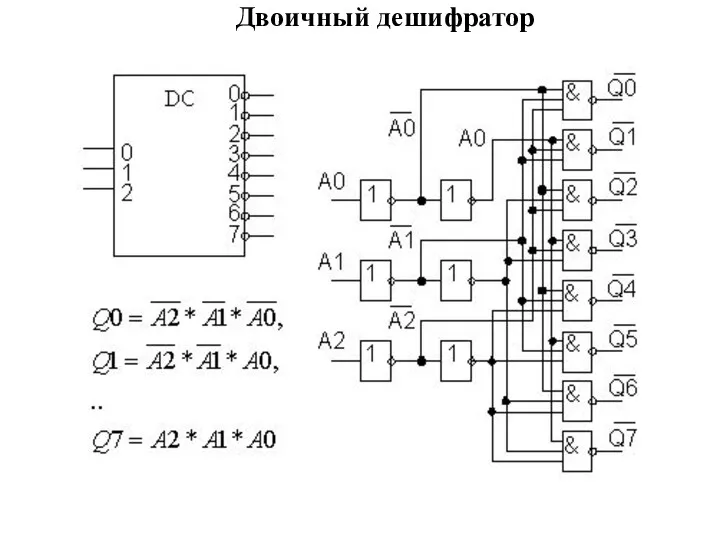

- 16. Двоичный дешифратор

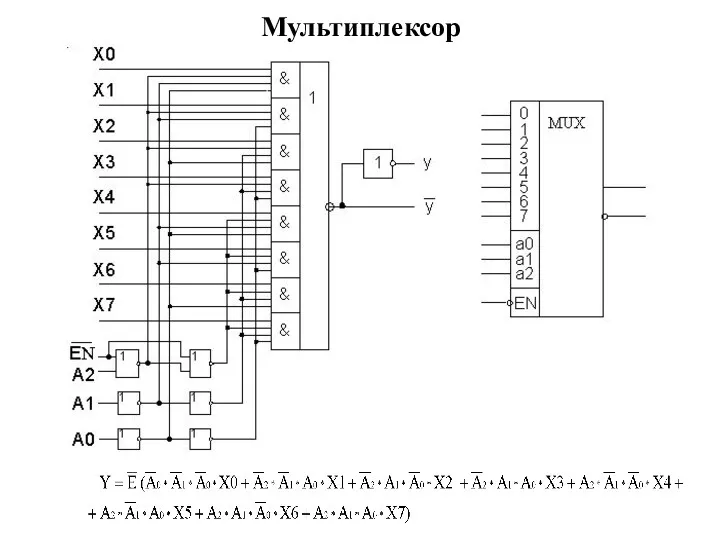

- 17. Мультиплексор

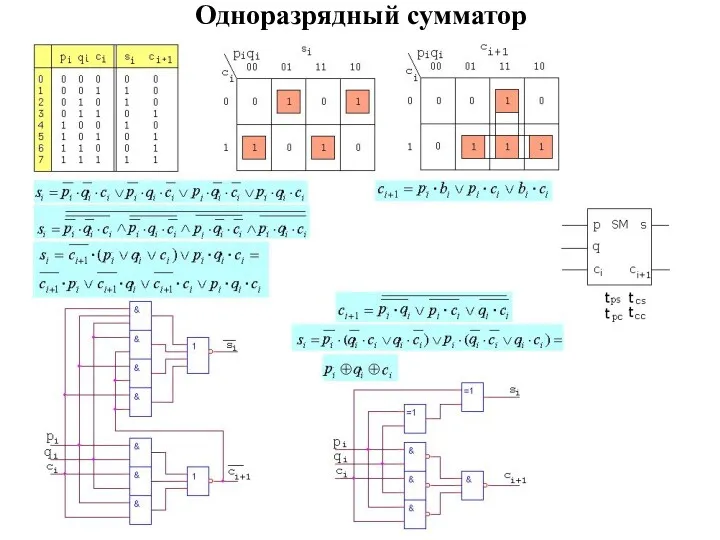

- 18. Одноразрядный сумматор

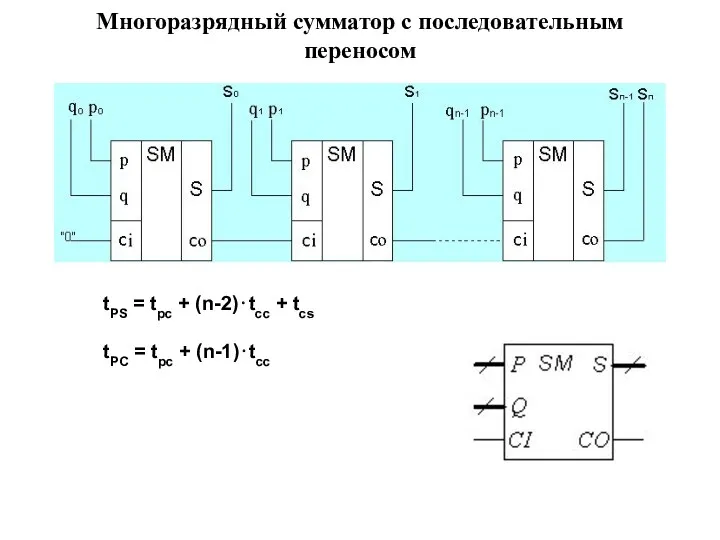

- 19. Многоразрядный сумматор с последовательным переносом tPS = tpc + (n-2)⋅tcc + tcs tPC = tpc +

- 20. Арифметико-логические устройства (АЛУ) Входы Выходы Операция M FSel1 FSel0 F[3..0] Clear 0 0 0 L Q

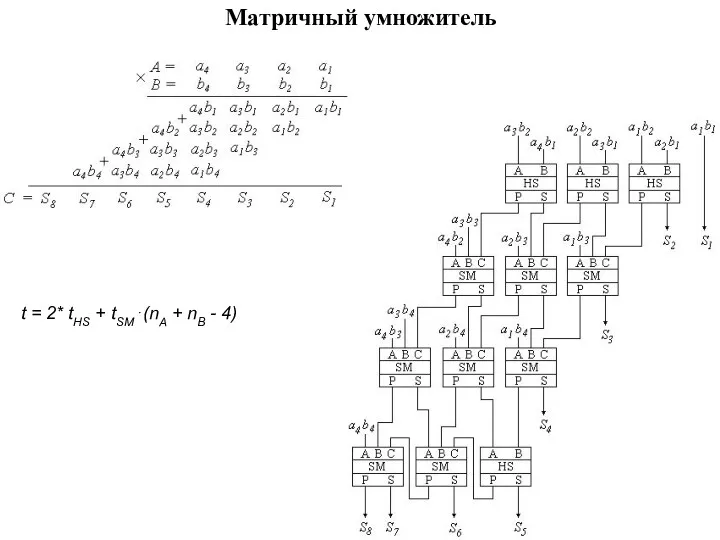

- 21. Матричный умножитель t = 2* tHS + tSM⋅(nA + nB - 4)

- 22. Раздел 4: Цифровые узлы последовательностного типа Лекция 5. Вопросы: 1 Функциональные узлы последовательностного типа. 2 Интегральные

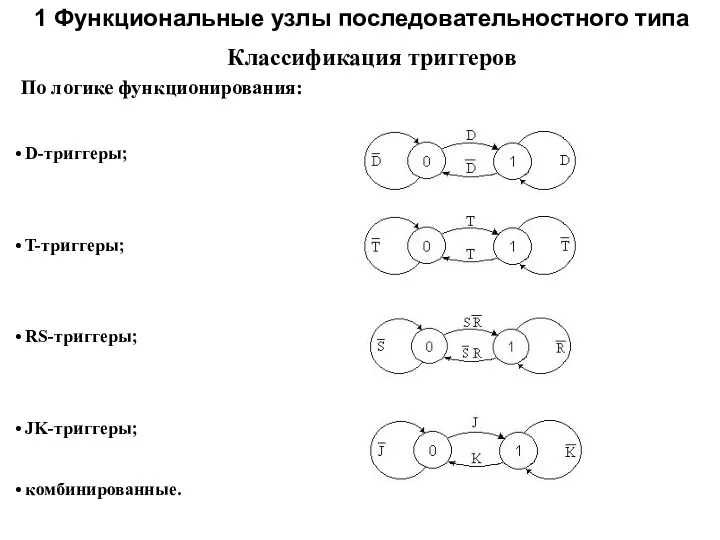

- 23. Классификация триггеров По логике функционирования: D-триггеры; T-триггеры; RS-триггеры; JK-триггеры; комбинированные. 1 Функциональные узлы последовательностного типа

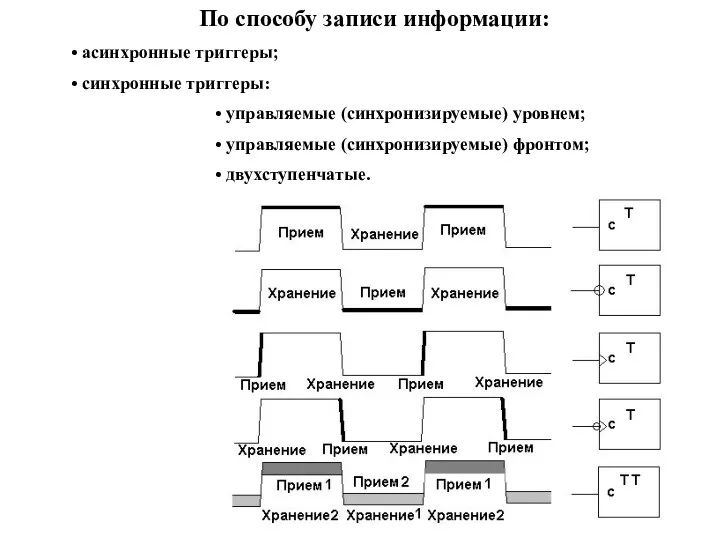

- 24. По способу записи информации: асинхронные триггеры; синхронные триггеры: управляемые (синхронизируемые) уровнем; управляемые (синхронизируемые) фронтом; двухступенчатые.

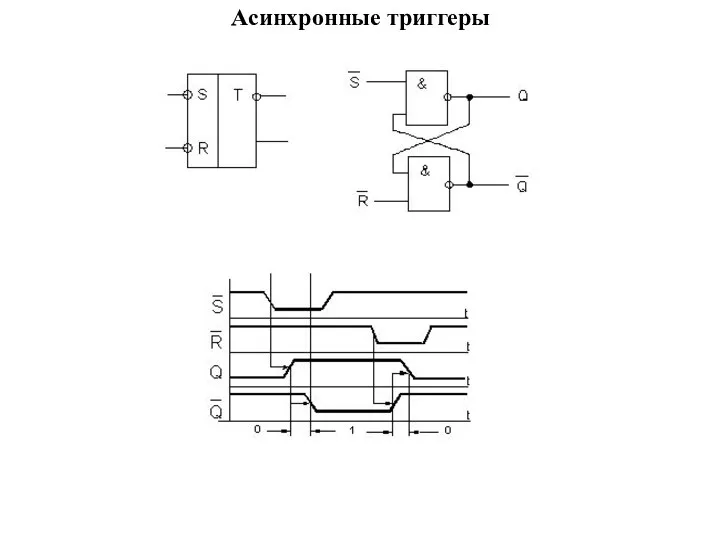

- 25. Асинхронные триггеры

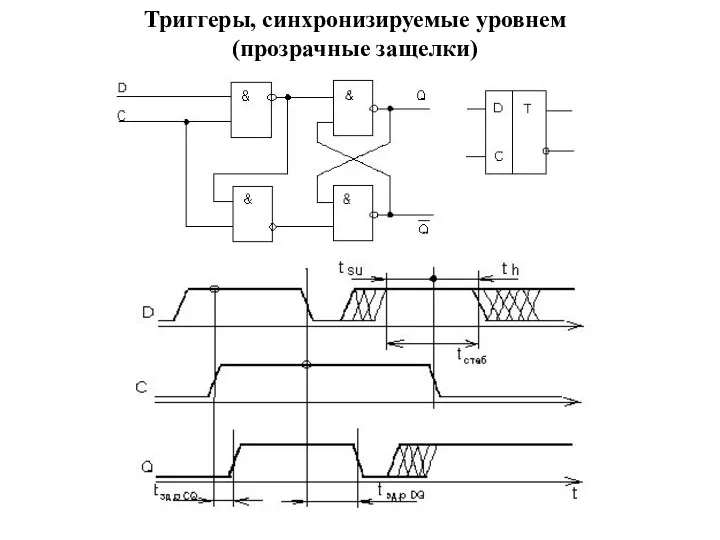

- 26. Триггеры, синхронизируемые уровнем (прозрачные защелки)

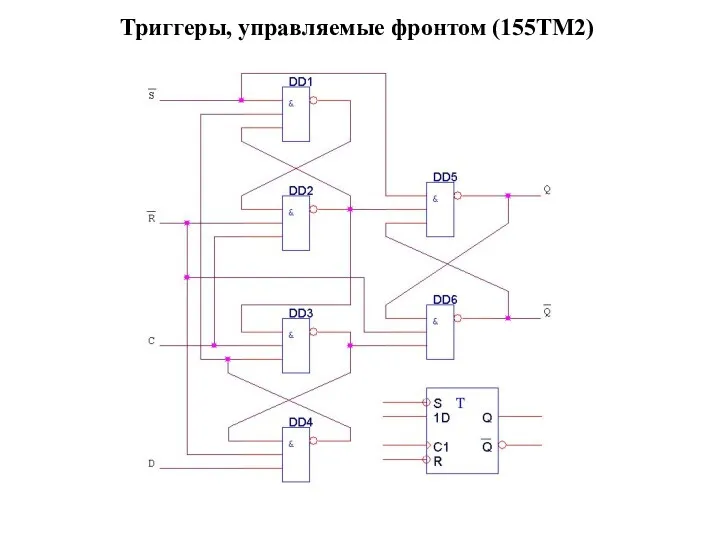

- 27. Триггеры, управляемые фронтом (155ТМ2)

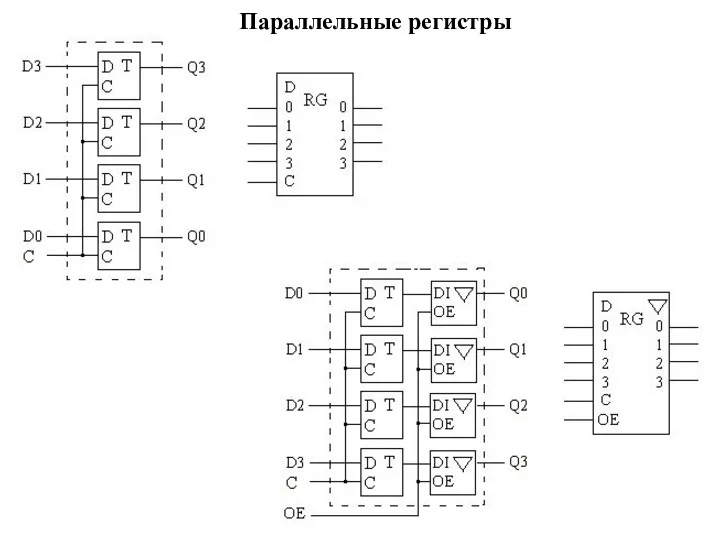

- 28. Параллельные регистры

- 29. Сдвигающие регистры

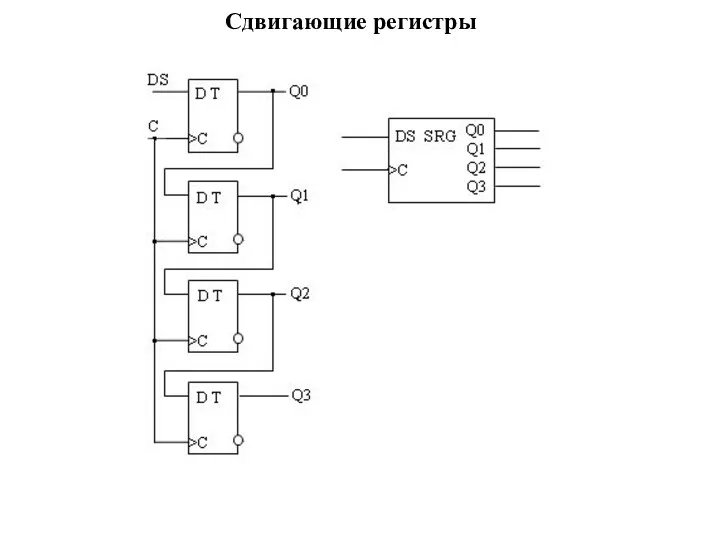

- 30. Универсальные регистры

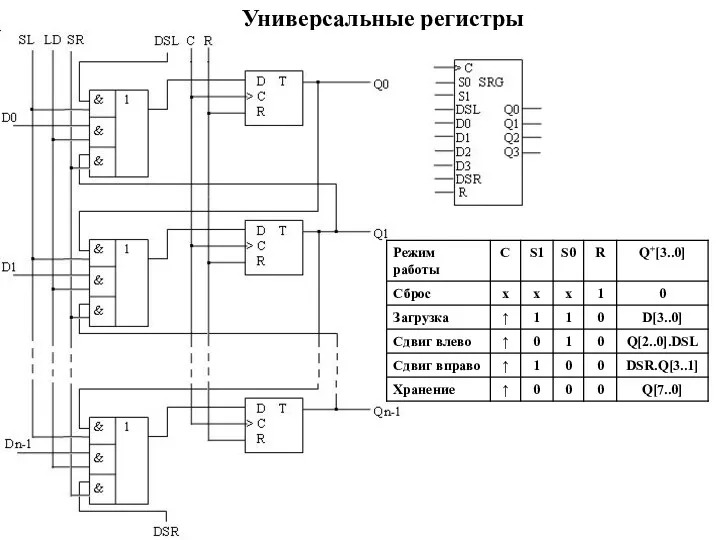

- 31. Счетчики – автоматы, фиксирующие число поступивших на их вход импульсов в том или ином коде Модуль

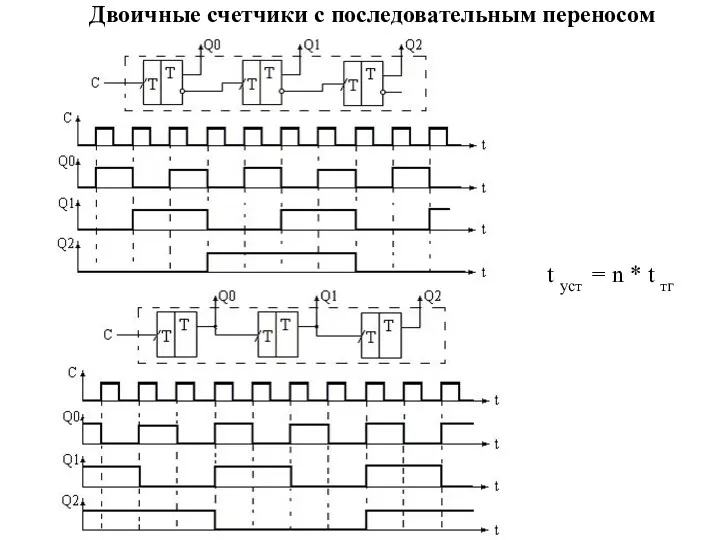

- 32. Двоичные счетчики с последовательным переносом t уст = n * t тг

- 33. Двоичный счетчик с параллельным переносом

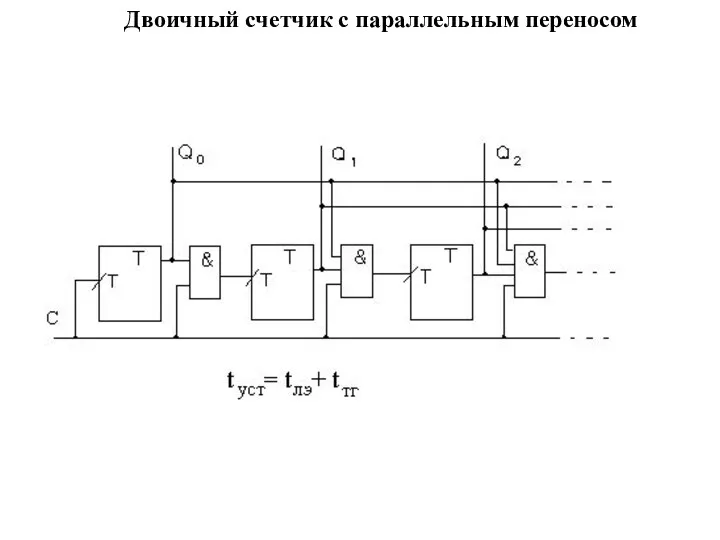

- 34. Синхронный счетчик

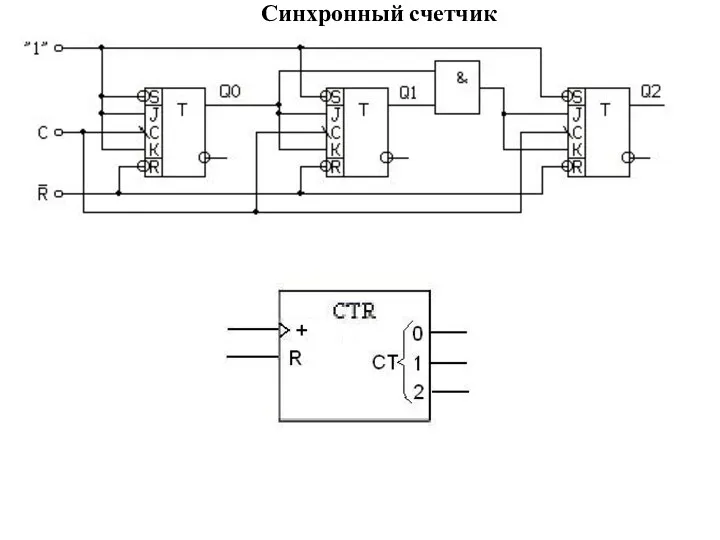

- 35. Сериализация - десериализация

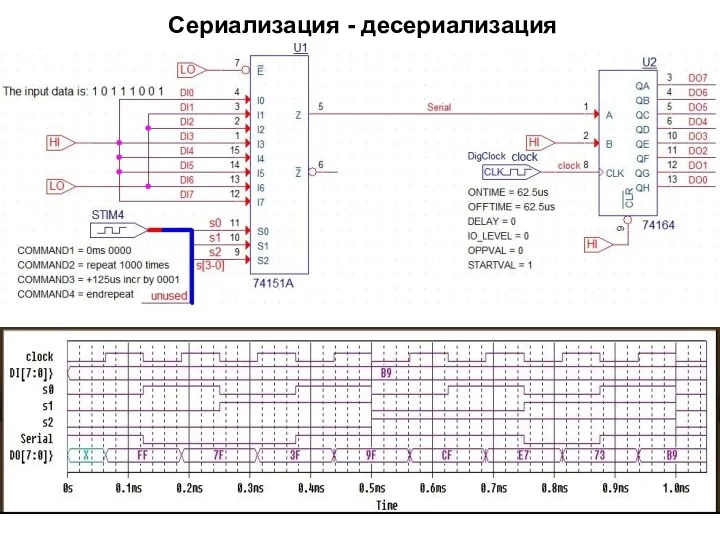

- 36. 2 Интегральные запоминающие устройства

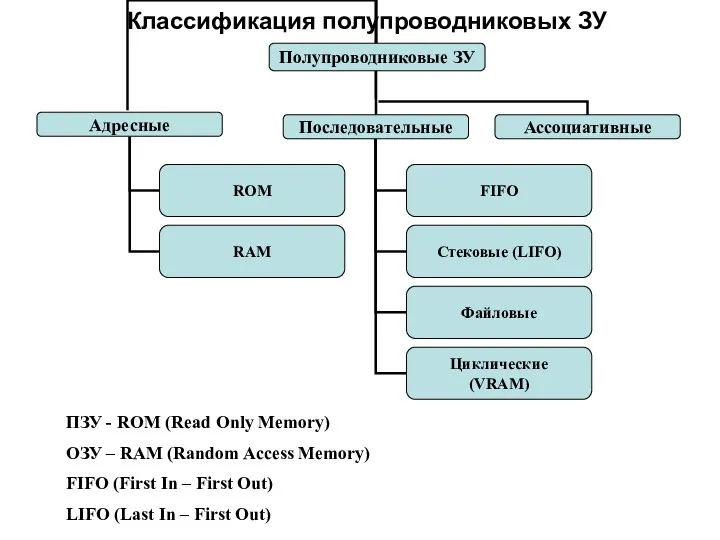

- 37. ПЗУ - ROM (Read Only Memory) ОЗУ – RAM (Random Access Memory) FIFO (First In –

- 38. ПЗУМ – ROM(M) - Mask ROM ППЗУ – PROM (Programmable ROM) РПЗУ-УФ – EPROM (Erasable Programmable

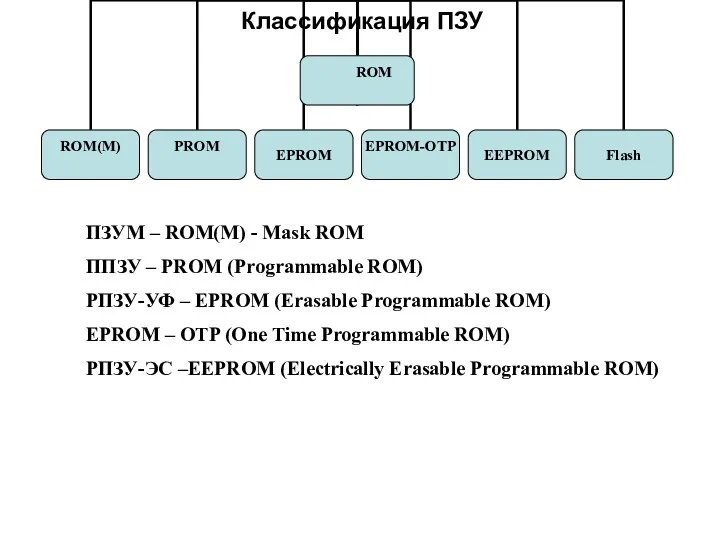

- 39. Классификация ОЗУ

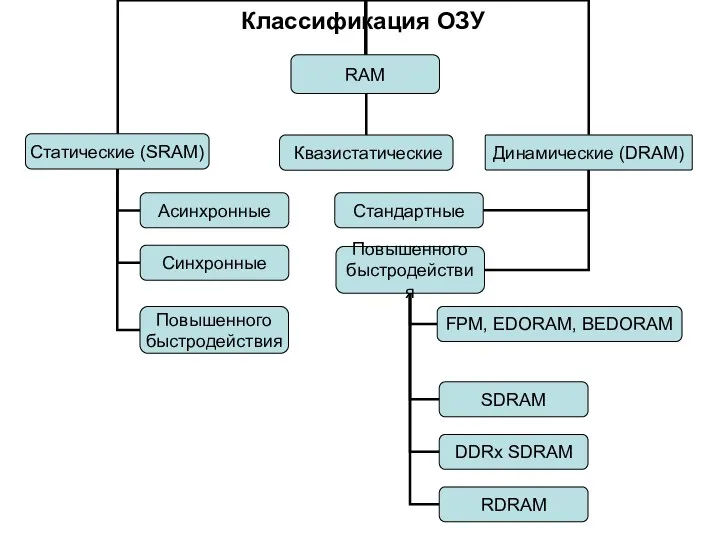

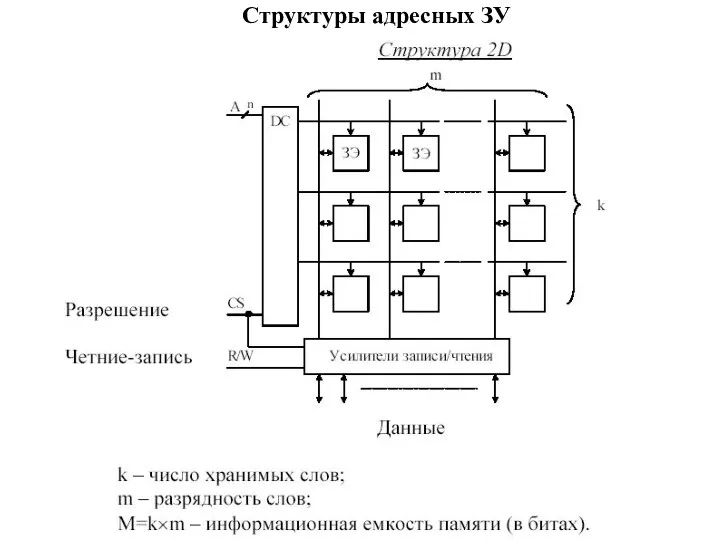

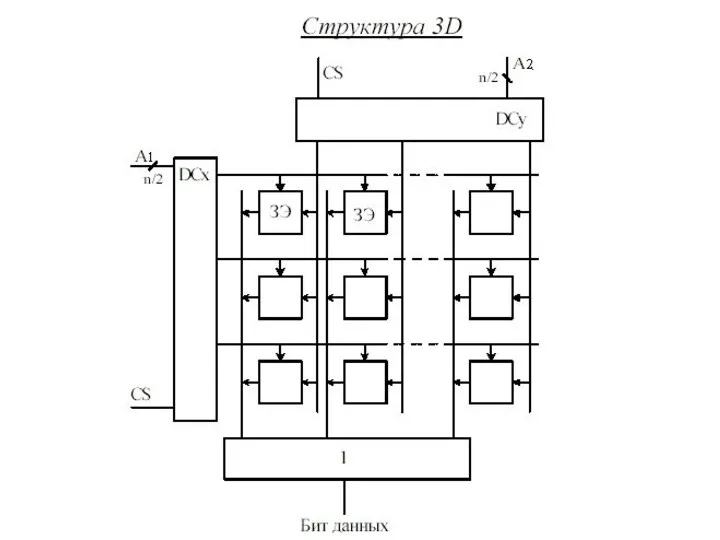

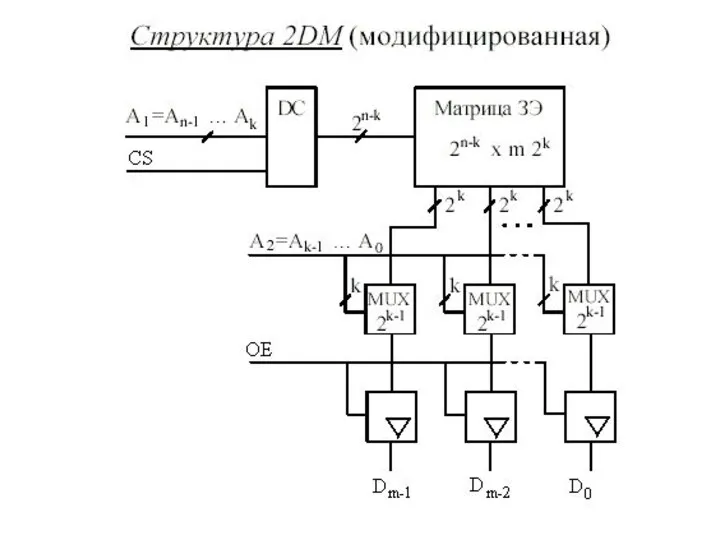

- 40. Структуры адресных ЗУ

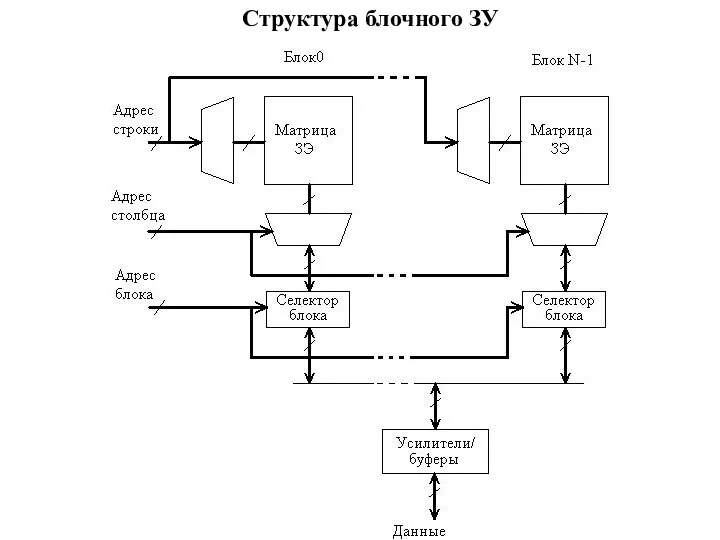

- 43. Структура блочного ЗУ

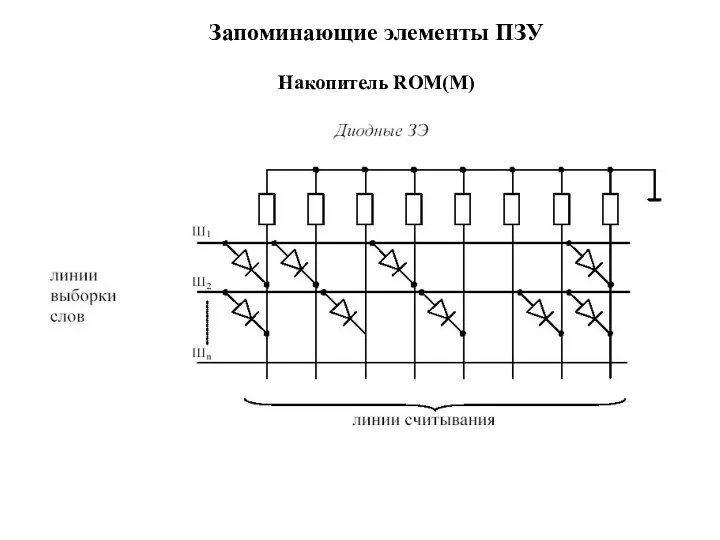

- 44. Запоминающие элементы ПЗУ Накопитель ROM(M)

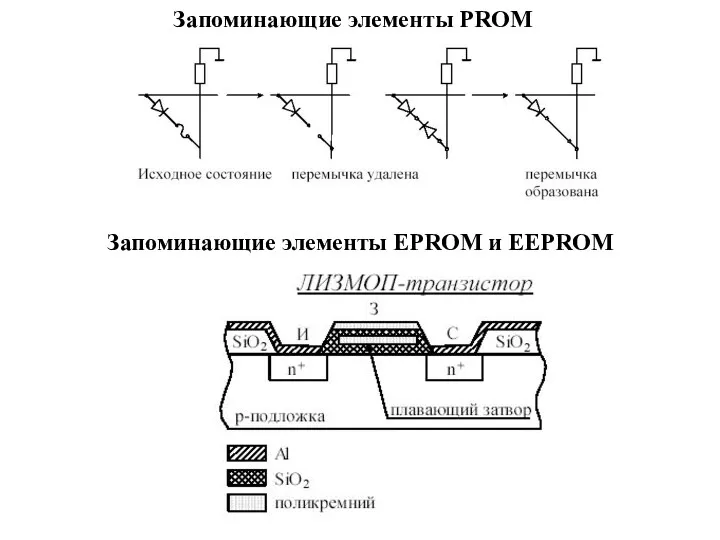

- 45. Запоминающие элементы PROM Запоминающие элементы EPROM и EEPROM

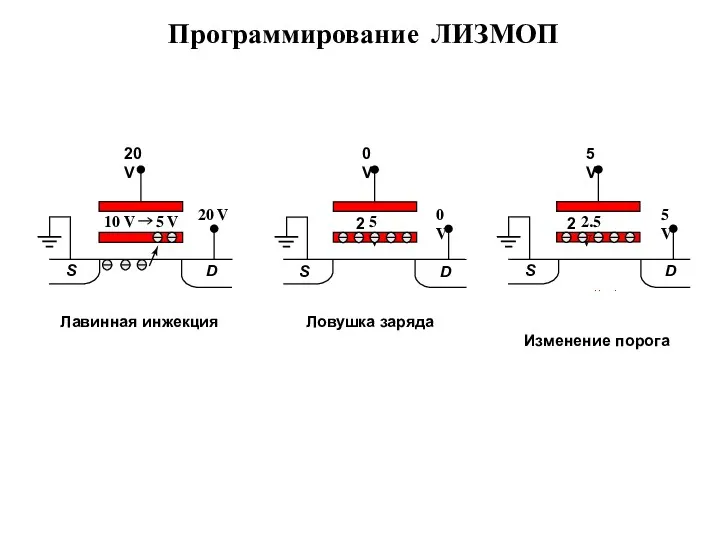

- 46. Программирование ЛИЗМОП

- 47. Транзистор с программируемым порогом

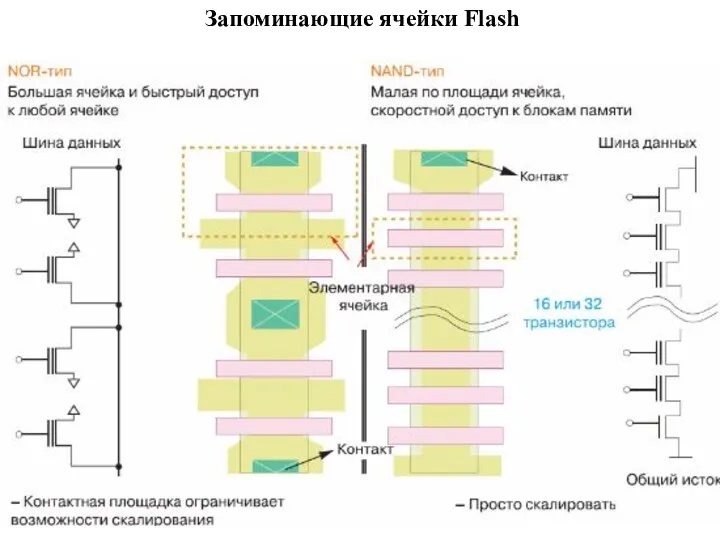

- 48. Запоминающие ячейки Flash

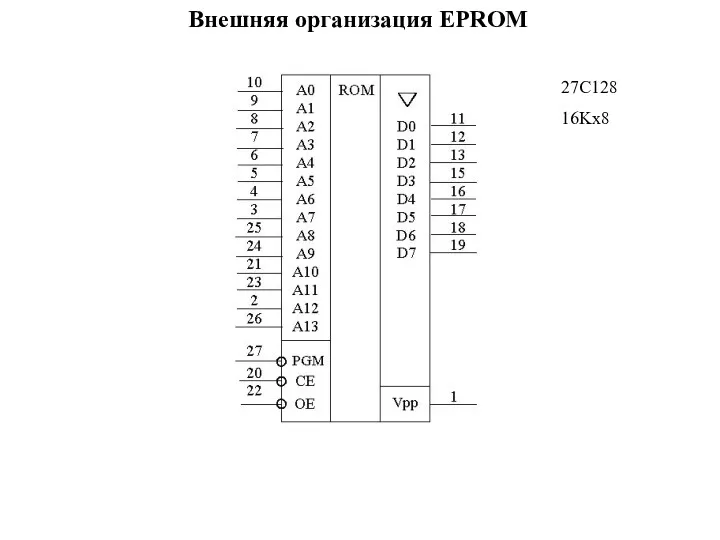

- 49. Внешняя организация EPROM 27C128 16Kx8

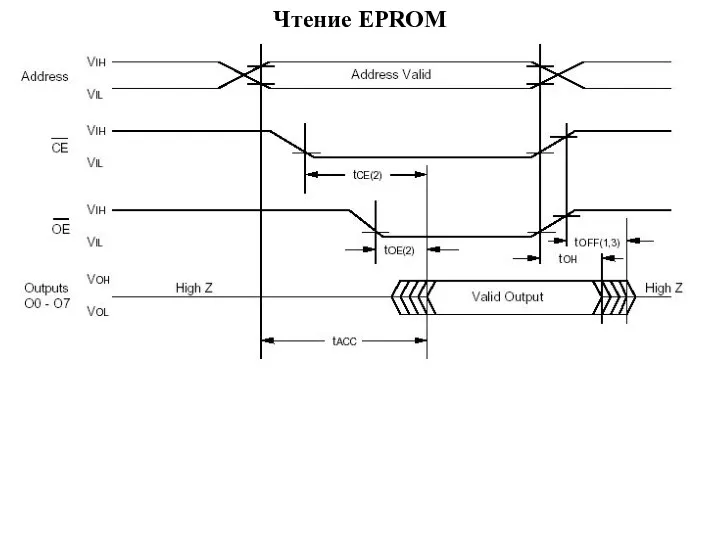

- 50. Чтение EPROM

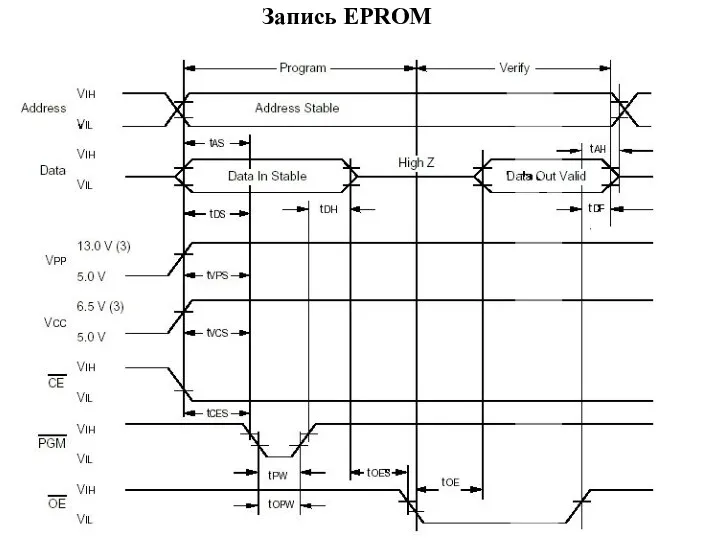

- 51. Запись EPROM

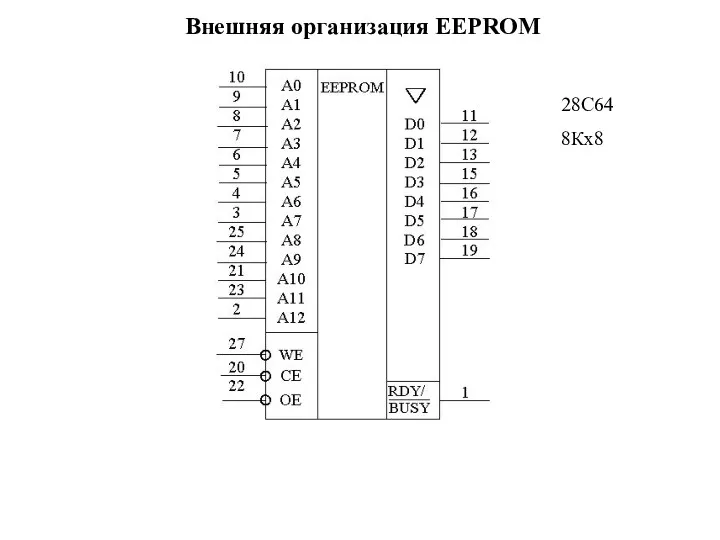

- 52. Внешняя организация EEPROM 28С64 8Кх8

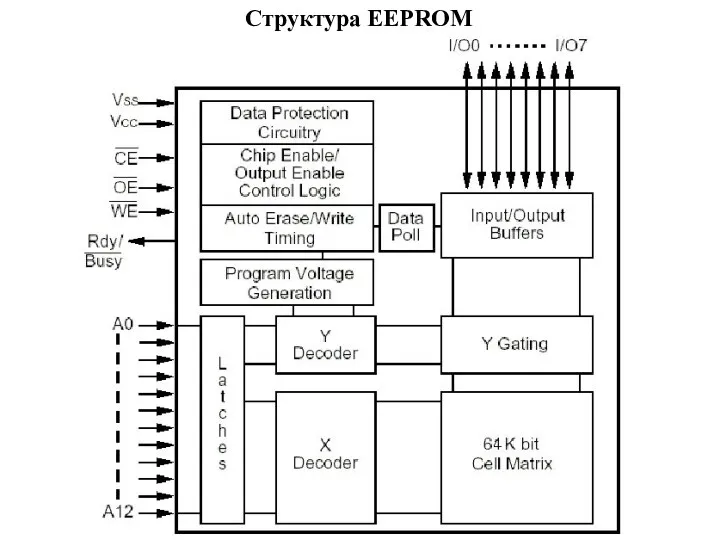

- 53. Структура EEPROM

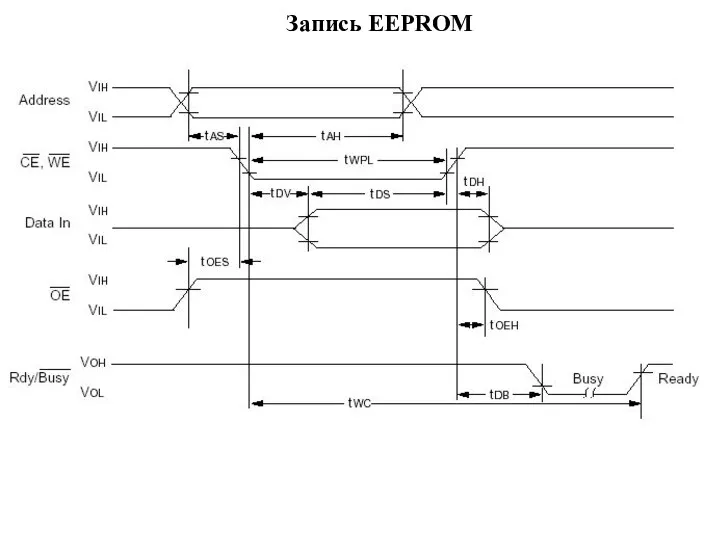

- 54. Запись EEPROM

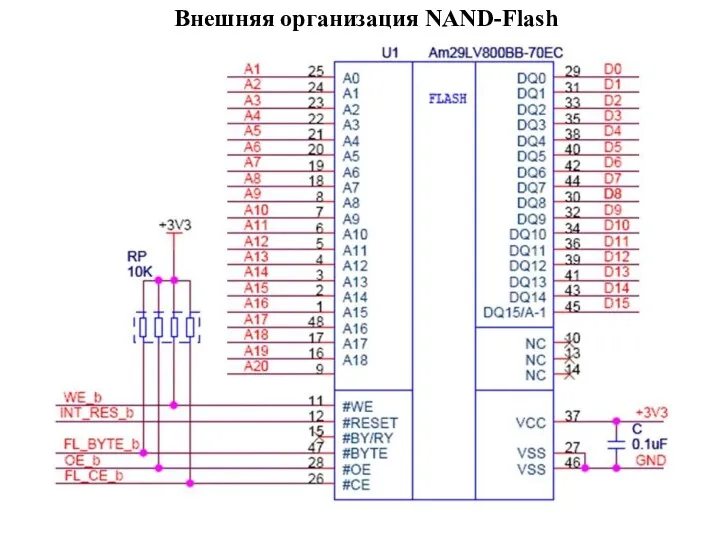

- 55. Внешняя организация NAND-Flash

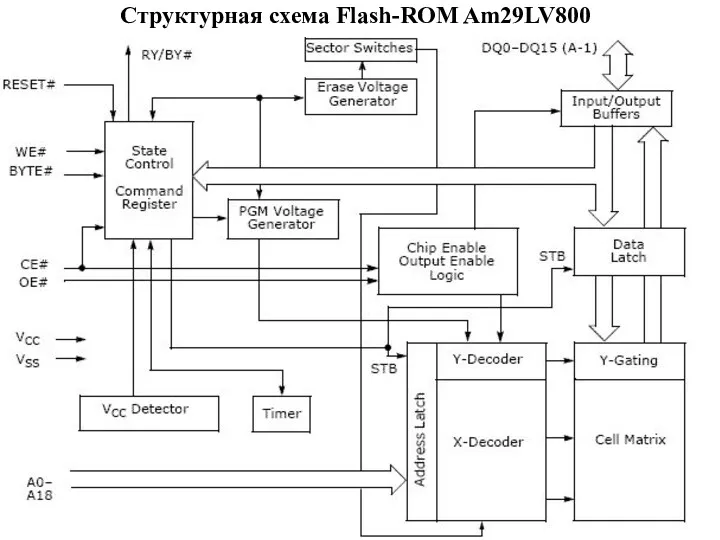

- 56. Структурная схема Flash-ROM Am29LV800

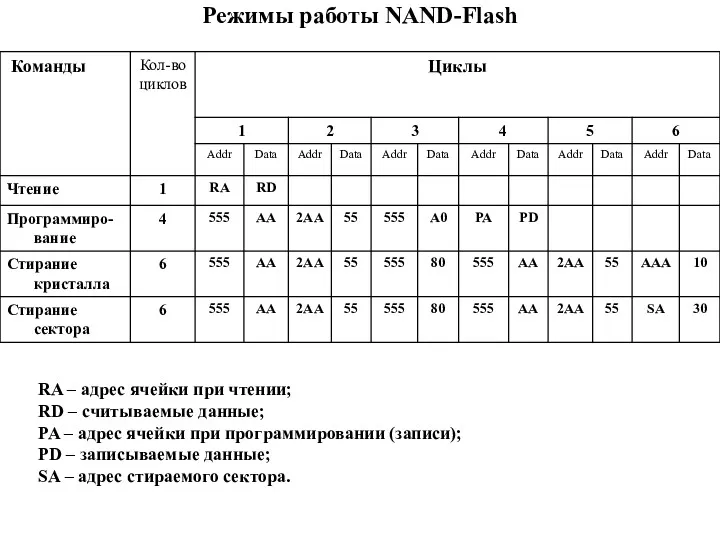

- 57. Режимы работы NAND-Flash RA – адрес ячейки при чтении; RD – считываемые данные; PA – адрес

- 58. 32-Гбит ИС флэш-памяти NAND-типа (техпроцесс 34-нм)

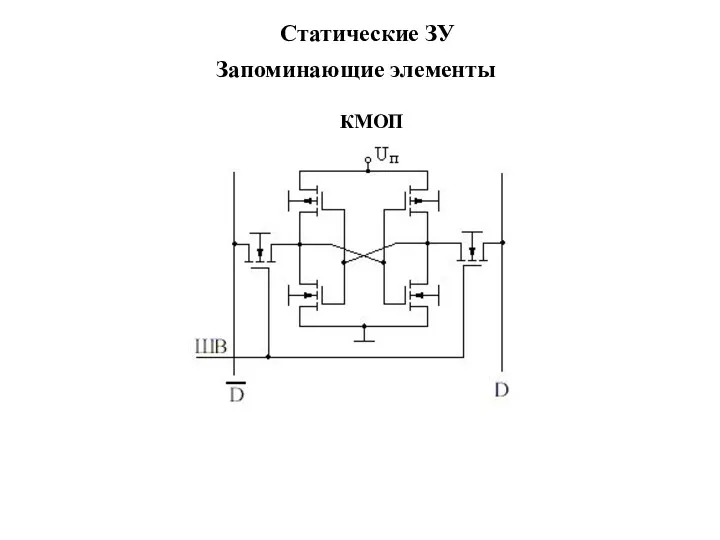

- 59. Запоминающие элементы КМОП Статические ЗУ

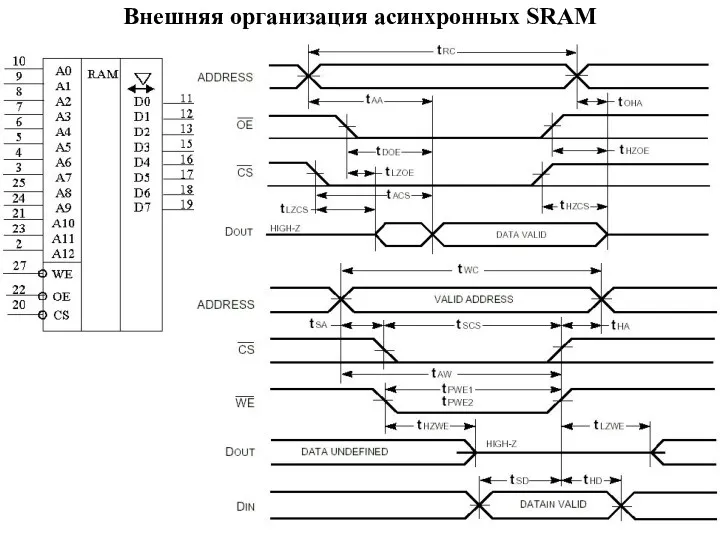

- 60. Внешняя организация асинхронных SRAM

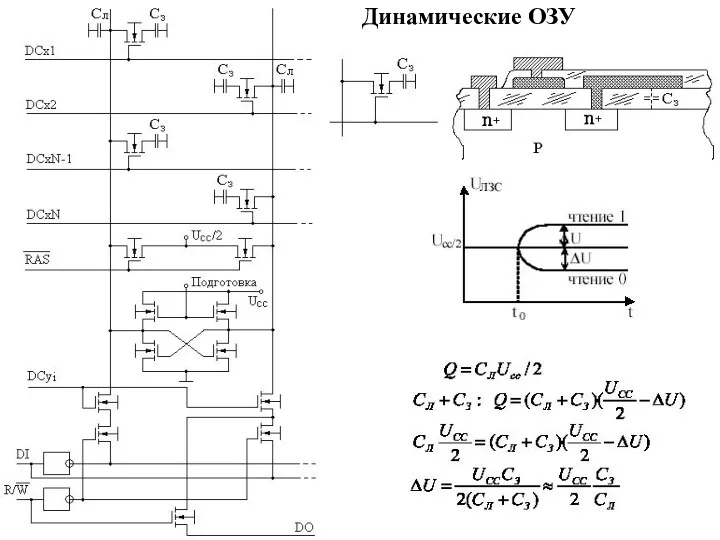

- 61. Динамические ОЗУ

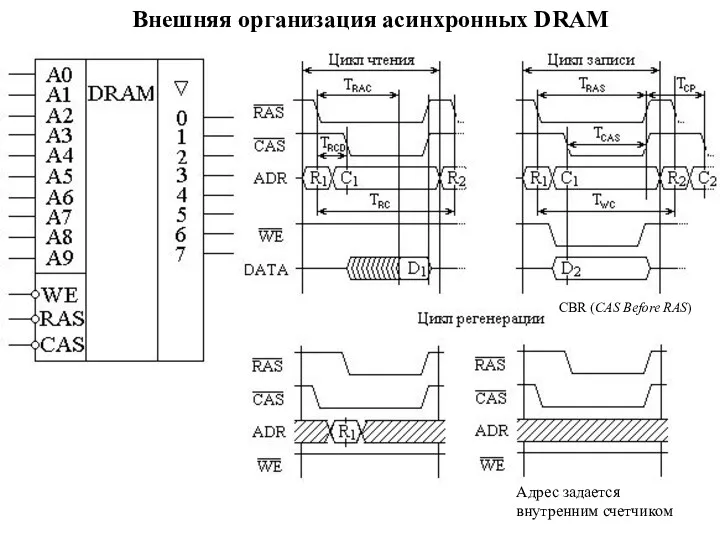

- 62. Внешняя организация асинхронных DRAM Адрес задается внутренним счетчиком CBR (CAS Before RAS)

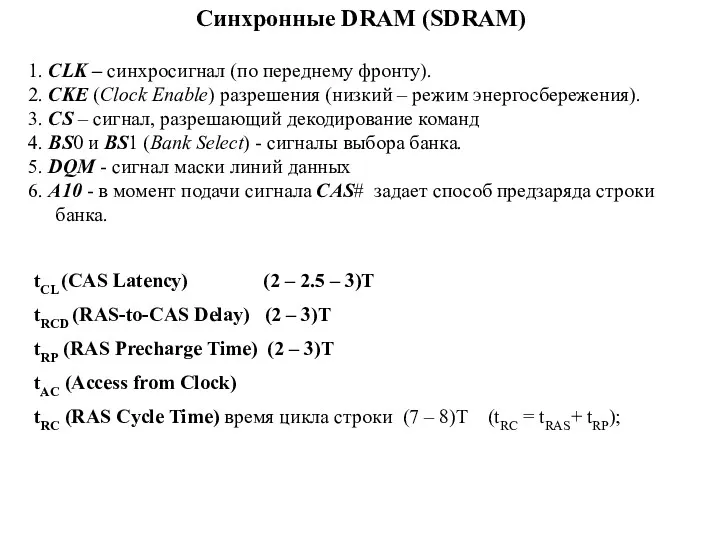

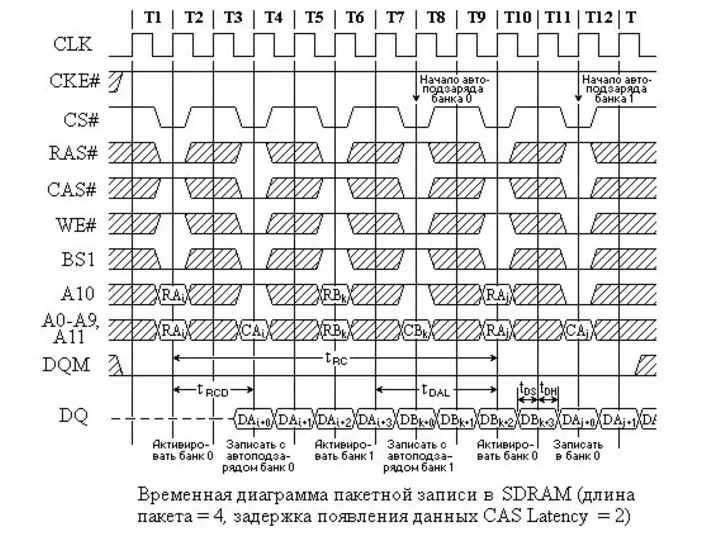

- 63. Синхронные DRAM (SDRAM) 1. CLK – синхросигнал (по переднему фронту). 2. CKE (Clock Enable) разрешения (низкий

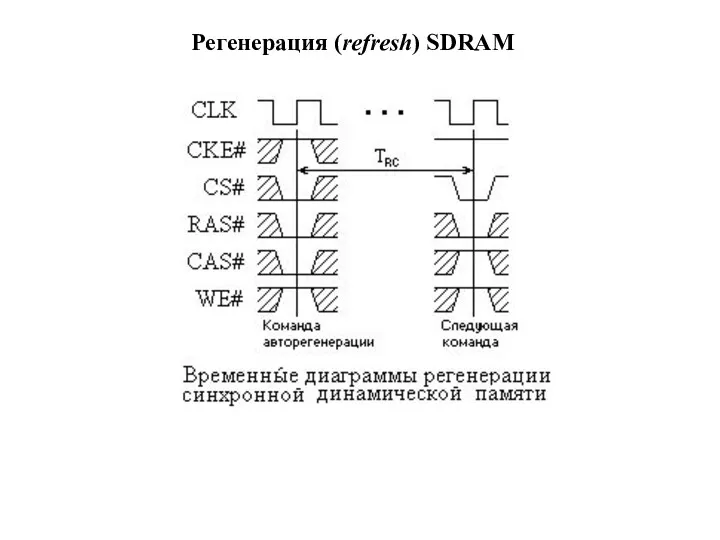

- 66. Регенерация (refresh) SDRAM

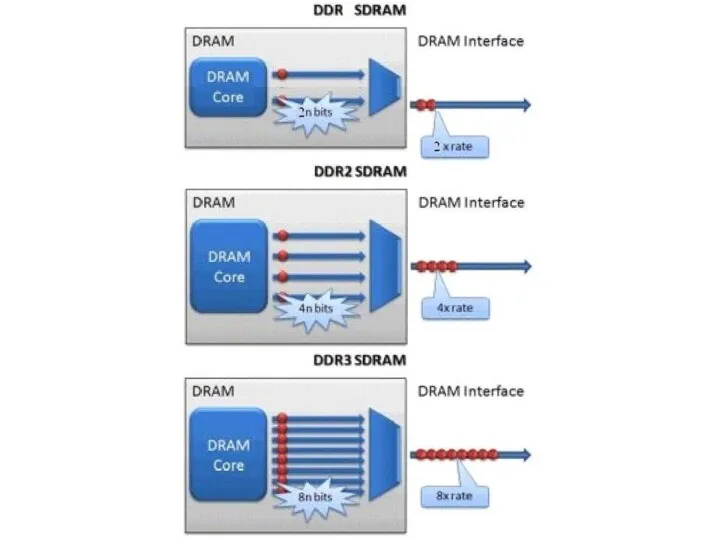

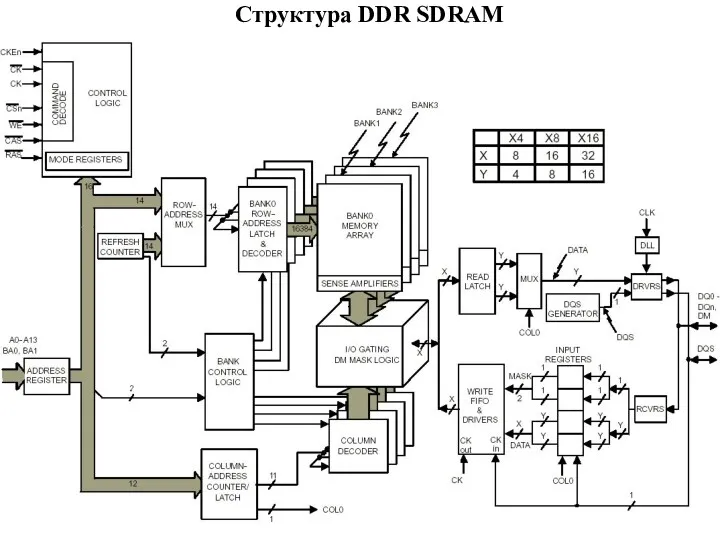

- 68. Структура DDR SDRAM

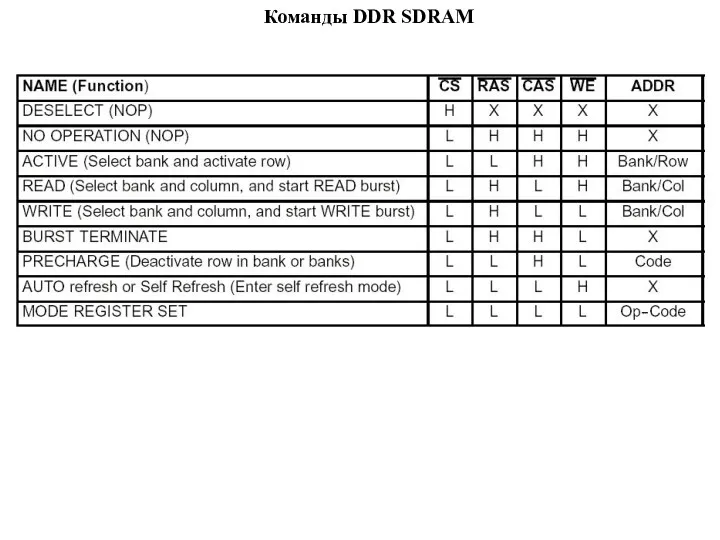

- 69. Команды DDR SDRAM

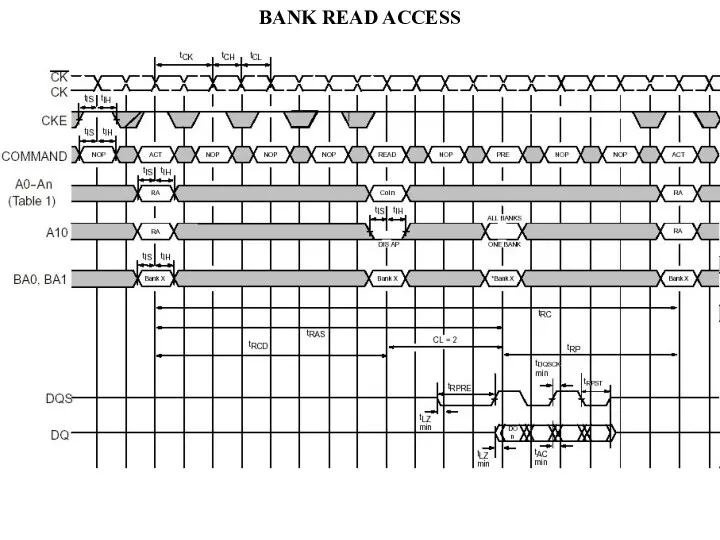

- 70. BANK READ ACCESS

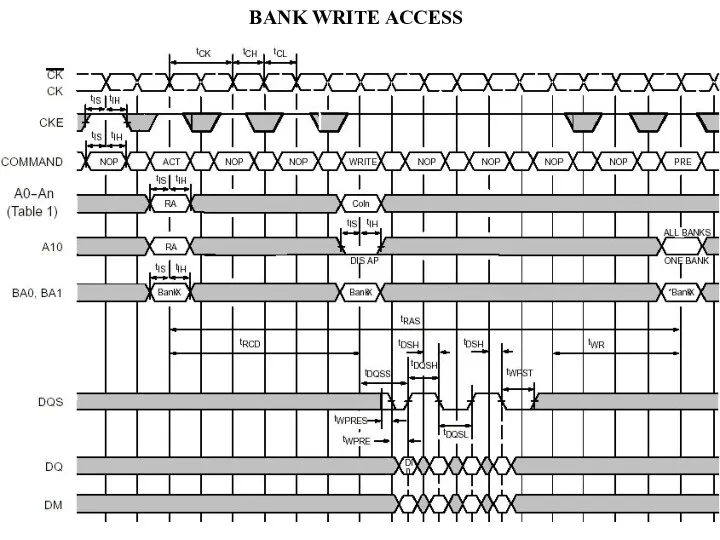

- 71. BANK WRITE ACCESS

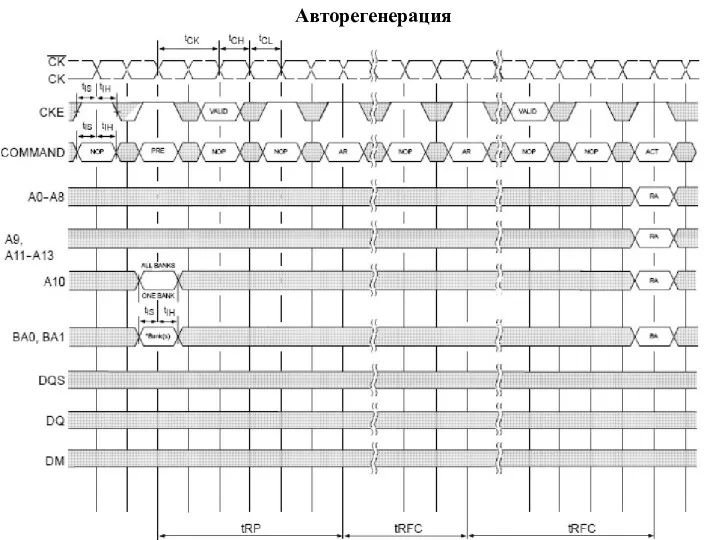

- 72. Авторегенерация

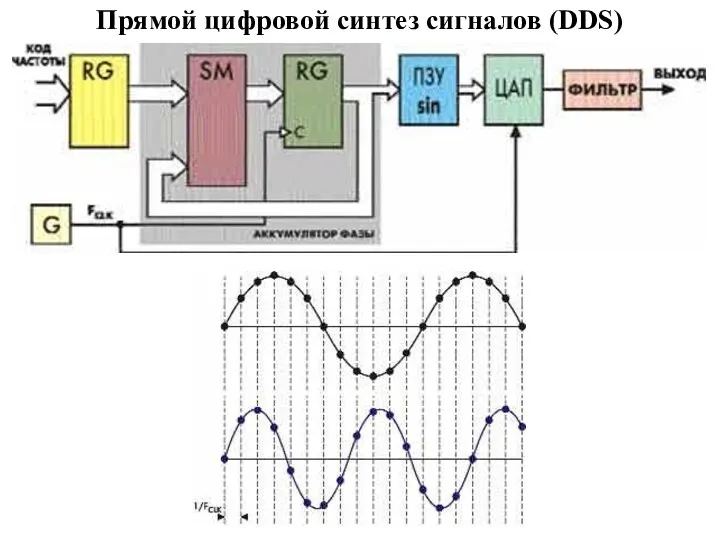

- 73. Прямой цифровой синтез сигналов (DDS)

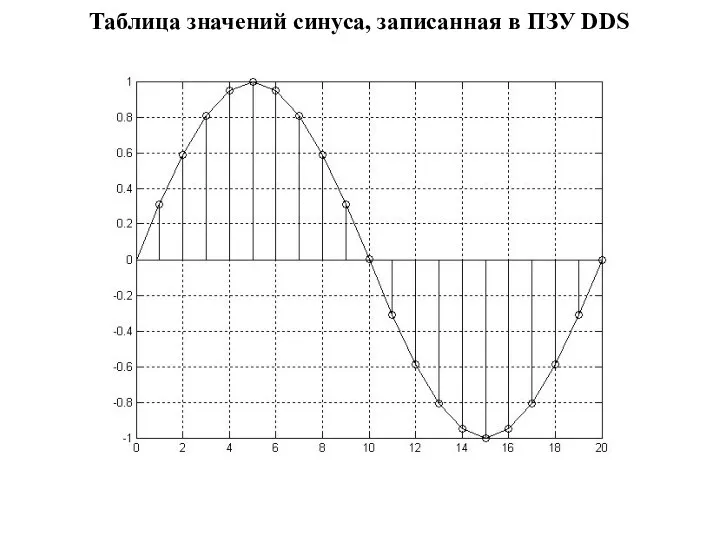

- 74. Таблица значений синуса, записанная в ПЗУ DDS

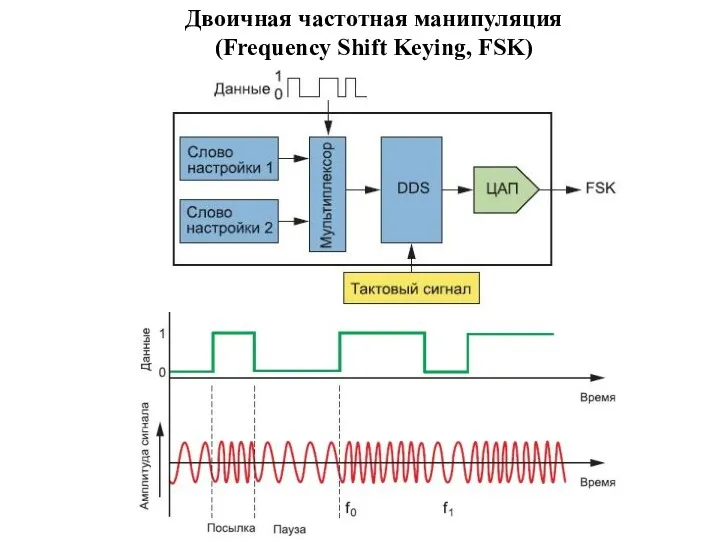

- 75. Двоичная частотная манипуляция (Frequency Shift Keying, FSK)

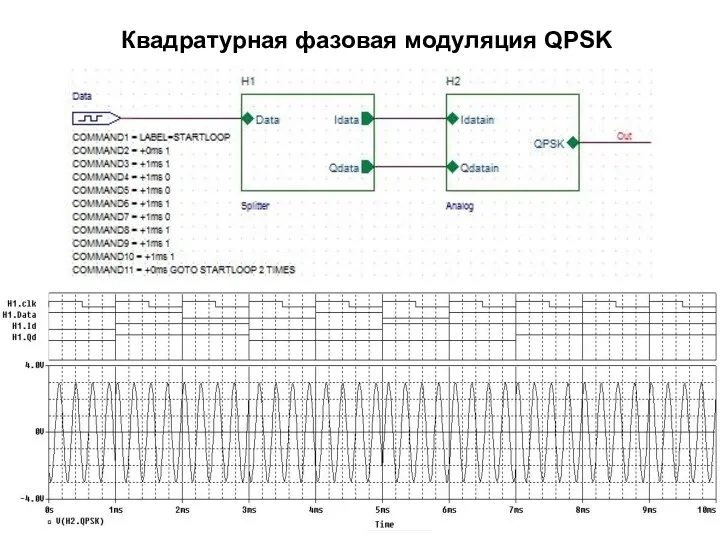

- 76. Квадратурная фазовая модуляция QPSK

- 78. Скачать презентацию

![Арифметико-логические устройства (АЛУ) Входы Выходы Операция M FSel1 FSel0 F[3..0]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/159202/slide-19.jpg)

Среднее арифметическое. Среднее значение величины

Среднее арифметическое. Среднее значение величины Теория управления

Теория управления Задание №9 ОГЭ. Обобщенный план варианта КИМ 2016 года для ГИА выпускников IХ классов по информатике и ИКТ

Задание №9 ОГЭ. Обобщенный план варианта КИМ 2016 года для ГИА выпускников IХ классов по информатике и ИКТ Пасха

Пасха Способы поверхностного упрочнения прокатных валков

Способы поверхностного упрочнения прокатных валков Номенклатура органических соединений

Номенклатура органических соединений Розробка інтегрованої автоматизованої системи управління виготовленням спирту з використанням хмарного середовища

Розробка інтегрованої автоматизованої системи управління виготовленням спирту з використанням хмарного середовища Проект Музей мяча. История, разновидности мяча, игры с мячом

Проект Музей мяча. История, разновидности мяча, игры с мячом Адаптивная физическая культура. Общие положения

Адаптивная физическая культура. Общие положения Чрезвычайные ситуации природного характера

Чрезвычайные ситуации природного характера Как запустить мейлинг с нулевым бюджетом

Как запустить мейлинг с нулевым бюджетом Открытое акционерное общество Холдинговая компания Якутуголь

Открытое акционерное общество Холдинговая компания Якутуголь Елді мекендердің су желісін төсеу

Елді мекендердің су желісін төсеу Презентация Музей истории села МОУ Лобанихинская СОШ

Презентация Музей истории села МОУ Лобанихинская СОШ Неопределенная форма глагола - инфинитив

Неопределенная форма глагола - инфинитив презентация педагогического проекта Учимся жить вместе

презентация педагогического проекта Учимся жить вместе Цифровой образовательный ресурс Социальное развитие детей дошкольного возраста (тест для педагогов дошкольных образовательных учреждений)

Цифровой образовательный ресурс Социальное развитие детей дошкольного возраста (тест для педагогов дошкольных образовательных учреждений) Сигнатурное комбо устройство MiVue™ i85

Сигнатурное комбо устройство MiVue™ i85 Судебная система в Российской Федерации

Судебная система в Российской Федерации Типы рыночных структур

Типы рыночных структур Ввод и редактирование текста

Ввод и редактирование текста Развитие познавательной активности у обучающихся средствами ИКТ в рамках ФГОС (на примере уроков географии)

Развитие познавательной активности у обучающихся средствами ИКТ в рамках ФГОС (на примере уроков географии) Цветы в нашей жизни. Диск

Цветы в нашей жизни. Диск Творческий проект Бисероплетение

Творческий проект Бисероплетение Добровольное медицинское страхование сотрудников ООО РДВ-СОФТ

Добровольное медицинское страхование сотрудников ООО РДВ-СОФТ Физминутка на движение Веселая зарядка

Физминутка на движение Веселая зарядка дифференциация гласных а я

дифференциация гласных а я Классный час .Тема 23 февраля - день защитника Отечества 1Б класс с творческими работами

Классный час .Тема 23 февраля - день защитника Отечества 1Б класс с творческими работами