Содержание

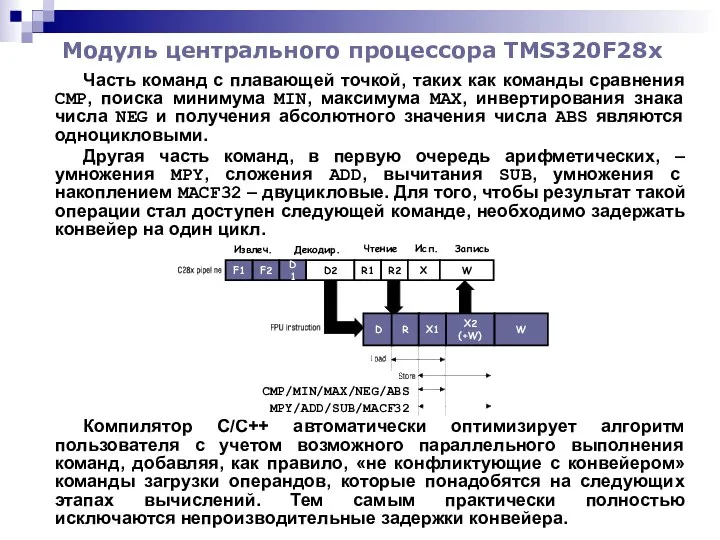

- 2. Модуль центрального процессора TMS320F28x Часть команд с плавающей точкой, таких как команды сравнения CMP, поиска минимума

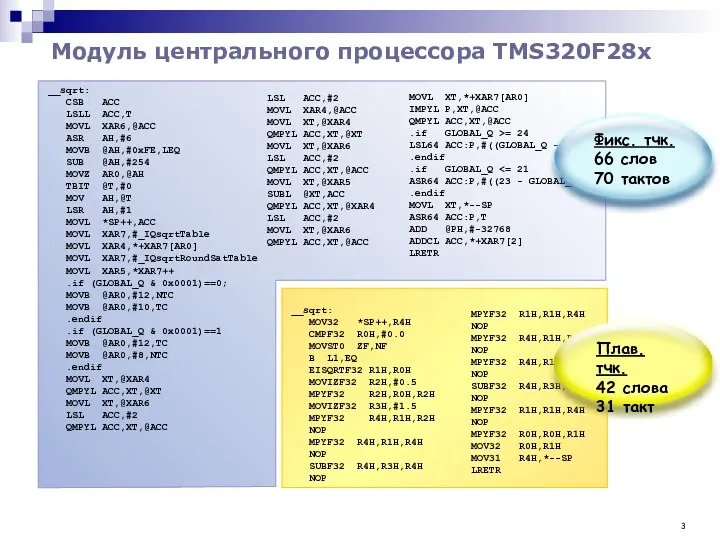

- 3. Модуль центрального процессора TMS320F28x

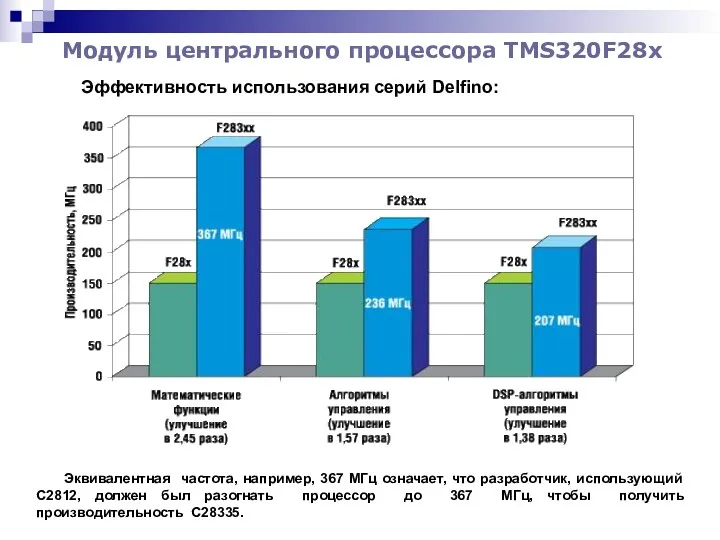

- 4. Модуль центрального процессора TMS320F28x Эквивалентная частота, например, 367 МГц означает, что разработчик, использующий C2812, должен был

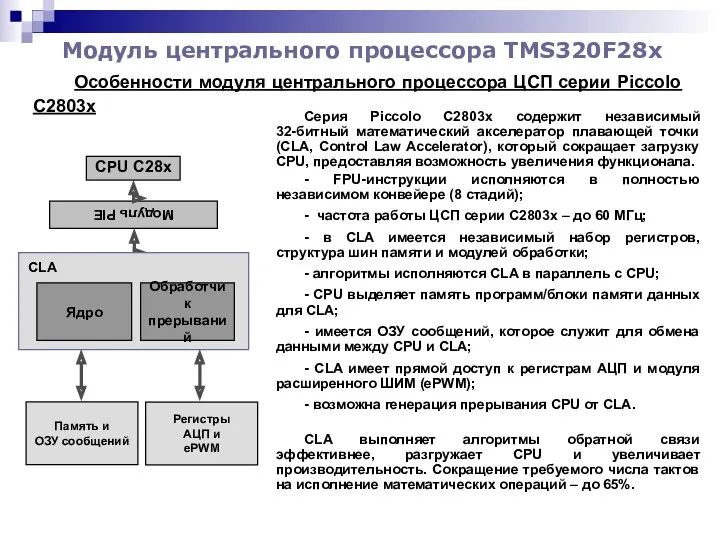

- 5. Модуль центрального процессора TMS320F28x Особенности модуля центрального процессора ЦСП серии Piccolo C2803x Серия Piccolo C2803x содержит

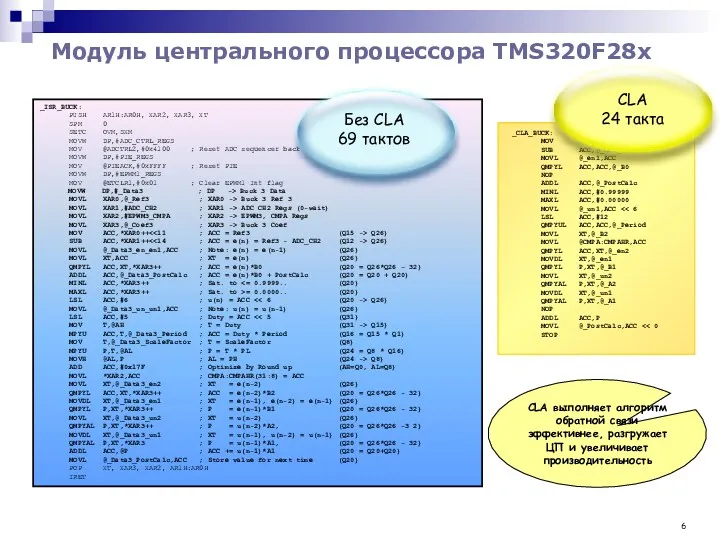

- 6. Модуль центрального процессора TMS320F28x

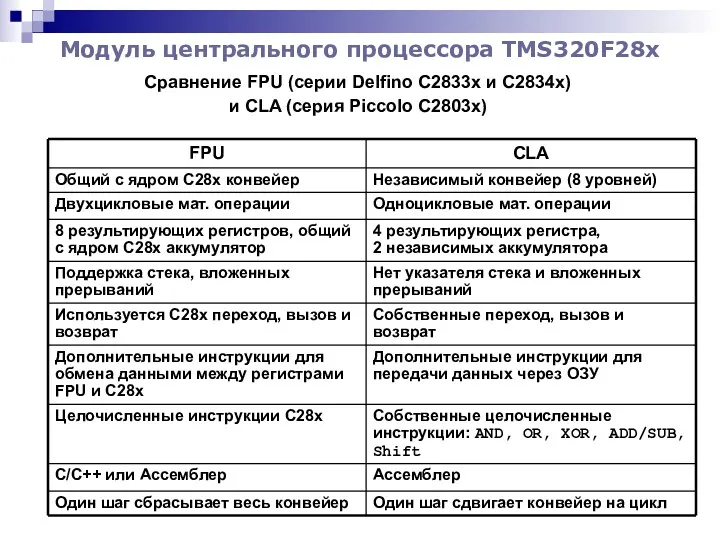

- 7. Модуль центрального процессора TMS320F28x Сравнение FPU (серии Delfino C2833x и C2834x) и CLA (серия Piccolo C2803x)

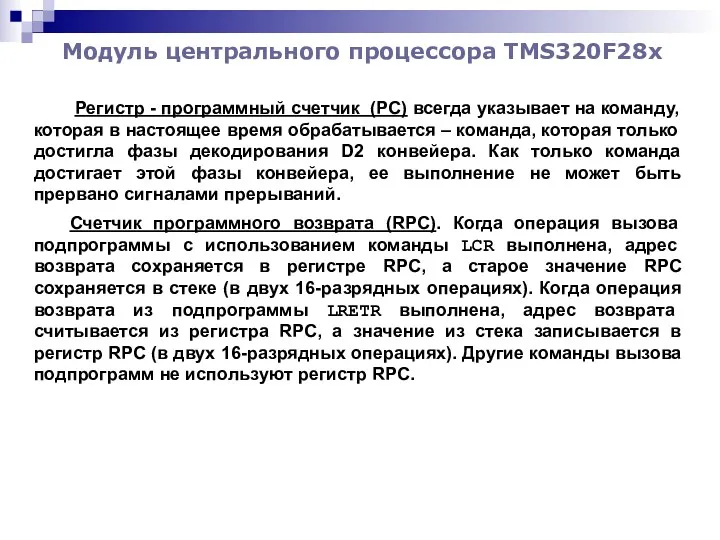

- 8. Модуль центрального процессора TMS320F28x Регистр - программный счетчик (PC) всегда указывает на команду, которая в настоящее

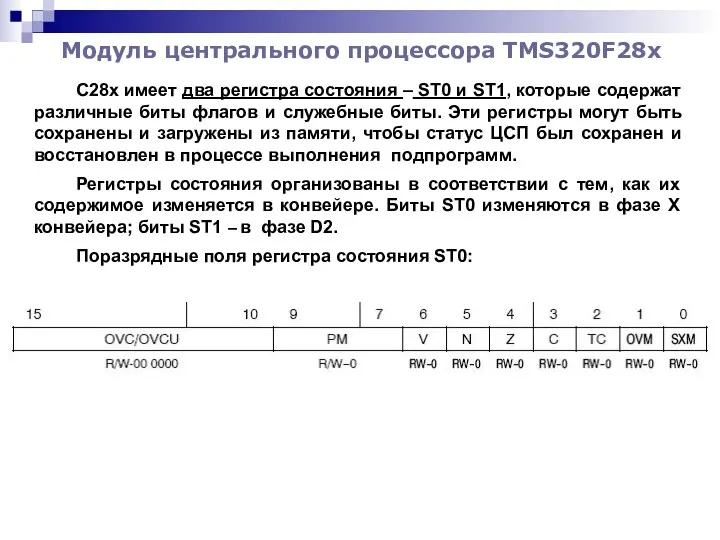

- 9. Модуль центрального процессора TMS320F28x C28x имеет два регистра состояния – ST0 и ST1, которые содержат различные

- 10. Модуль центрального процессора TMS320F28x OVC/OVCU (биты ST010-15) – счетчик переполнений. Режим установки этих флагов активен, когда

- 11. Модуль центрального процессора TMS320F28x PM (бит ST07-9) – биты режима сдвига, задают сдвиговый режим выходных операций

- 12. Модуль центрального процессора TMS320F28x N (бит ST05) – флаг знака. N установлен, если результат операции –

- 13. Модуль центрального процессора TMS320F28x C (бит ST03) – флаг переноса. Этот флаг показывает, когда сложение, инкремент

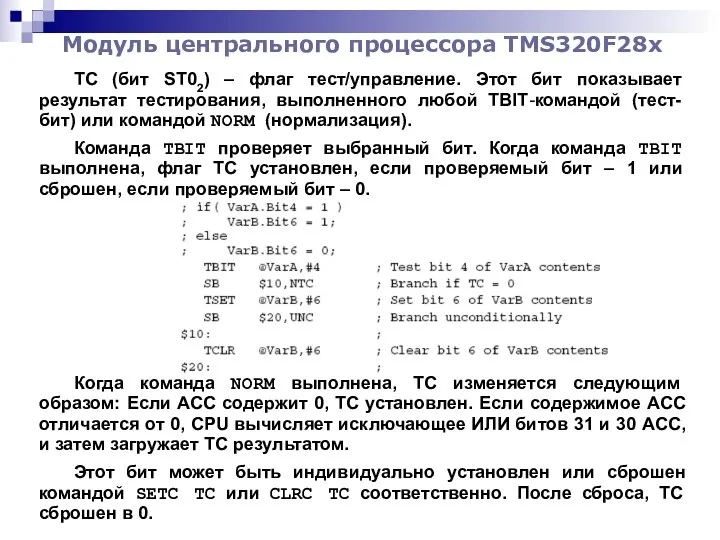

- 14. Модуль центрального процессора TMS320F28x TC (бит ST02) – флаг тест/управление. Этот бит показывает результат тестирования, выполненного

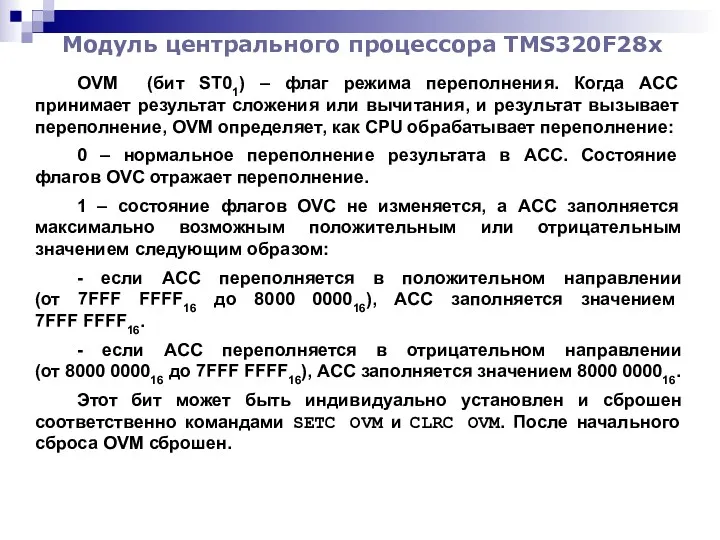

- 15. Модуль центрального процессора TMS320F28x OVM (бит ST01) – флаг режима переполнения. Когда ACC принимает результат сложения

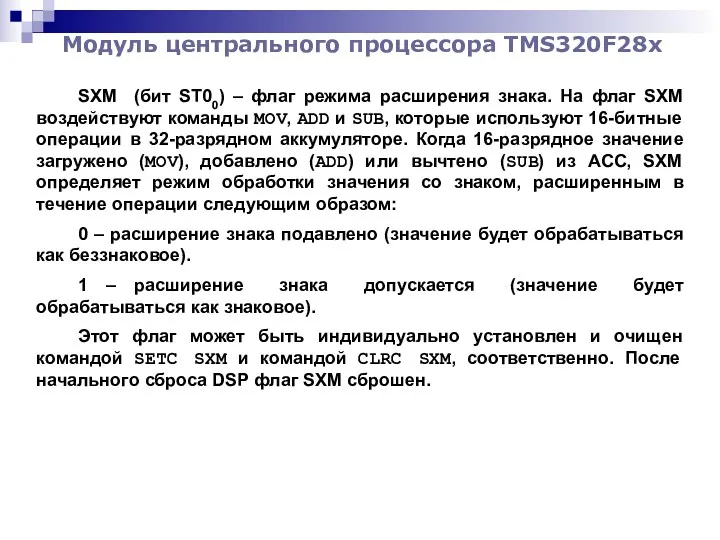

- 16. Модуль центрального процессора TMS320F28x SXM (бит ST00) – флаг режима расширения знака. На флаг SXM воздействуют

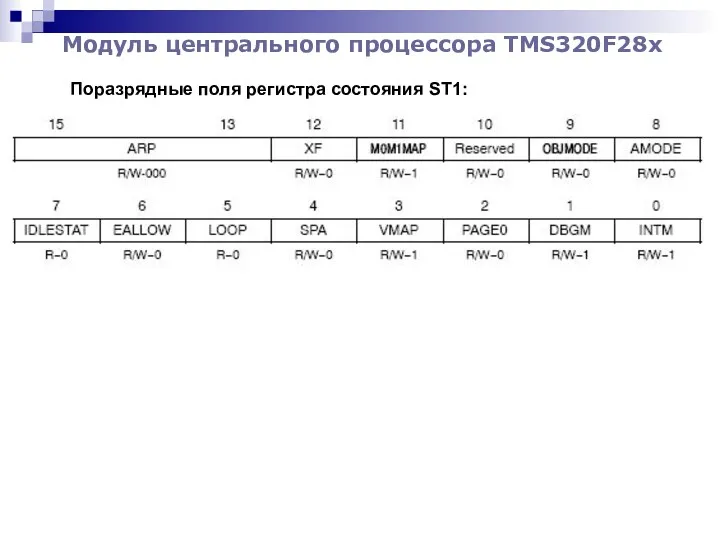

- 17. Модуль центрального процессора TMS320F28x Поразрядные поля регистра состояния ST1:

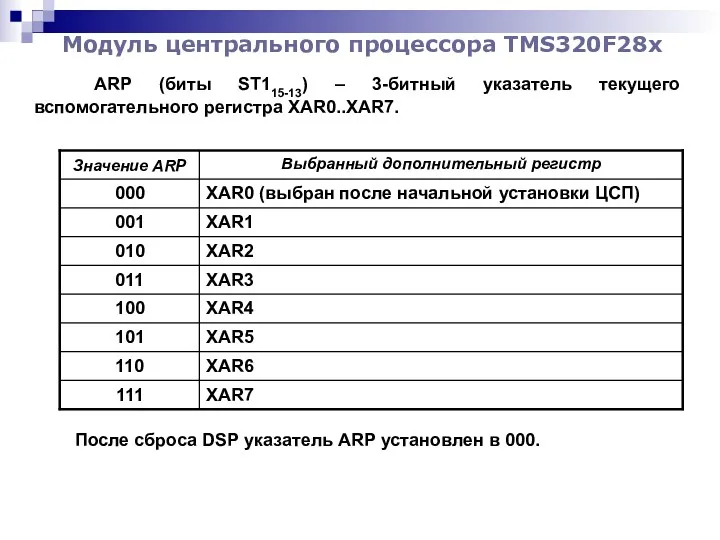

- 18. Модуль центрального процессора TMS320F28x ARP (биты ST115-13) – 3-битный указатель текущего вспомогательного регистра XAR0..XAR7. После сброса

- 19. Модуль центрального процессора TMS320F28x XF (бит ST112) – флаг, отражающий текущее состояние вывода /XF_XPLLDIS. Программная установка

- 21. Скачать презентацию

Компетенция личностного самосовершенствования

Компетенция личностного самосовершенствования Разработка ресурсосберегающего способа производства топливно-плавильных материалов на основе техногенного сырья (Н3)

Разработка ресурсосберегающего способа производства топливно-плавильных материалов на основе техногенного сырья (Н3) Изготовление декоративного изделия 3D ручкой like

Изготовление декоративного изделия 3D ручкой like Готовая преза с триггерами

Готовая преза с триггерами урок по теме Карбоновые кислоты

урок по теме Карбоновые кислоты Операции Банка России на финансовом рынке. Лекция №4

Операции Банка России на финансовом рынке. Лекция №4 Общая краниология. Общие сведения о черепе

Общая краниология. Общие сведения о черепе Социальная психология личности

Социальная психология личности Роль физической культуры в сохранении здоровья

Роль физической культуры в сохранении здоровья Речь монологическая и диалогическая

Речь монологическая и диалогическая Холокост в литературе. То что забыть нельзя

Холокост в литературе. То что забыть нельзя Земля – уникальная планета (Урок-презентация).

Земля – уникальная планета (Урок-презентация). Мишка. Найди 3 отличия

Мишка. Найди 3 отличия Термодинамические процессы идеальных газов

Термодинамические процессы идеальных газов We're having a great time

We're having a great time Цветотерапия Попугаи

Цветотерапия Попугаи Фестиваль гражданского общества Добрые люди

Фестиваль гражданского общества Добрые люди ПрезентацияХлеб всему голова

ПрезентацияХлеб всему голова Родительское собрание для 1 класса.

Родительское собрание для 1 класса. Ауруханадан тыс пневманиямен ауыратын науқастарды емдеу кезіндегі пенициллин мен цефтриаксонның салыстырмалы

Ауруханадан тыс пневманиямен ауыратын науқастарды емдеу кезіндегі пенициллин мен цефтриаксонның салыстырмалы Обществознание и общественные науки

Обществознание и общественные науки Полиомиелит. Мероприятия в отношении больных полиомиелитом, острыми вялыми параличами

Полиомиелит. Мероприятия в отношении больных полиомиелитом, острыми вялыми параличами Угол. Измерение углов

Угол. Измерение углов Пищевая и легкая промышленность

Пищевая и легкая промышленность Настройка компьютера. Компьютерный вирус

Настройка компьютера. Компьютерный вирус Призентация творческого проекта Мягкая игрушка

Призентация творческого проекта Мягкая игрушка ОГАС 2.0. Программно-техническое решение системы (часть 2)

ОГАС 2.0. Программно-техническое решение системы (часть 2) Формирование стратегии и школы стратегического управления

Формирование стратегии и школы стратегического управления