Содержание

- 2. Список литературы 1. В.Ф. Мелехин. Вычислительные машины системы и сети.

- 3. Иерархия запоминающих устройств Память наряду с процессором в значительной мере определяет основные возможности ВМ — ее

- 4. Иерархия запоминающих устройств

- 5. Иерархия запоминающих устройств ГОУ ОГУ 2008 Закономерности: • чем меньше время доступа, тем выше стоимость хранения

- 6. Иерархия запоминающих устройств ГОУ ОГУ 2008 По мере движения вниз по иерархической структуре: 1. Уменьшается соотношение

- 7. Структура микросхемы памяти ГОУ ОГУ 2008

- 8. Статическая и динамическая память Оперативная память может составляться из микросхем динамического (Dynamic Random Access Memory -DRAM)

- 9. Запоминающие элементы ГОУ ОГУ 2008 Запоминающий элемент динамического ОЗУ Запоминающий элемент статического ОЗУ

- 10. Кэш-память Кэш-память представляет собой быстродействующее ЗУ, размещенное на одном кристалле с ЦП или внешнее по отношению

- 11. В структуре кэш-памяти выделяют два типа блоков данных: - память отображения данных (собственно сами данные, дублированные

- 12. Полностью ассоциативный кэш 8х8 для 10-битного адреса

- 13. Кэш прямого отображения 8х8 для 10-битного адреса

- 14. Двухвходовый ассоциативный кэш 8х8 для 10-битного адреса

- 15. Для согласования содержимого кэш-памяти и оперативной памяти используют три метода записи: - cквозная запись (write through)

- 16. Tср = (Thit x Rhit) + (Tmiss x (1 - Rhit)) где Thit - время доступа

- 17. Структура стека

- 18. Схема работы со стеком

- 22. Скачать презентацию

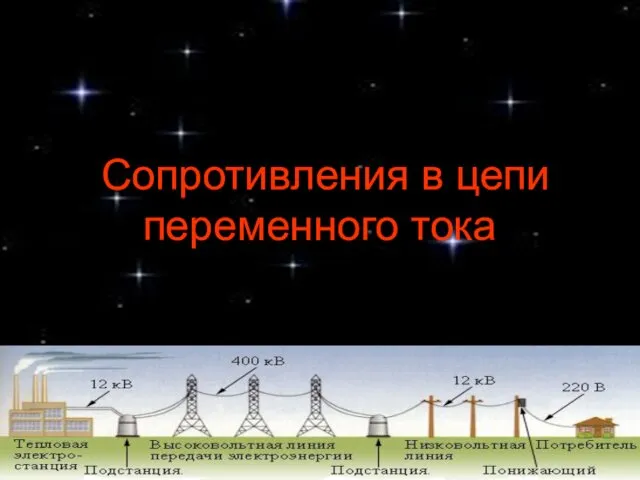

Сопротивления в цепи переменного тока

Сопротивления в цепи переменного тока Информационная поддержка жизненных циклов продукции в строительстве

Информационная поддержка жизненных циклов продукции в строительстве Смутное время (1598-1613)

Смутное время (1598-1613) Моря России

Моря России Современные направления научных исследований

Современные направления научных исследований Легендарный парад на Красной площади в Москве 7 ноября 1941 года

Легендарный парад на Красной площади в Москве 7 ноября 1941 года Дамыта оқыту технологиясы. Дамыта оқыту жүйесі

Дамыта оқыту технологиясы. Дамыта оқыту жүйесі фотоотчет Подготовка к празднованию Дня Победы

фотоотчет Подготовка к празднованию Дня Победы Классный час Моя Москва. Транспорт столицы.

Классный час Моя Москва. Транспорт столицы. Модест Петрович Мусоргский. Картинки с выставки

Модест Петрович Мусоргский. Картинки с выставки Проект Моя семья

Проект Моя семья Слайд-презентация Проектная деятельность в ДОУ

Слайд-презентация Проектная деятельность в ДОУ Виды электрического кабеля

Виды электрического кабеля Экономические задачи

Экономические задачи 20231214_isakova_t.a._master-klass_izmerenie_pulsa_s_pomoshchyu_fotopletizmografii_v_ramkah_uchebnoy_laboratorii_po_neyrotehnologii_i_ispolzovanie_tsifrovogo_mikroskopa_na_urokah_biologii_0

20231214_isakova_t.a._master-klass_izmerenie_pulsa_s_pomoshchyu_fotopletizmografii_v_ramkah_uchebnoy_laboratorii_po_neyrotehnologii_i_ispolzovanie_tsifrovogo_mikroskopa_na_urokah_biologii_0 Возведение зданий методом подъёма перекрытий и этажей

Возведение зданий методом подъёма перекрытий и этажей Алюминий – химический элемент, простое вещество

Алюминий – химический элемент, простое вещество Немецкая овчарка

Немецкая овчарка Презентация Полимеры. Волокна. Каучуки. 10 класс.

Презентация Полимеры. Волокна. Каучуки. 10 класс. Сушилки для сушки сыпучих материалов. Барабанные сушилки и их применение в производстве тугоплавких силикатных материалов

Сушилки для сушки сыпучих материалов. Барабанные сушилки и их применение в производстве тугоплавких силикатных материалов Учим стихи по мнемотаблицам Колючие стихи

Учим стихи по мнемотаблицам Колючие стихи Интеллектуальная кормушка для рыб

Интеллектуальная кормушка для рыб Утилизация теплоты отходящих дымовых газов. Промышленная теплоэнергетика

Утилизация теплоты отходящих дымовых газов. Промышленная теплоэнергетика Набор № 3 ВС Щелочи. Техника безопасности при работе со щелочами

Набор № 3 ВС Щелочи. Техника безопасности при работе со щелочами Cursul universitar “Electrotehnică”

Cursul universitar “Electrotehnică” Сплавы. Металлы

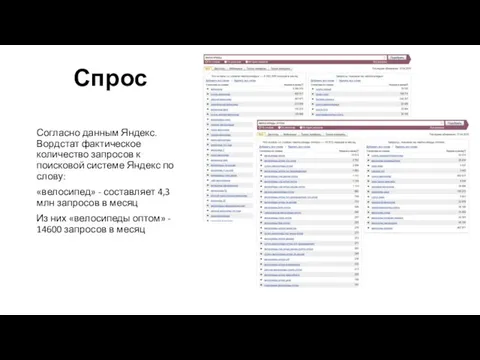

Сплавы. Металлы Спрос. Поисковая система Яндекс

Спрос. Поисковая система Яндекс История исследования России

История исследования России