Содержание

- 2. Якщо трансформувати затвор звичайного МОН транзистора таким чином, щоб в під затворному діелектрику міг зберігатися електричний

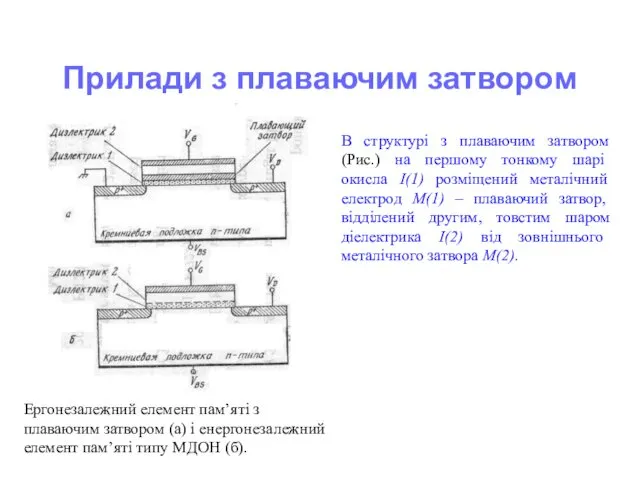

- 3. Прилади з плаваючим затвором Ергонезалежний елемент пам’яті з плаваючим затвором (а) і енергонезалежний елемент пам’яті типу

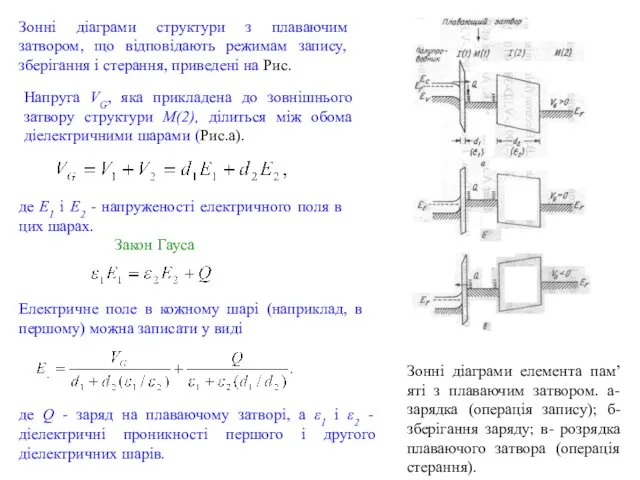

- 4. Зонні діаграми елемента пам’яті з плаваючим затвором. а- зарядка (операція запису); б- зберігання заряду; в- розрядка

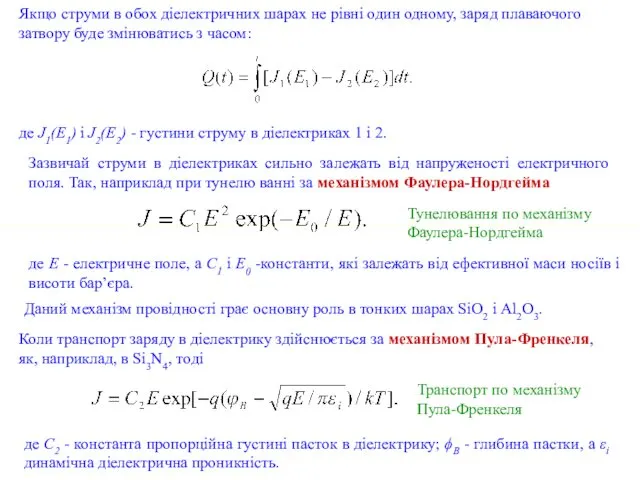

- 5. Тунелювання по механізму Фаулера-Нордгейма Транспорт по механізму Пула-Френкеля Якщо струми в обох діелектричних шарах не рівні

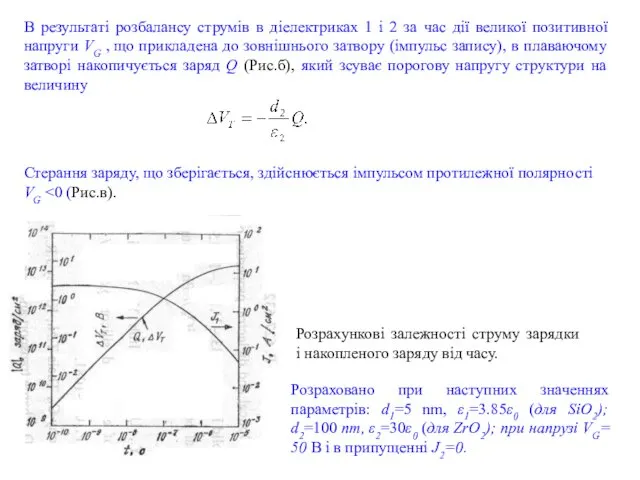

- 6. В результаті розбалансу струмів в діелектриках 1 і 2 за час дії великої позитивної напруги VG

- 7. Провідність каналу до (стан «0») і після (стан «1») виконання операції запису.

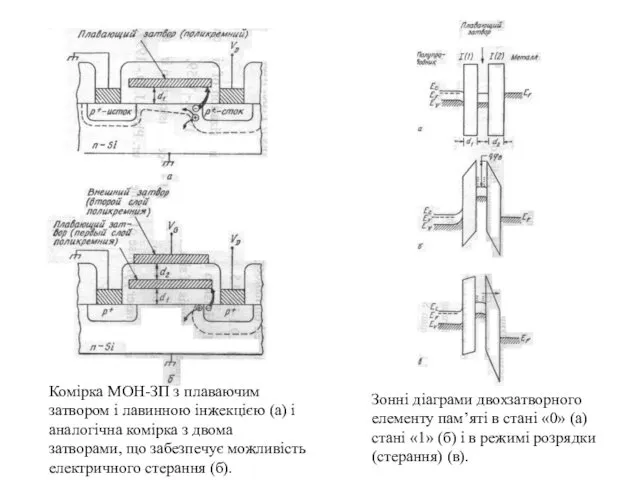

- 8. Комірка МОН-ЗП з плаваючим затвором і лавинною інжекцією (а) і аналогічна комірка з двома затворами, що

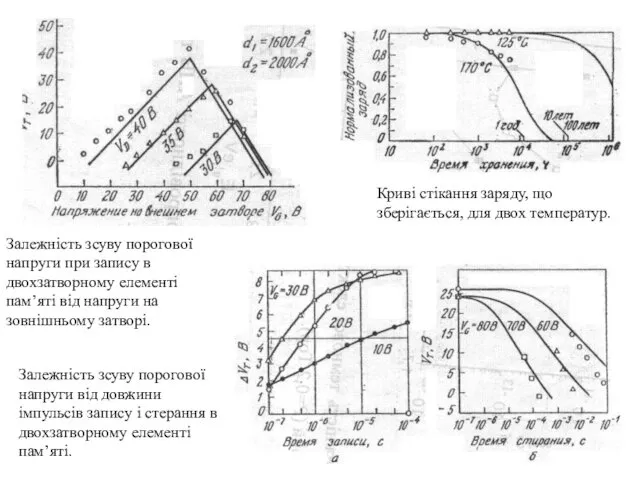

- 9. Залежність зсуву порогової напруги при запису в двохзатворному елементі пам’яті від напруги на зовнішньому затворі. Криві

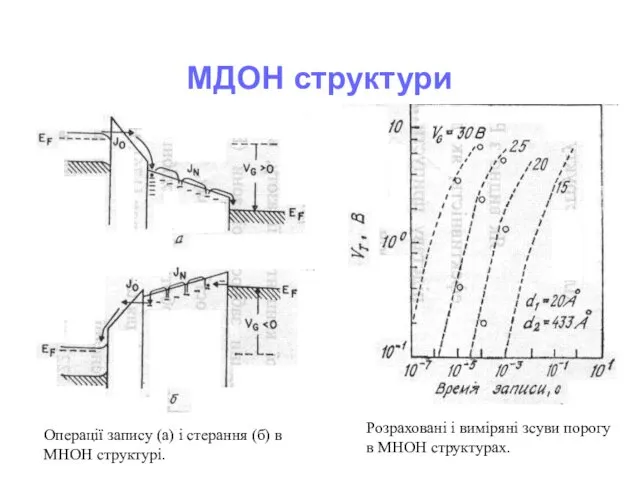

- 10. МДОН структури Операції запису (а) і стерання (б) в МНОН структурі. Розраховані і виміряні зсуви порогу

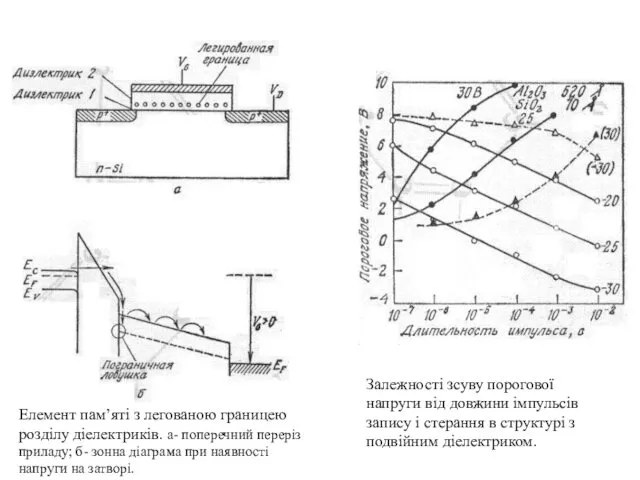

- 11. Елемент пам’яті з легованою границею розділу діелектриків. а- поперечний переріз приладу; б- зонна діаграма при наявності

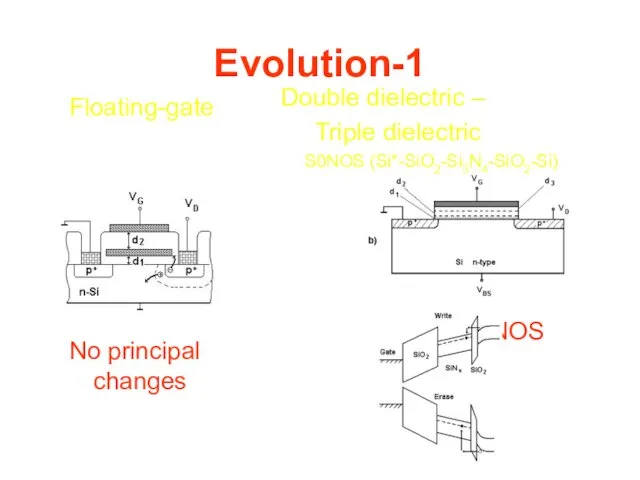

- 12. Evolution-1 Floating-gate No principal changes Double dielectric – Triple dielectric S0NOS (Si*-SiO2-Si3N4-SiO2-Si) SONOS

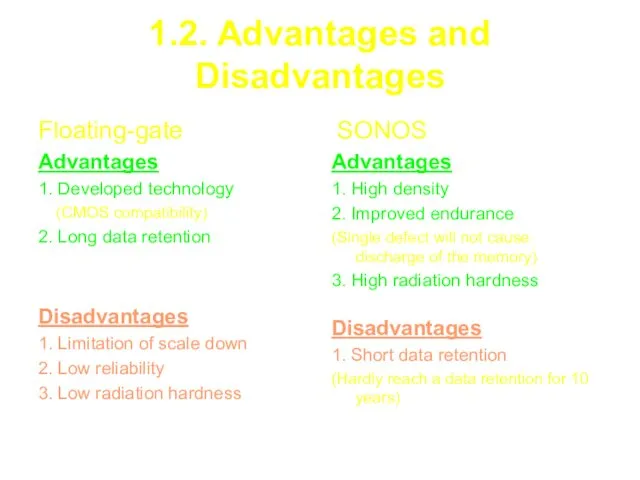

- 13. 1.2. Advantages and Disadvantages Floating-gate Advantages 1. Developed technology (CMOS compatibility) 2. Long data retention Disadvantages

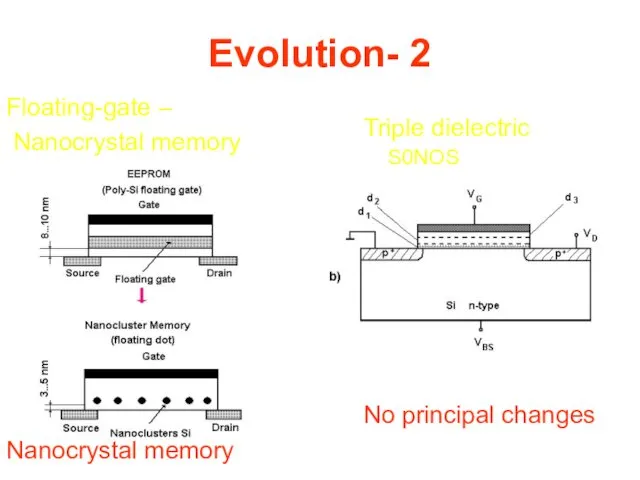

- 14. Evolution- 2 Floating-gate – Nanocrystal memory Nanocrystal memory Triple dielectric S0NOS No principal changes

- 15. 1.3. Nanocrystal memory Main idea: The continuous poly-Si Floating gate is replaced on discontinuous Si nanocrystals

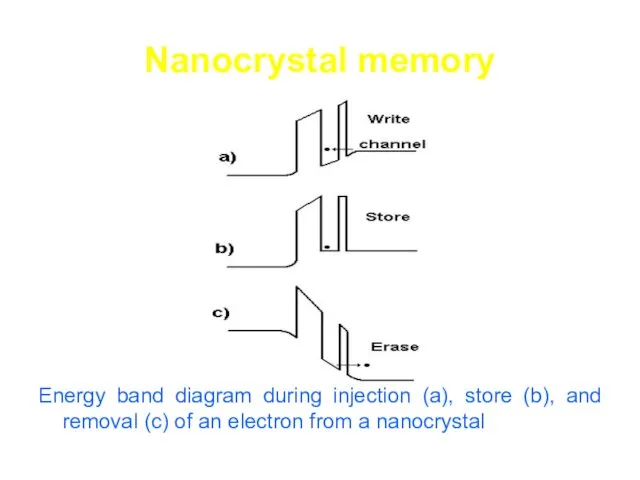

- 16. Nanocrystal memory Energy band diagram during injection (a), store (b), and removal (c) of an electron

- 17. 1.3.1. Why nanocrystal memory? 1. CMOS compatibility 2. High integrity (scaling down) 3. Faster (high speed

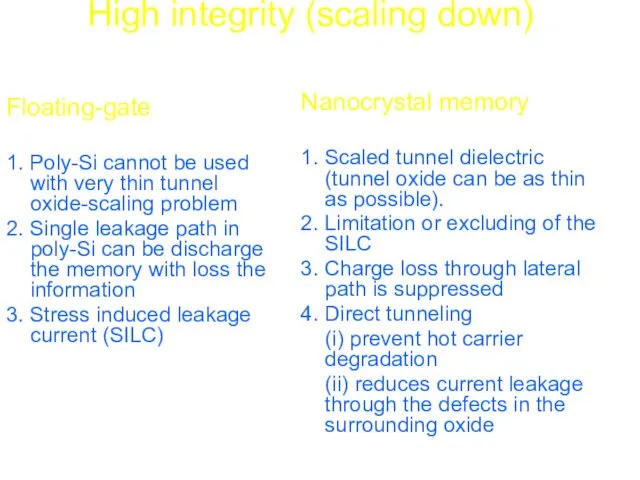

- 18. High integrity (scaling down) Floating-gate 1. Poly-Si cannot be used with very thin tunnel oxide-scaling problem

- 19. High stability / High reliability Failure No failure

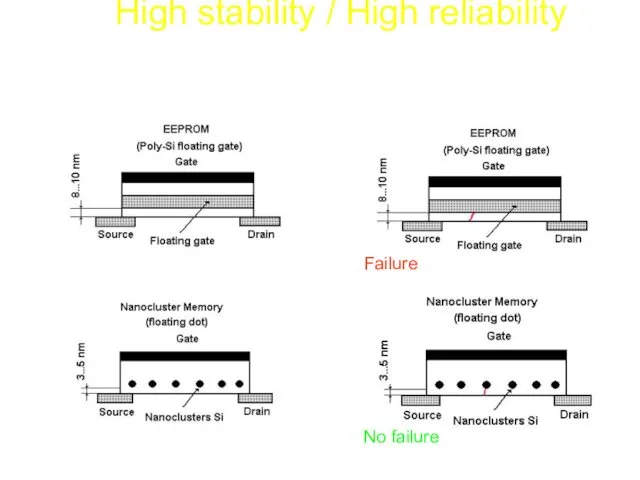

- 20. Low voltage operation / Consumption of lower power / Faster / Much smaller degradation / High

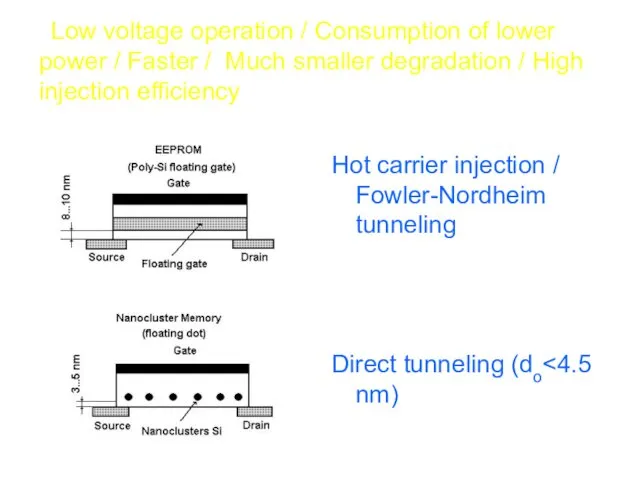

- 21. Fowler-Nordheim – Direct tinneling(1) Hot carrier injection (1) / Fowler-Nordheim tunneling (2) Direct tunneling (do

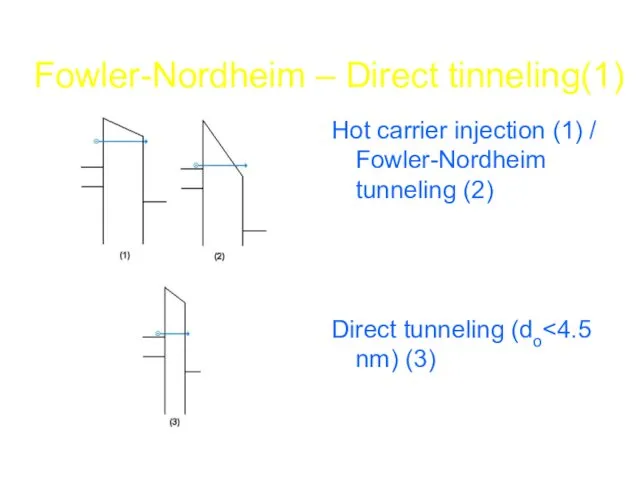

- 22. Fowler-Nordheim – Direct tinneling(2) Fowler-Nordheim tunneling Direct tunneling

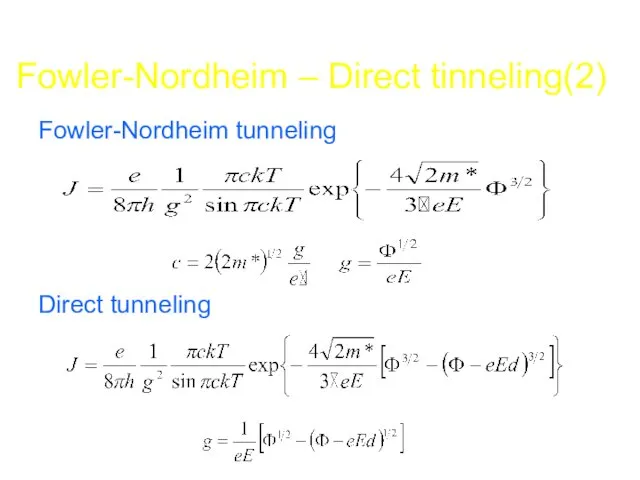

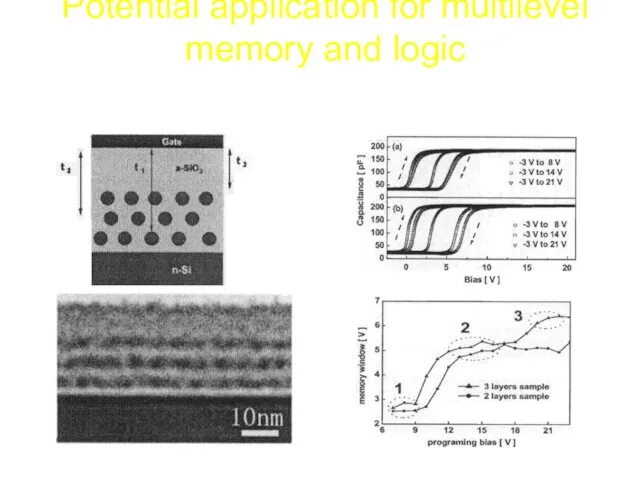

- 23. Potential application for multilevel memory and logic

- 24. Novel Si functional devices 1. Nanocrystal memory- quantum dot floating gate memory 2. Single electron transistors

- 25. Comparison of non-volatile memories EEPROM FN – Tunneling e- in floating gate dox~8…10 nm Vw/e~12…20 V

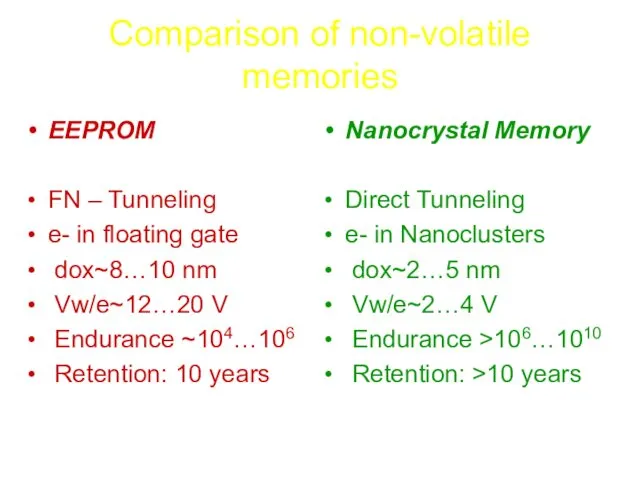

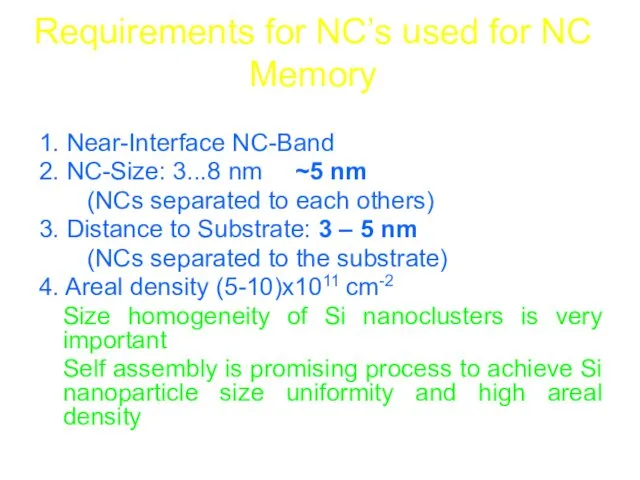

- 26. Requirements for NC’s used for NC Memory 1. Near-Interface NC-Band 2. NC-Size: 3...8 nm ~5 nm

- 27. Requirements for NC’s used for NC Memory Improved device performance and reliability depends upon: 1. Ability

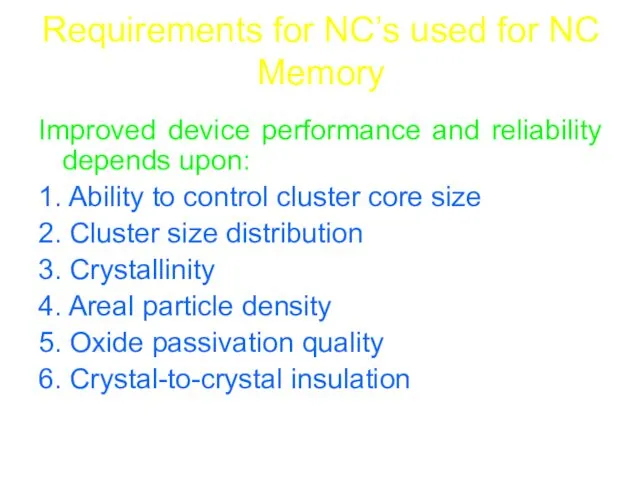

- 28. 1.3.2. New physics Quantum confinement effect 3- dimensional system (3D) 2- dimensional system (2D) 1- dimensional

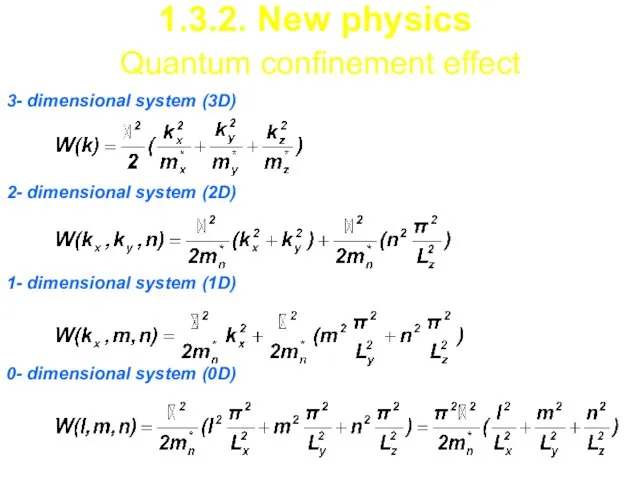

- 29. Quantum confinement effect

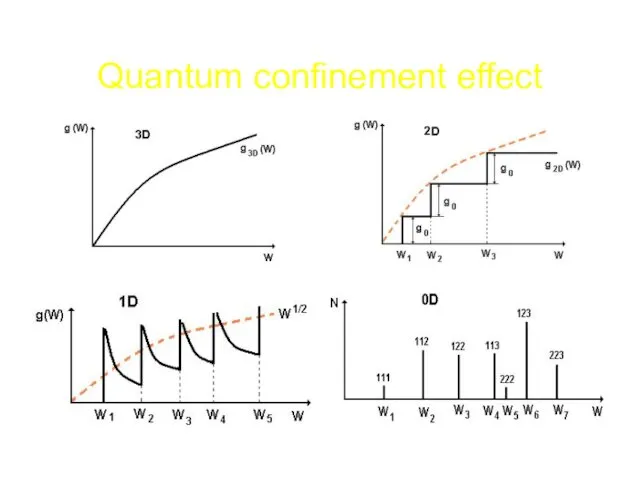

- 30. Quantum confinement effect Energy spectrum

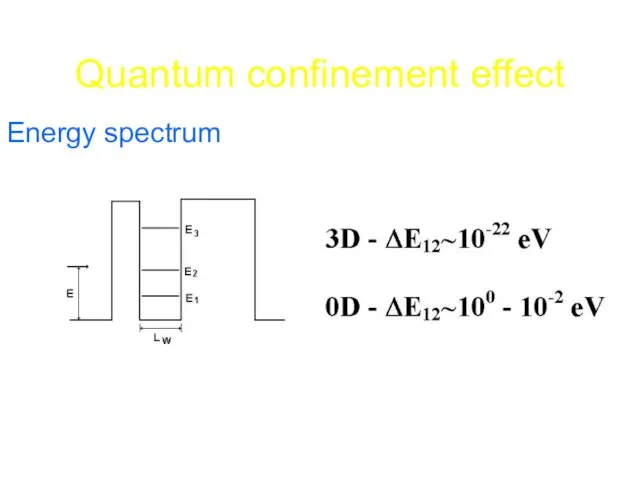

- 31. Quantum confinement effect In case of spherical nanoparticles (nanocrystals) Conclusion 1: Electron energy spectrum in quantum

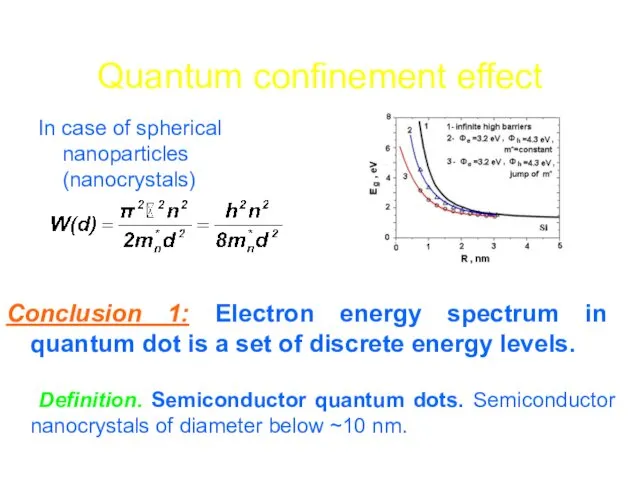

- 32. Coulomb blockade effect The effect of blocking the injection of a second charge into a semiconductor

- 33. Coulomb blockade effect [2]. I. Kim et al. Jpn. J. Appl. Phys..40, 447-451, 2001.

- 34. Coulomb blockade effect Conclusions 2. 1. The electrons already transferred to the nanocrystals block the transfer

- 35. Single electron transistor Quantum confinement effect + Coulomb blockade effect ___________________________ Single electron charging effects ___________________________

- 36. Single electron transistor Fabrication route of forming high-density of small and uniform in size nanocrystals is

- 37. 1.3.5. Parameters Vw/e~2…4 V Endurance >106…1010 Retention: >10 years

- 38. 1.4. Conclusions 1. Nanocrystal floating gate memory is a perspective candidate for the future scaled flash

- 40. Скачать презентацию

![Coulomb blockade effect [2]. I. Kim et al. Jpn. J. Appl. Phys..40, 447-451, 2001.](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/97530/slide-32.jpg)

Здоровье школьника - правильная осанка

Здоровье школьника - правильная осанка Ошибки в рекламе. Рекламное воздействие на потребителей. Словарь новейших слов иноязычной лексики

Ошибки в рекламе. Рекламное воздействие на потребителей. Словарь новейших слов иноязычной лексики презентация к классному часу Край мой родной, Забайкалье!

презентация к классному часу Край мой родной, Забайкалье! Broken heart

Broken heart Путешествие по Японии

Путешествие по Японии Органы внутренних дел Российской Федерации

Органы внутренних дел Российской Федерации Электронные генераторы

Электронные генераторы презентация Домашние животные

презентация Домашние животные Топливно-энергетический комплекс Иркутской области

Топливно-энергетический комплекс Иркутской области Правила поведения в школе

Правила поведения в школе Современный урок в условиях введения ФГОС

Современный урок в условиях введения ФГОС Проблемы адаптации детей в приюте.

Проблемы адаптации детей в приюте. Развитие творческих способностей у детей дошкольного возраста средствами театрализованной деятельности.

Развитие творческих способностей у детей дошкольного возраста средствами театрализованной деятельности. Основные определения, топологические параметры и методы расчета электрических цепей

Основные определения, топологические параметры и методы расчета электрических цепей Процесс обработки детали АКДП-150208-2020 11700.001 с применением станков с программным управлением

Процесс обработки детали АКДП-150208-2020 11700.001 с применением станков с программным управлением Текстовые задачи в ЕГЭ по математике

Текстовые задачи в ЕГЭ по математике Игровые технологии

Игровые технологии Ленталы конвейрдің автоматтандырылған электр жетегін өңдеу

Ленталы конвейрдің автоматтандырылған электр жетегін өңдеу Исследовательский проект Юный орнитолог, начальная школа

Исследовательский проект Юный орнитолог, начальная школа Цифровая камера

Цифровая камера Scanner and printer

Scanner and printer Знаменитости умершие от употребления наркотиков-1

Знаменитости умершие от употребления наркотиков-1 Избирательная система РФ

Избирательная система РФ Культура исламского Востока

Культура исламского Востока Россия - Родина моя

Россия - Родина моя Россия в Первой Мировой войне

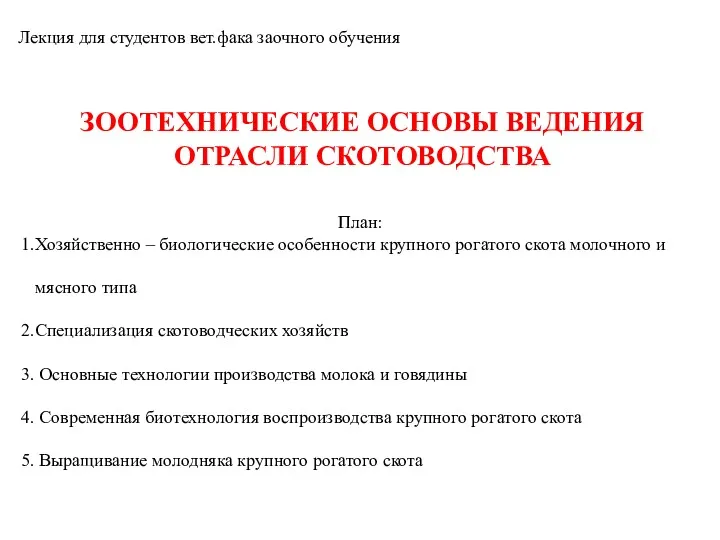

Россия в Первой Мировой войне Зоотехнические основы ведения отрасли скотоводства

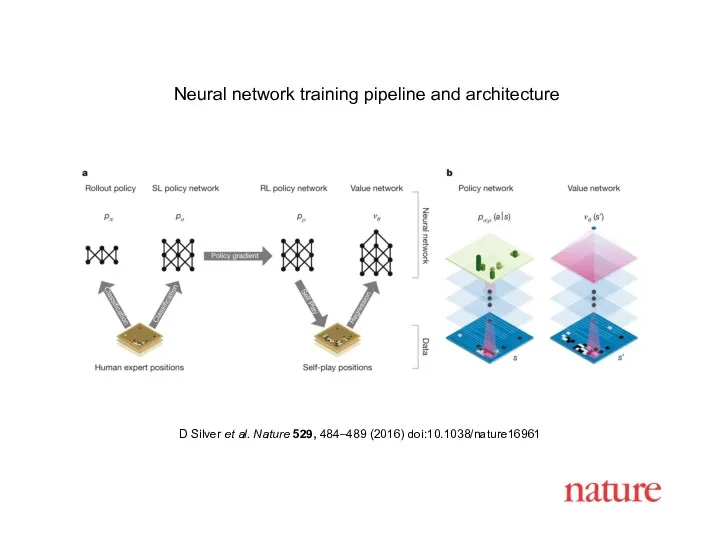

Зоотехнические основы ведения отрасли скотоводства Neural network training pipeline and architecture

Neural network training pipeline and architecture