Содержание

- 2. УЧЕБНЫЕ ВОПРОСЫ: 1. Программируемая логическая матрица (ПЛМ) 2. Программируемые логические интегральные схемы (ПЛИС) 3. Методика и

- 3. Контрольные вопросы Записать аналитическое выражение логической операции, нарисовать условно-графическое обозначение логического элемента, реализующего логическую функцию. 1

- 4. 1. Программируемая логическая матрица (ПЛМ)

- 5. Основные понятия и определения Программируемая логическая матрица представляет собой сетку ортогональных проводников (шин), в местах пересечения

- 6. Классификация 1. По способу программирования ПЛМ делят на: - матрицы, настраиваемые (программируемые) предприятием - изготовителем (М-матрицы);

- 7. Условное графическое обозначение

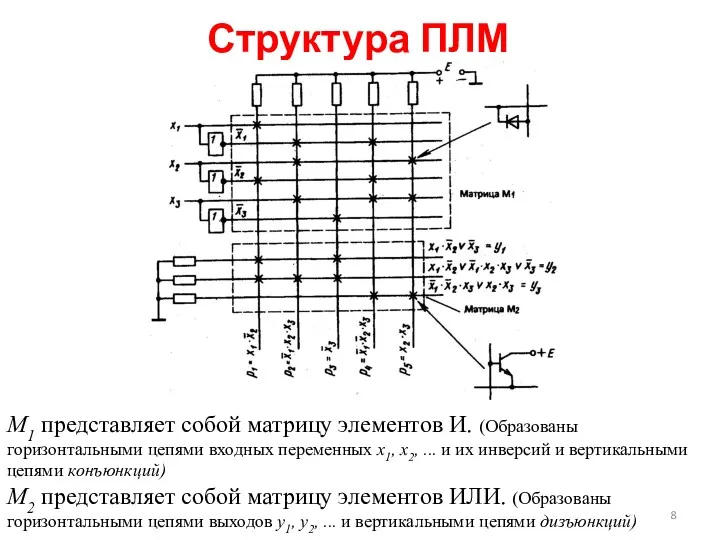

- 8. Структура ПЛМ М1 представляет собой матрицу элементов И. (Образованы горизонтальными цепями входных переменных x1, x2, ...

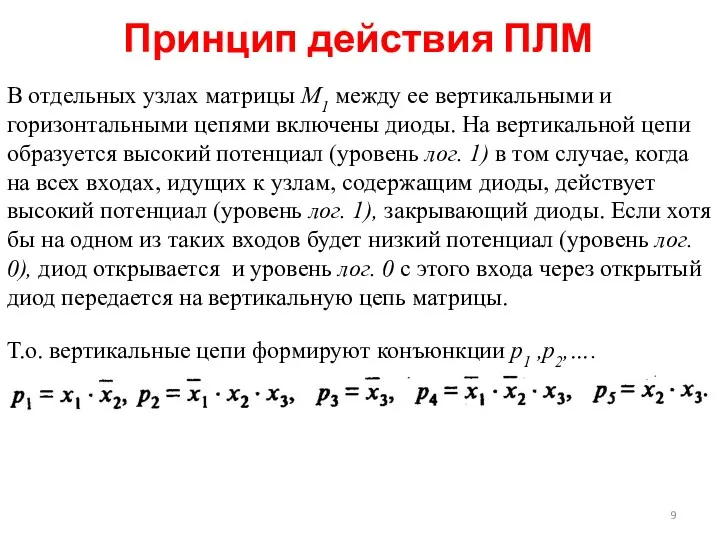

- 9. Принцип действия ПЛМ В отдельных узлах матрицы М1 между ее вертикальными и горизонтальными цепями включены диоды.

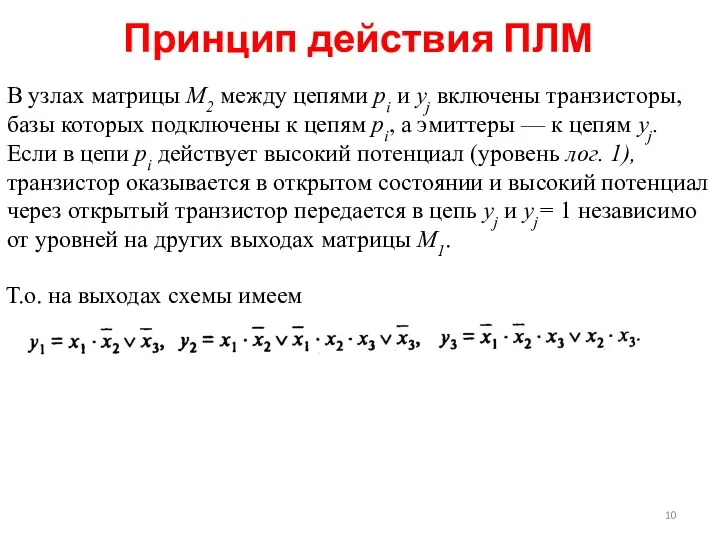

- 10. Принцип действия ПЛМ В узлах матрицы М2 между цепями рi и уj включены транзисторы, базы которых

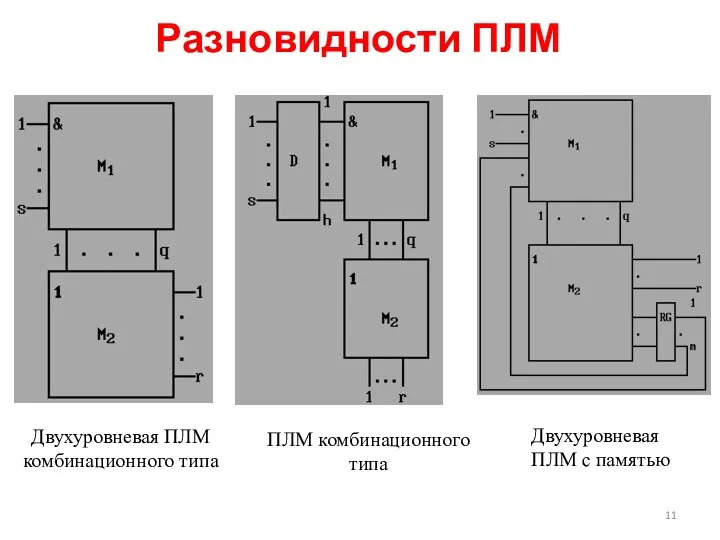

- 11. Разновидности ПЛМ Двухуровневая ПЛМ комбинационного типа ПЛМ комбинационного типа Двухуровневая ПЛМ с памятью

- 12. 1. ПЛМ является универсальным цифровым устройством, позволяющим реализовать логические функции различной сложности Вывод по 1 вопросу

- 13. 2. Программируемые логические интегральные схемы (ПЛИС)

- 14. Основные понятия и определения ПЛИС — это матричные большие интегральные схемы Назначение. ПЛИС позволяют программно скомпоновать

- 15. 1. По типу программируемых элементов: однократно программируемые (транзисторы с перемычками типа antifuse, с программированием плавающих затворов);

- 16. Микросхема ПЛИС имеет в своём составе память для хранения конфигурации (в ПЛИС EPLD используется ППЗУ с

- 17. серии ХС7200 и ХС7300 — типа EPLD. Содержат от 18 до 144 многовходовых макроячеек, представляющих собой

- 18. 1. Технология ПЛИС обеспечивает рекордно короткий проектно-технологический цикл (от нескольких часов до нескольких дней), минимальные затраты

- 19. 3. Методика и средства проектирования ЦУ

- 20. Основные понятия и определения Проектирование — разработка технической документации, позволяющей изготовить заданное устройство в заданных условиях.

- 21. Основные понятия и определения Выбор наилучшего варианта при синтезе осуществляется по результатам анализа (проверяется правильность работы

- 22. Классификация цифровых ИС с точки зрения методов проектирования

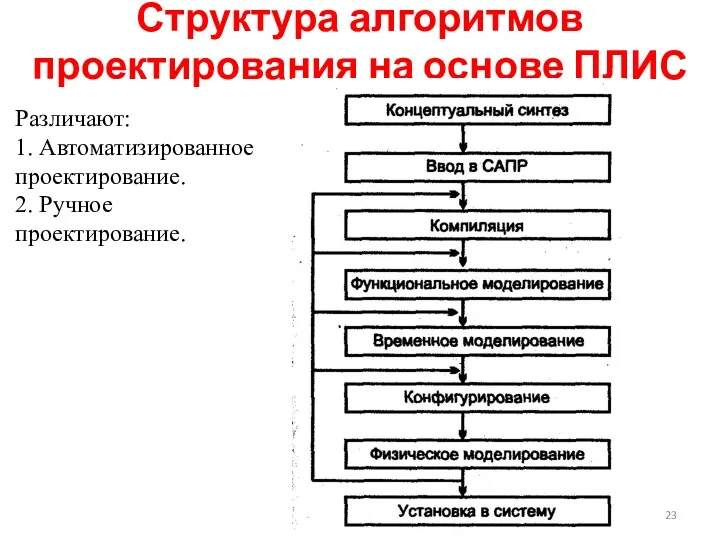

- 23. Структура алгоритмов проектирования на основе ПЛИС Различают: 1. Автоматизированное проектирование. 2. Ручное проектирование.

- 24. При проектировании цифрового устройства либо ручным либо автоматизированным способом всегда придерживаются определённого алгоритма Вывод по 3

- 26. Скачать презентацию

ВПР в начальной школе: методика проверки заданий по русскому языку

ВПР в начальной школе: методика проверки заданий по русскому языку Конспект урока математики: Действия с положительными и отрицательными числами, 6 класс

Конспект урока математики: Действия с положительными и отрицательными числами, 6 класс 20191102_summa_uglov_treugolnika

20191102_summa_uglov_treugolnika Джек Лондон. Роман Маленькая хозяйка большого дома

Джек Лондон. Роман Маленькая хозяйка большого дома Сословно-представительная монархия XVII века в России, в условиях внешних вызовов и внутренних угроз

Сословно-представительная монархия XVII века в России, в условиях внешних вызовов и внутренних угроз Волонтерский отряд Лесная братва

Волонтерский отряд Лесная братва Графический редактор Adobe PhotoShop

Графический редактор Adobe PhotoShop Патофизиология и ее место среди медико-биологических и клинических наук

Патофизиология и ее место среди медико-биологических и клинических наук Социальная психология общения

Социальная психология общения Публикация в социальных сетях Интернета и вывод результата на бумажный носитель

Публикация в социальных сетях Интернета и вывод результата на бумажный носитель Рухомий склад метрополітену. Загальний курс метрополітену. Відділ експлуатації та безпеки руху. Тема № 3

Рухомий склад метрополітену. Загальний курс метрополітену. Відділ експлуатації та безпеки руху. Тема № 3 Иудаизм.Время возникновения

Иудаизм.Время возникновения Возможности электронного журнала

Возможности электронного журнала Ильменский заповедник

Ильменский заповедник План-конспект занятия Оберег-домовушка

План-конспект занятия Оберег-домовушка Наглядные пособия на уроке природоведения.

Наглядные пособия на уроке природоведения. Человеческий капитал и персональные компетенции как основа образования современного коммуникатора

Человеческий капитал и персональные компетенции как основа образования современного коммуникатора Презентация Использование нестандартного оборудования на занятиях по физической культуре

Презентация Использование нестандартного оборудования на занятиях по физической культуре Гендерный подход в формировании интереса к художественным произведениям у детей дошкольного возраста

Гендерный подход в формировании интереса к художественным произведениям у детей дошкольного возраста Экономика и дошкольник.

Экономика и дошкольник. Тема 9. Эффективность производственно-хозяйственной деятельности

Тема 9. Эффективность производственно-хозяйственной деятельности Мастер-класс Подарок для мамы

Мастер-класс Подарок для мамы Как можно ускорить экономический рост.

Как можно ускорить экономический рост. Производство вторичной гранулы полипропилена, ООО Кияна Пласт

Производство вторичной гранулы полипропилена, ООО Кияна Пласт Медицина в Древнем Египте

Медицина в Древнем Египте Сопряжения линий в геометрических построениях

Сопряжения линий в геометрических построениях Оборудование по теме Порошки

Оборудование по теме Порошки Теорема Виета

Теорема Виета