Содержание

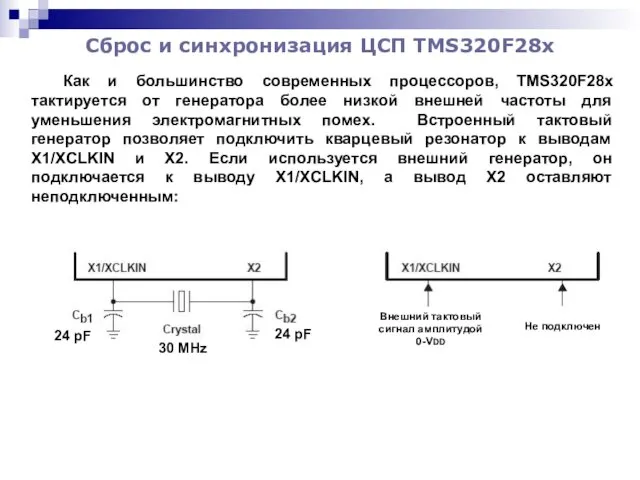

- 2. Сброс и синхронизация ЦСП TMS320F28x Как и большинство современных процессоров, TMS320F28x тактируется от генератора более низкой

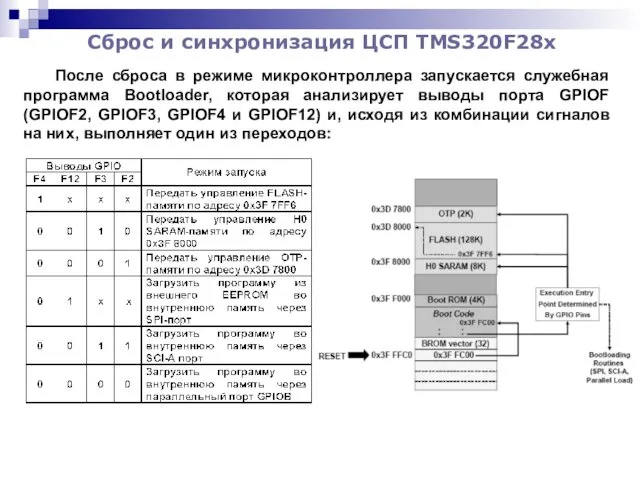

- 3. Сброс и синхронизация ЦСП TMS320F28x После сброса в режиме микроконтроллера запускается служебная программа Bootloader, которая анализирует

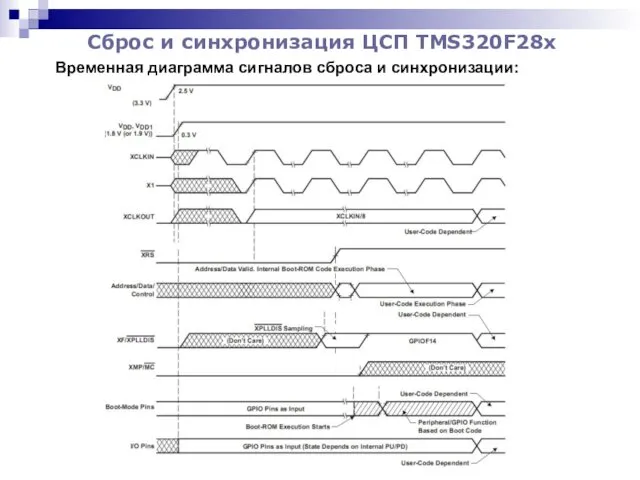

- 4. Сброс и синхронизация ЦСП TMS320F28x Временная диаграмма сигналов сброса и синхронизации:

- 5. Сброс и синхронизация ЦСП TMS320F28x Внутренние сигналы синхронизации DSP TMS320F2812: (PLL запрещен) Встроенный генератор (OSC)

- 6. Сброс и синхронизация ЦСП TMS320F28x Модуль фазовой синхронизации (PLL – Phase-Locked Loop) задает внутреннюю частоту DSP.

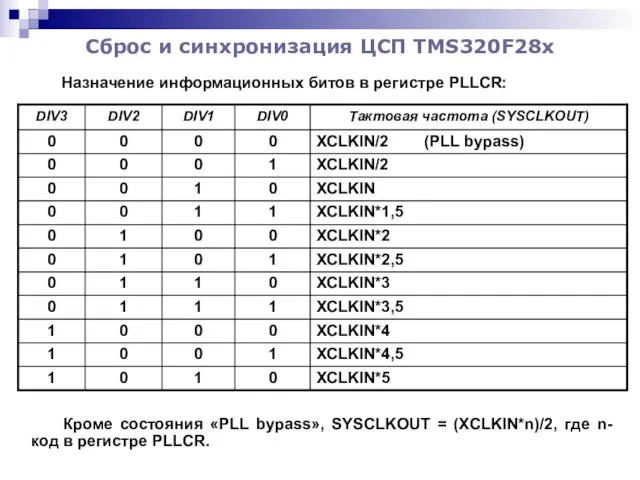

- 7. Сброс и синхронизация ЦСП TMS320F28x Кроме состояния «PLL bypass», SYSCLKOUT = (XCLKIN*n)/2, где n- код в

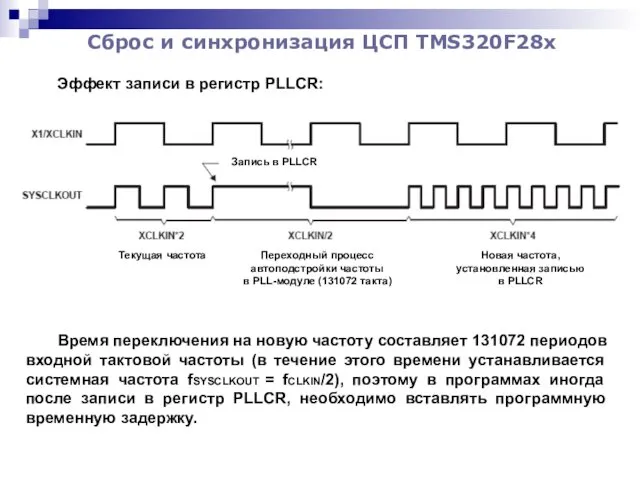

- 8. Сброс и синхронизация ЦСП TMS320F28x Эффект записи в регистр PLLCR: Время переключения на новую частоту составляет

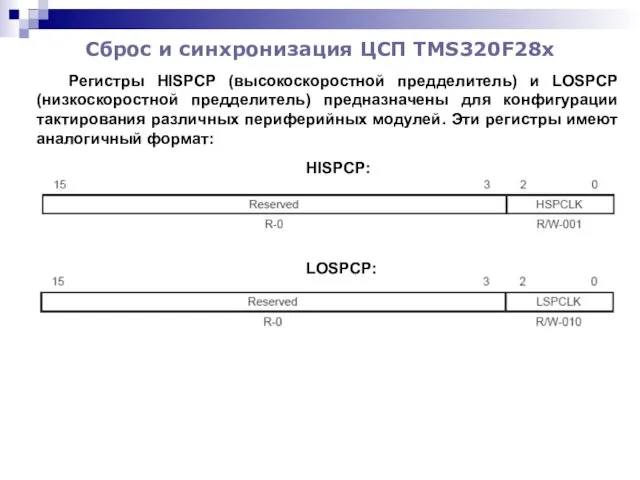

- 9. Сброс и синхронизация ЦСП TMS320F28x Регистры HISPCP (высокоскоростной предделитель) и LOSPCP (низкоскоростной предделитель) предназначены для конфигурации

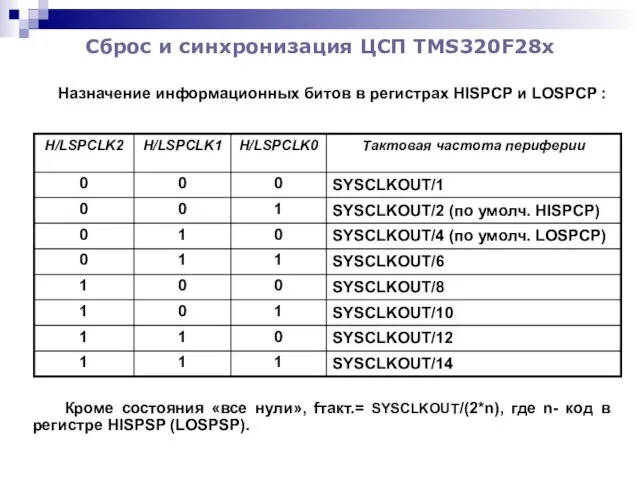

- 10. Сброс и синхронизация ЦСП TMS320F28x Назначение информационных битов в регистрах HISPCP и LOSPCP : Кроме состояния

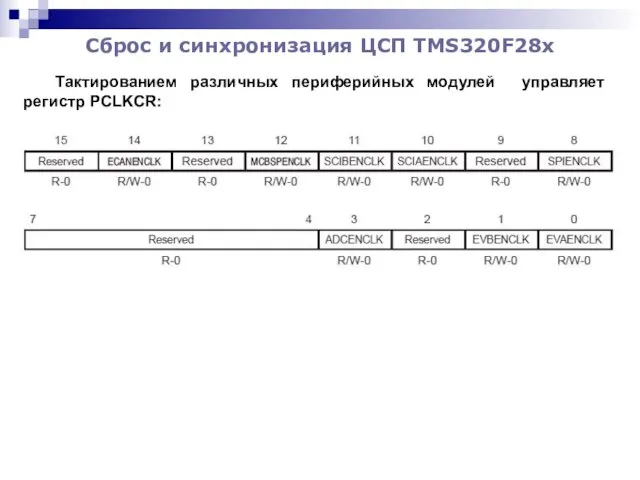

- 11. Сброс и синхронизация ЦСП TMS320F28x Тактированием различных периферийных модулей управляет регистр PCLKCR:

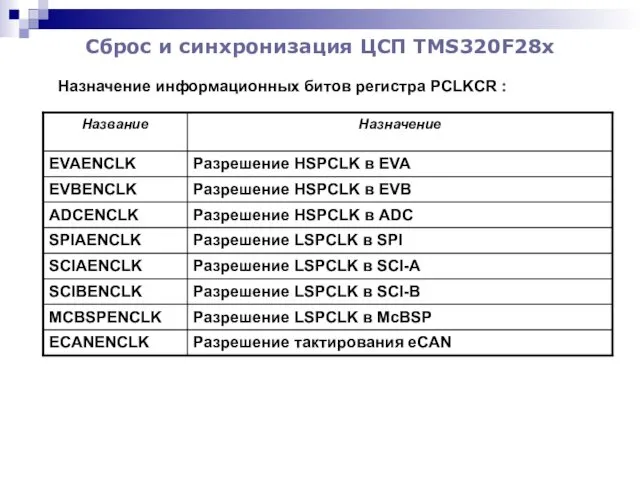

- 12. Сброс и синхронизация ЦСП TMS320F28x Назначение информационных битов регистра PCLKCR :

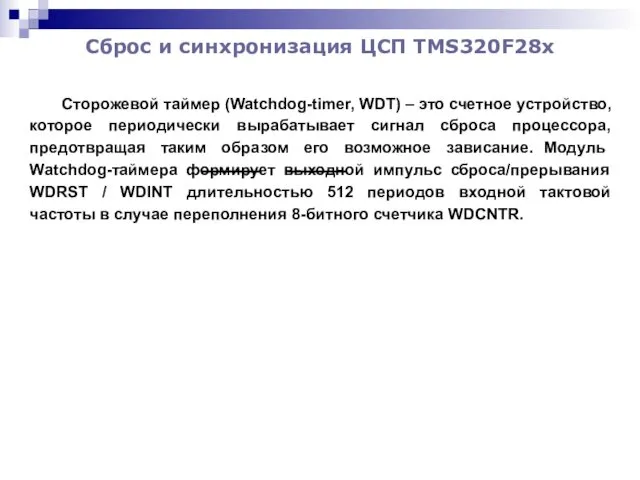

- 13. Сброс и синхронизация ЦСП TMS320F28x Сторожевой таймер (Watchdog-timer, WDT) – это счетное устройство, которое периодически вырабатывает

- 14. Сброс и синхронизация ЦСП TMS320F28x Функциональная схема модуля WDT:

- 15. Сброс и синхронизация ЦСП TMS320F28x Для предотвращения сброса процессора необходимо периодически программно сбрасывать счетчик WDCNTR при

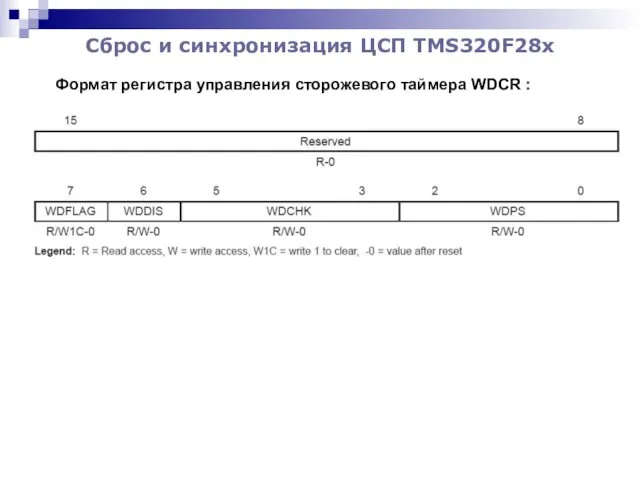

- 16. Сброс и синхронизация ЦСП TMS320F28x Формат регистра управления сторожевого таймера WDCR :

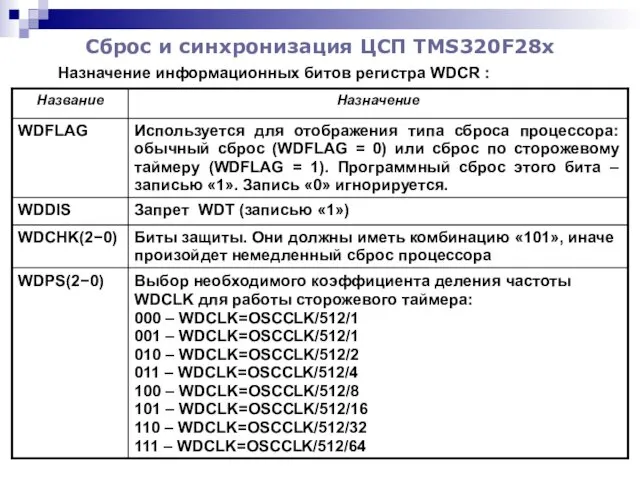

- 17. Сброс и синхронизация ЦСП TMS320F28x Назначение информационных битов регистра WDCR :

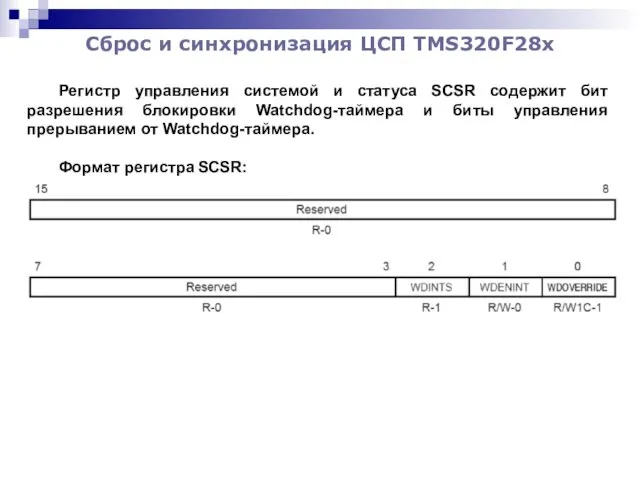

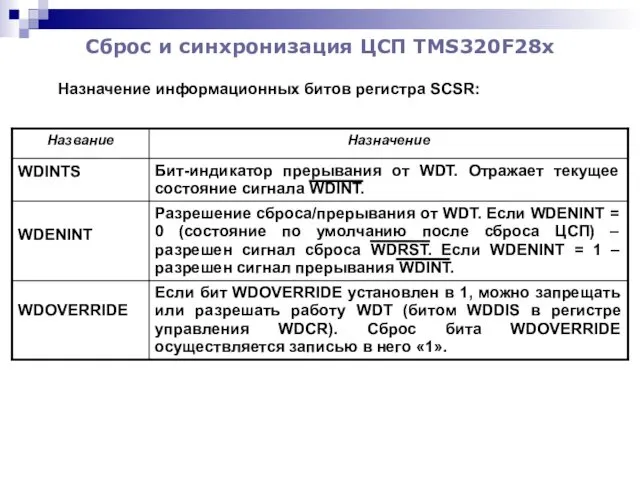

- 18. Сброс и синхронизация ЦСП TMS320F28x Регистр управления системой и статуса SCSR содержит бит разрешения блокировки Watchdog-таймера

- 19. Сброс и синхронизация ЦСП TMS320F28x

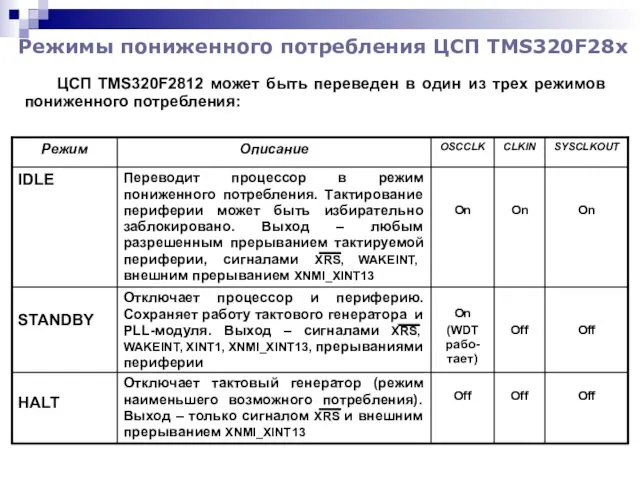

- 20. Режимы пониженного потребления ЦСП TMS320F28x ЦСП TMS320F2812 может быть переведен в один из трех режимов пониженного

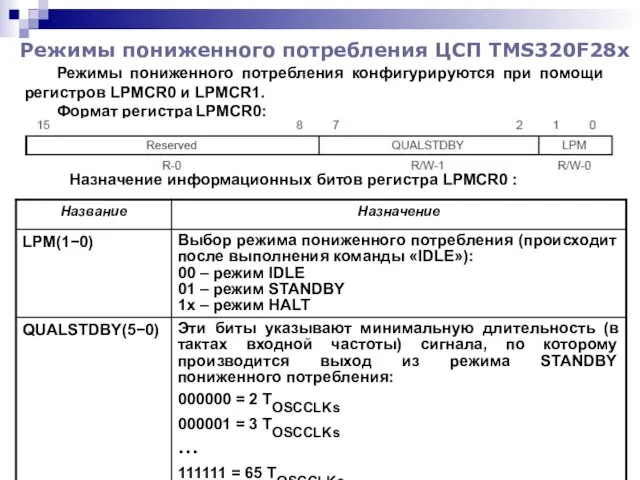

- 21. Режимы пониженного потребления ЦСП TMS320F28x Режимы пониженного потребления конфигурируются при помощи регистров LPMCR0 и LPMCR1. Формат

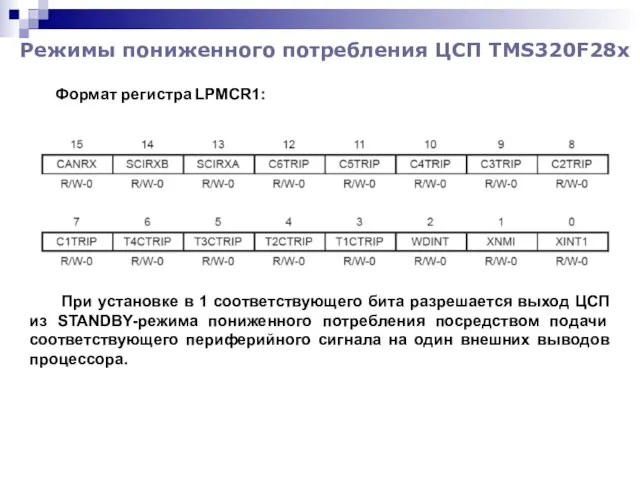

- 22. Режимы пониженного потребления ЦСП TMS320F28x Формат регистра LPMCR1: При установке в 1 соответствующего бита разрешается выход

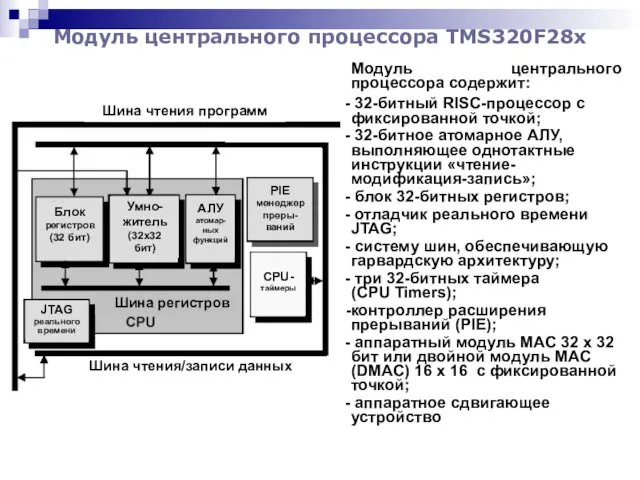

- 23. Модуль центрального процессора TMS320F28x Модуль центрального процессора содержит: - 32-битный RISC-процессор с фиксированной точкой; - 32-битное

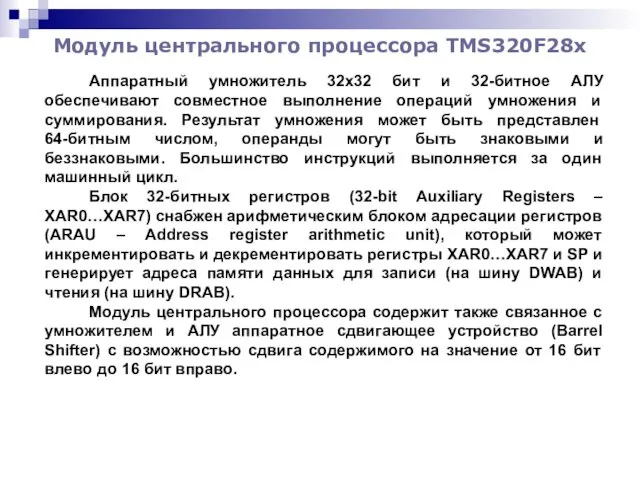

- 24. Модуль центрального процессора TMS320F28x Аппаратный умножитель 32x32 бит и 32-битное АЛУ обеспечивают совместное выполнение операций умножения

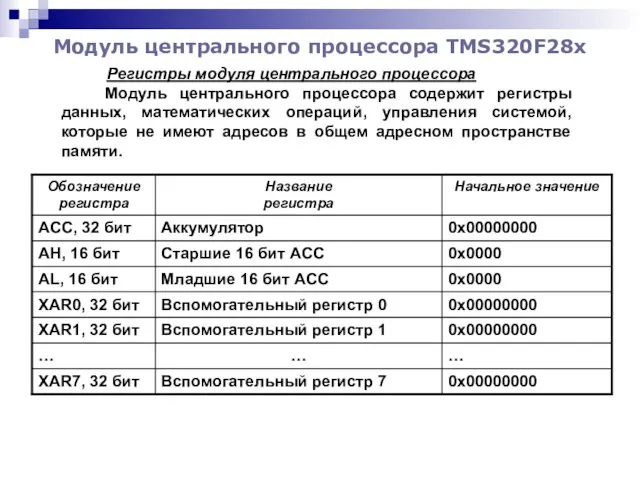

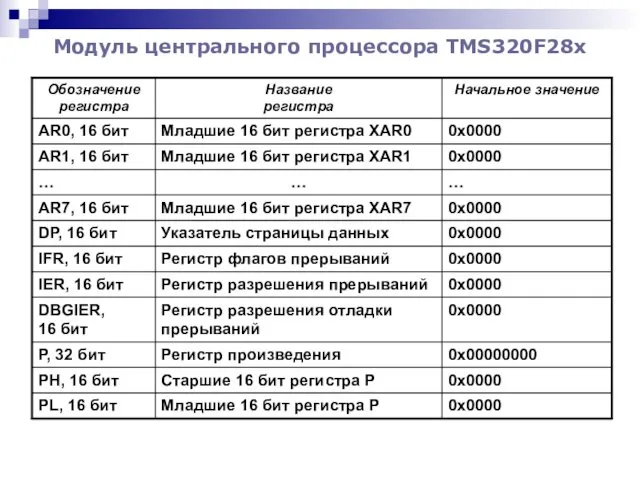

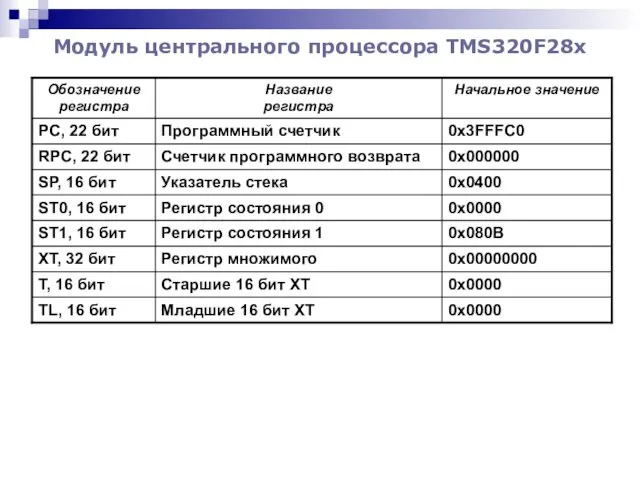

- 25. Модуль центрального процессора TMS320F28x Регистры модуля центрального процессора Модуль центрального процессора содержит регистры данных, математических операций,

- 26. Модуль центрального процессора TMS320F28x

- 27. Модуль центрального процессора TMS320F28x

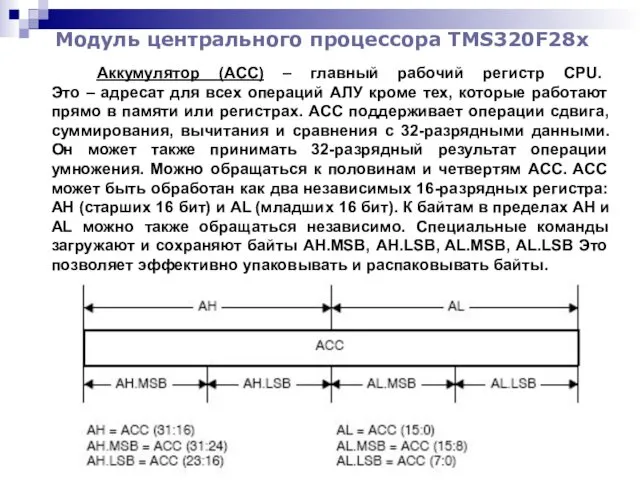

- 28. Модуль центрального процессора TMS320F28x Аккумулятор (ACC) – главный рабочий регистр CPU. Это – адресат для всех

- 30. Скачать презентацию

Право собственности и другие вещные права на жилые помещения. Общее имущество собственников помещений многоквартирного дома

Право собственности и другие вещные права на жилые помещения. Общее имущество собственников помещений многоквартирного дома Ресторанная управляющая и консалтинговая компания RestoStart

Ресторанная управляющая и консалтинговая компания RestoStart Рекомендации по выполнению курсовой работы: основы экономики и управления фармацевтическим производством

Рекомендации по выполнению курсовой работы: основы экономики и управления фармацевтическим производством Бланк документа

Бланк документа Семинар для воспитателей Введения ФГОС в городе Москве

Семинар для воспитателей Введения ФГОС в городе Москве адаптация первоклассника в школе

адаптация первоклассника в школе Своя игра. Общая биология

Своя игра. Общая биология Подземный урбанизм

Подземный урбанизм Терапия наночастицами: новый способ лечения рака

Терапия наночастицами: новый способ лечения рака Строительство жилого дома переменной этажности в г. Череповце

Строительство жилого дома переменной этажности в г. Череповце презентация для подготовки к ЕГЭ по обществознанию. Блок Политология

презентация для подготовки к ЕГЭ по обществознанию. Блок Политология Модели психики и интеллекта человека

Модели психики и интеллекта человека Лепим пряники

Лепим пряники Создание собственного медиа-пространства на всех платформах социальных сетей

Создание собственного медиа-пространства на всех платформах социальных сетей История и работа музейной комнаты школы №44

История и работа музейной комнаты школы №44 Создание изделий из текстильных материалов. Производство текстильных материалов

Создание изделий из текстильных материалов. Производство текстильных материалов Разбор заданий ЕГЭ по русскому языку (информационная обработка текстов, орфоэпические, лексические нормы, орфография)

Разбор заданий ЕГЭ по русскому языку (информационная обработка текстов, орфоэпические, лексические нормы, орфография) Книжная выставка Подвиг Сталинграда

Книжная выставка Подвиг Сталинграда Религии мира

Религии мира 20230416_na_rmo_vystuplenie

20230416_na_rmo_vystuplenie Пасха. Символы Пасхи

Пасха. Символы Пасхи Прощальная беседа Иисуса Христа с учениками

Прощальная беседа Иисуса Христа с учениками Катетеризация центральных вен

Катетеризация центральных вен The common cold

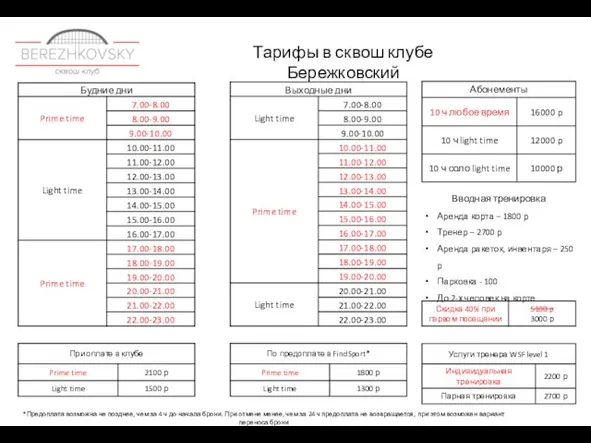

The common cold Тарифы, сертификаты и объявления

Тарифы, сертификаты и объявления Сбалансированная система показателей (BSC). Группы компаний ПРОТЕК

Сбалансированная система показателей (BSC). Группы компаний ПРОТЕК Почему трудно определиться с выбором будущей профессии?

Почему трудно определиться с выбором будущей профессии? Энергосбережение в строительстве. Япония

Энергосбережение в строительстве. Япония