Содержание

- 2. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. SDR (Single Data Rate) SDRAM SDRAM (Synchronous DRAM)

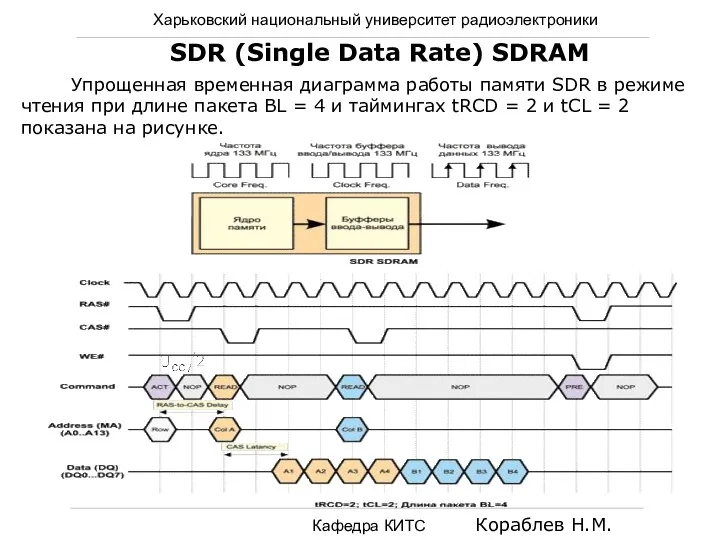

- 3. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. SDR (Single Data Rate) SDRAM Упрощенная временная диаграмма

- 4. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. DDR (Double Data Rate) SDRAM DDR SDRAM –

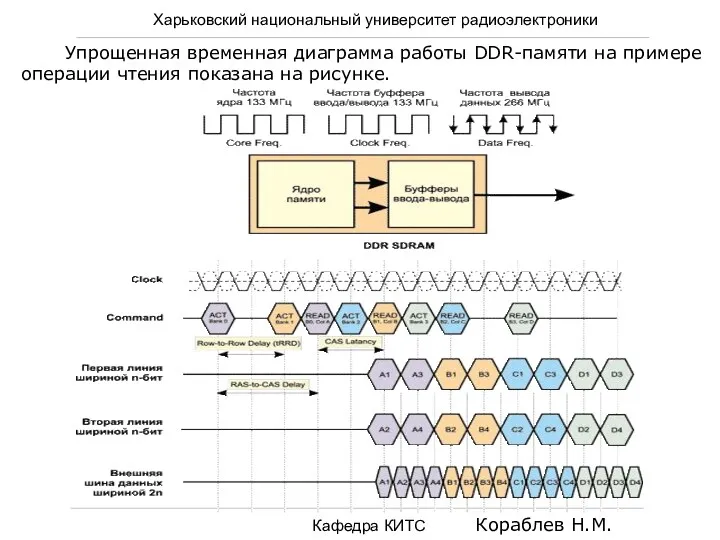

- 5. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Упрощенная временная диаграмма работы DDR-памяти на примере операции

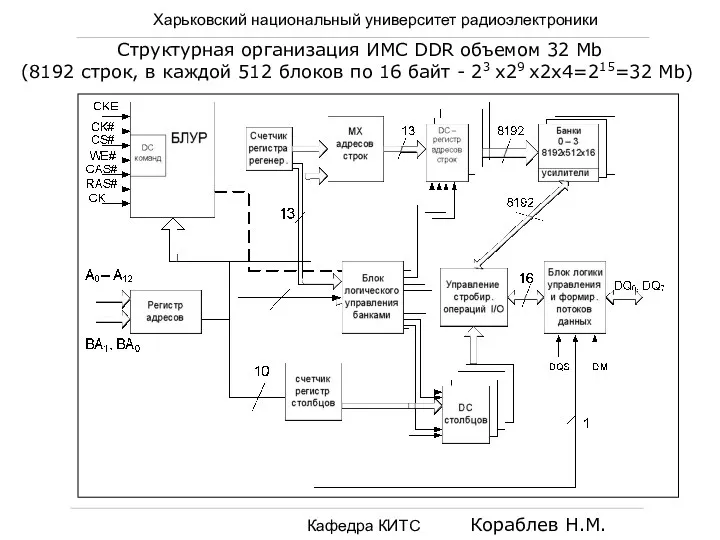

- 6. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Структурная организация ИМС DDR объемом 32 Mb (8192

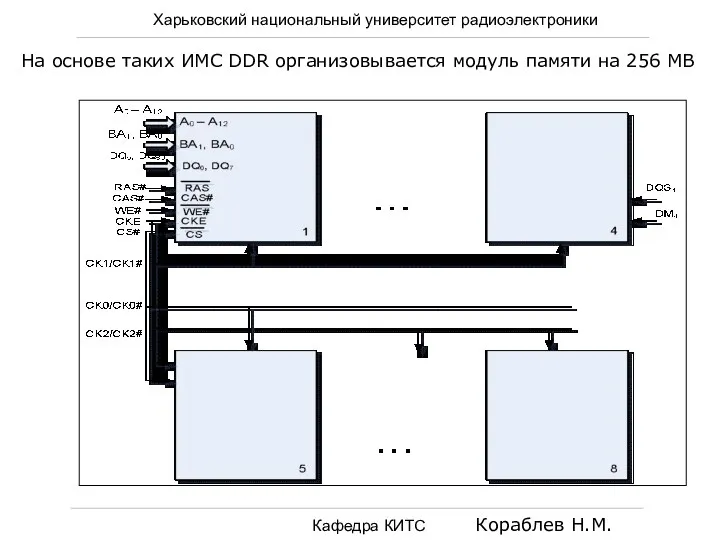

- 7. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. На основе таких ИМС DDR организовывается модуль памяти

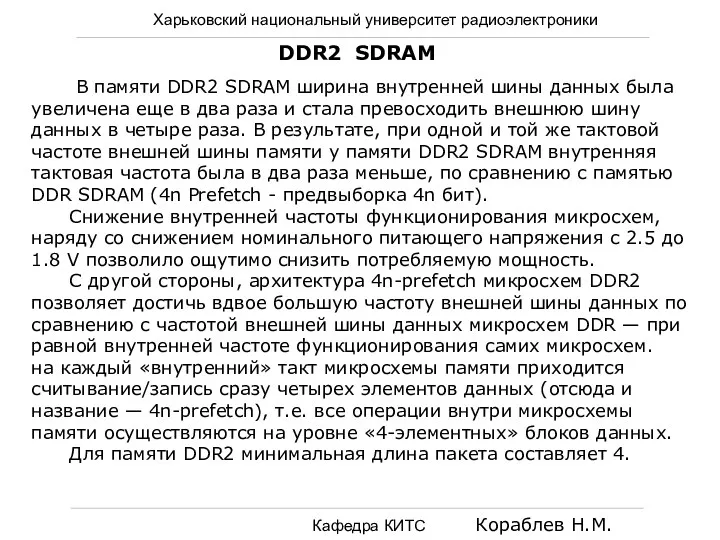

- 8. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. DDR2 SDRAM В памяти DDR2 SDRAM ширина внутренней

- 9. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Упрощенная временная диаграмма работы DDR2-памяти на примере операции

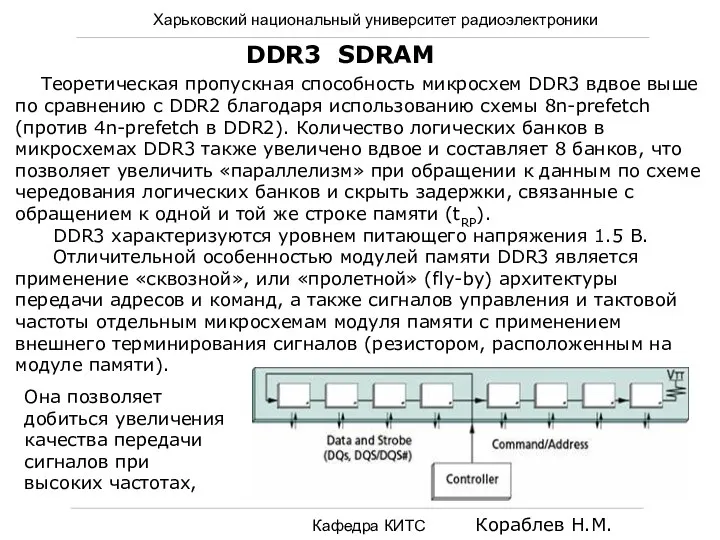

- 10. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. DDR3 SDRAM Теоретическая пропускная способность микросхем DDR3 вдвое

- 11. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. DDR3 SDRAM В модулях памяти DDR2 подача адресов

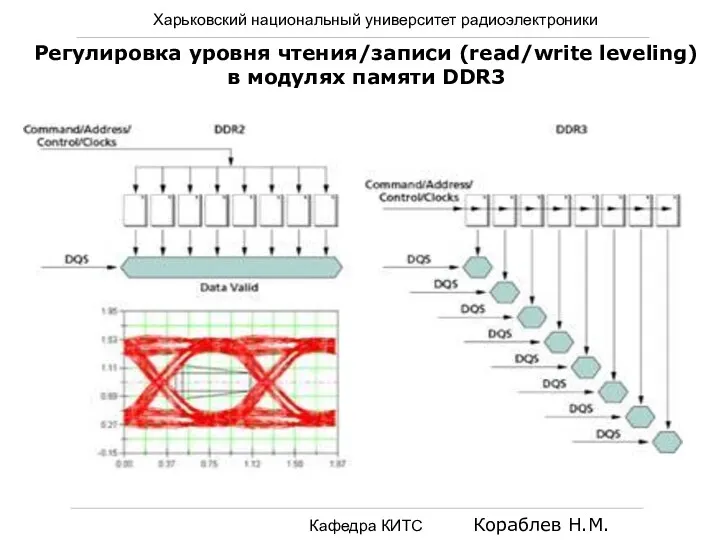

- 12. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Регулировка уровня чтения/записи (read/write leveling) в модулях памяти

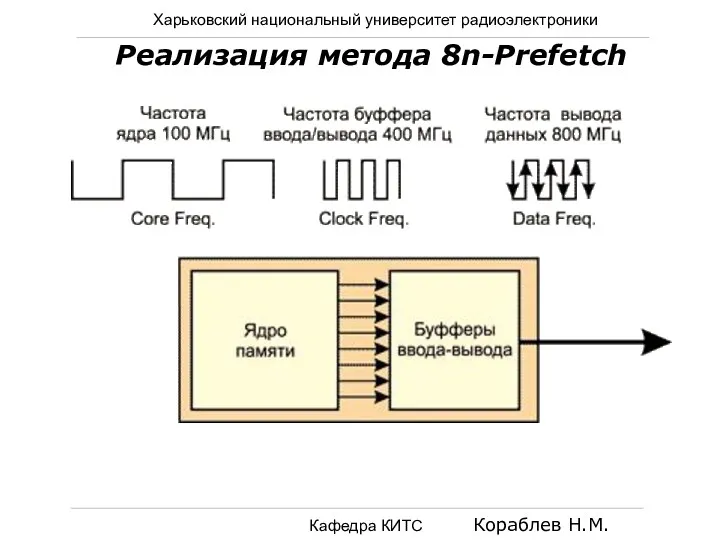

- 13. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Реализация метода 8n-Prefetch

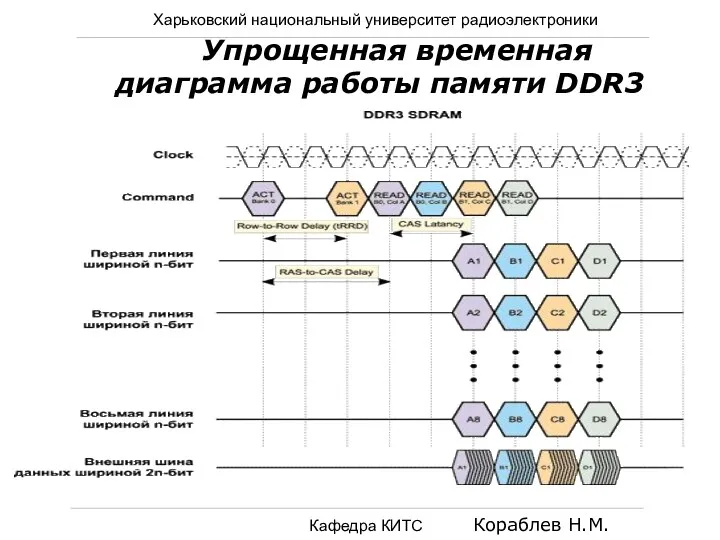

- 14. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Упрощенная временная диаграмма работы памяти DDR3

- 15. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Структурная схема микросхем памяти DDR3 объемом 1Г байт

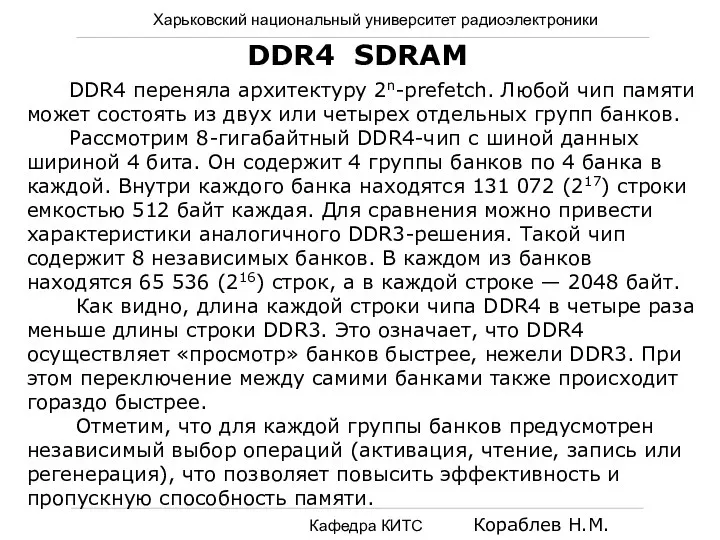

- 16. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. DDR4 SDRAM DDR4 переняла архитектуру 2n-prefetch. Любой чип

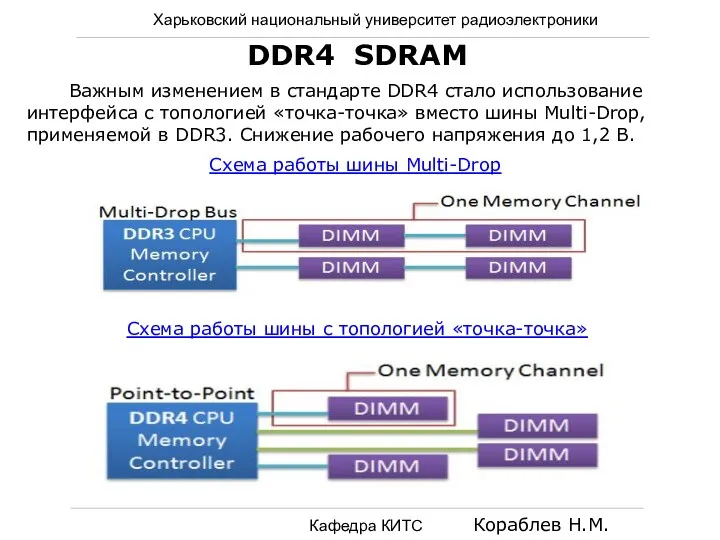

- 17. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. DDR4 SDRAM Важным изменением в стандарте DDR4 стало

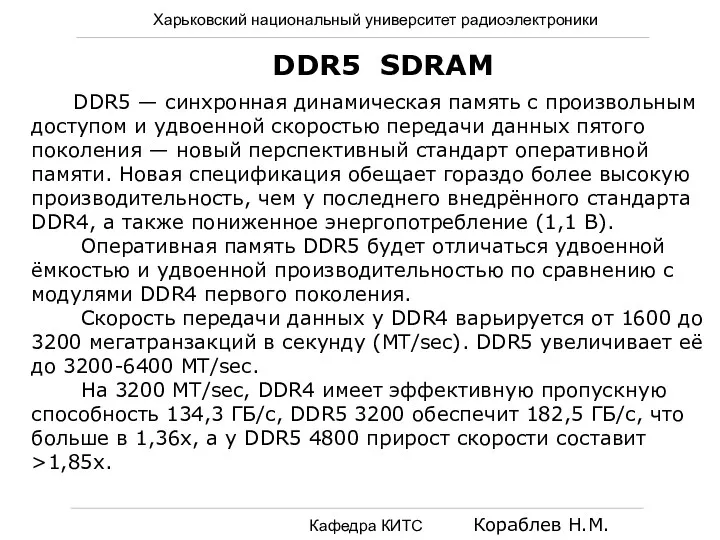

- 18. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. DDR5 SDRAM DDR5 — синхронная динамическая память с

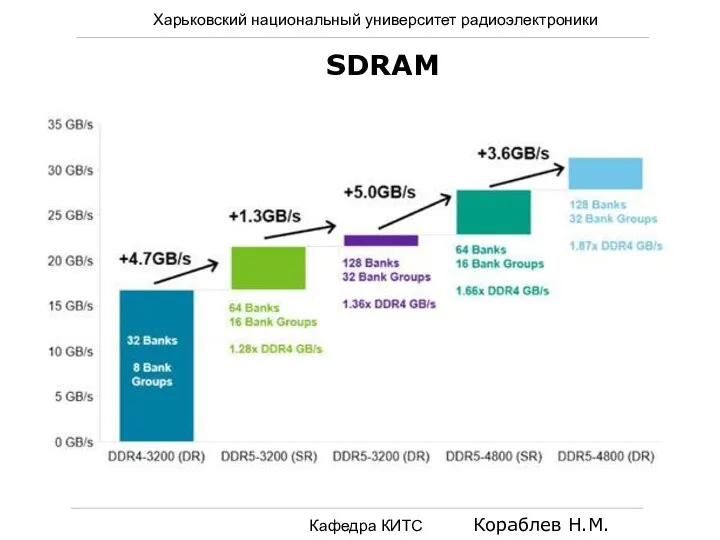

- 19. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. SDRAM

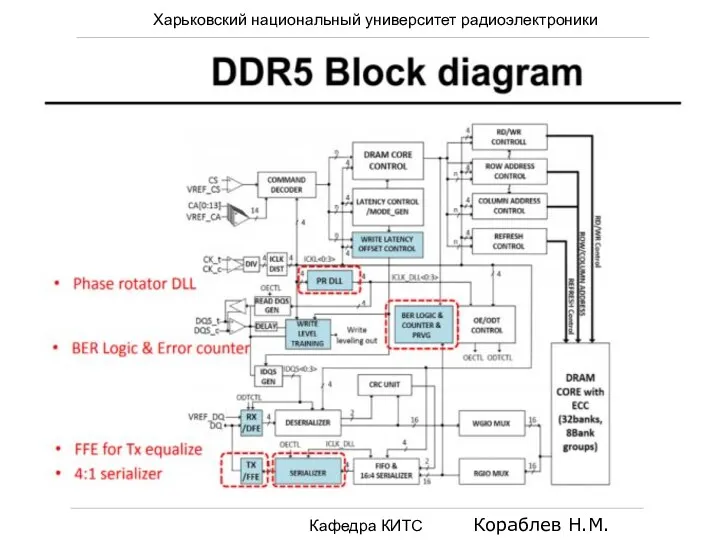

- 20. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М.

- 21. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. SDRAM

- 23. Скачать презентацию

Монтаж оборудования на объектах с особыми условиями. Лекция 35

Монтаж оборудования на объектах с особыми условиями. Лекция 35 Проект В мире сказки

Проект В мире сказки “Эпидемилогиялық диагноз”түсінігінің методологиялық негізі

“Эпидемилогиялық диагноз”түсінігінің методологиялық негізі Окуджава Булат Шалвович (1924 – 1997)

Окуджава Булат Шалвович (1924 – 1997) Запрошуємо на службу в поліції на вакантні посади до підрозділів головного управління національної поліції в одеській області

Запрошуємо на службу в поліції на вакантні посади до підрозділів головного управління національної поліції в одеській області Неотложная помощь при травмах и кровотечениях

Неотложная помощь при травмах и кровотечениях Основные понятия в области качества. Потребительские свойства

Основные понятия в области качества. Потребительские свойства Презентация о моей работе

Презентация о моей работе Решение неравенств

Решение неравенств Общественно-политические движения

Общественно-политические движения Оборудование лесопильного производства. Лесопильные рамы. Назначение, классификация, конструктивные особенности

Оборудование лесопильного производства. Лесопильные рамы. Назначение, классификация, конструктивные особенности Кәмелетке толмағандар арасындағы алкоголизм және онымен күресу жолдары

Кәмелетке толмағандар арасындағы алкоголизм және онымен күресу жолдары Логические транзисторы

Логические транзисторы Выращивание и уход за цветочным растением Лобелия

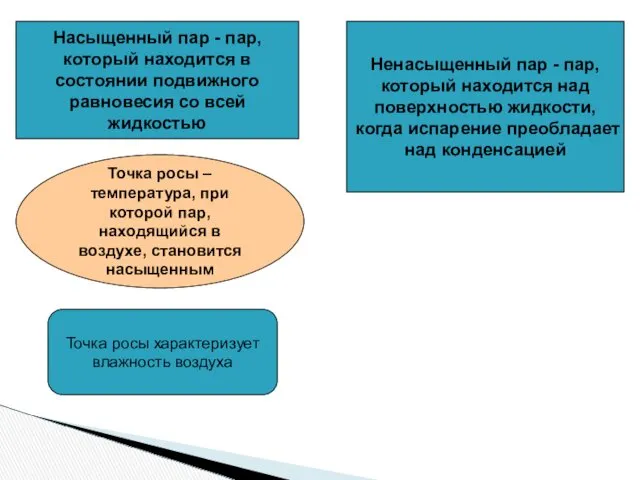

Выращивание и уход за цветочным растением Лобелия Насыщенный пар. Точка росы

Насыщенный пар. Точка росы Взрыв мозга

Взрыв мозга Ivan Shishkin

Ivan Shishkin Технология производства сыра

Технология производства сыра Лекция №12 РБ. Основные способы защиты человека от радиации

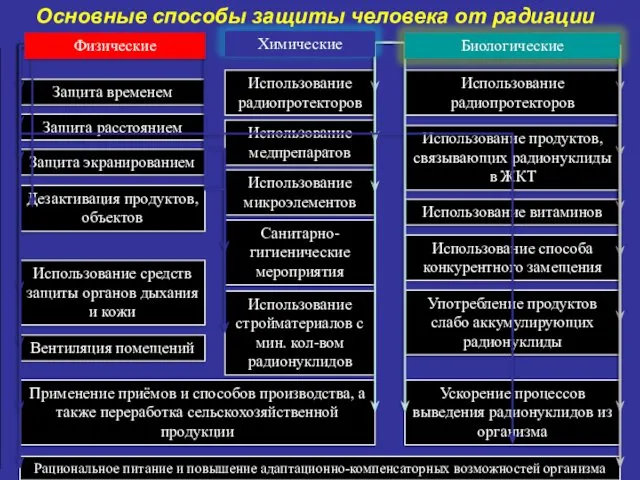

Лекция №12 РБ. Основные способы защиты человека от радиации OLED (органический светодиод ) дисплеи

OLED (органический светодиод ) дисплеи Либеральные реформы 60—70-х гг. XIX в

Либеральные реформы 60—70-х гг. XIX в Энциклопедия для малышей в сказках

Энциклопедия для малышей в сказках Экономическое регулирование в области охраны окружающей среды. (Лекция 4)

Экономическое регулирование в области охраны окружающей среды. (Лекция 4) Ислам дінін насихаттауға арналған маддах өлеңдер

Ислам дінін насихаттауға арналған маддах өлеңдер Наукăпа тĕпчев ĕçĕ: Тăван ялăм çинчен сăмахăм

Наукăпа тĕпчев ĕçĕ: Тăван ялăм çинчен сăмахăм Ад батлейкі - да тэатра

Ад батлейкі - да тэатра Роль школьного музея в духовно-нравственном воспитании обучающихся

Роль школьного музея в духовно-нравственном воспитании обучающихся Презентация 1 к уроку История родины в творчестве А.Булычева

Презентация 1 к уроку История родины в творчестве А.Булычева