Содержание

- 2. Учебные вопросы: 1. Система и форматы команд. 2. Способы адресации процессоров

- 3. 1. Система и форматы команд

- 4. ПА А1 А2 А3 Вариант структуры команды КОП Адресная часть команды Операционная часть КОП - ПА

- 5. Команда – это машинное слово определенной разрядности, задающее действие ЭВМ (прежде всего процессора) по выполнению конкретной

- 6. ТИПОВАЯ СТРУКТУРА КОМАНДЫ КОП (код операции) – определяет, какую операцию должен выполнить процессор Содержит адрес места

- 7. или ТИПОВАЯ СТРУКТУРА КОМАНДЫ ПА Возможны дополнительные элементы в структуре команды (обычно в адресной, реже –

- 8. ОПРЕДЕЛЕНИЕ РАЗРЯДНОСТИ КОМАНДЫ Lк = Lкоп + Lач Lкоп ≥ log2 Nоп Lач ≥ log2 Nяп

- 9. Трехадресная Двухадресная РАЗНОВИДНОСТИ КОМАНД Безадресная Одноадресная А1, А2 – адреса первого и второго операндов; А3 –

- 10. Операнд 1 Стек ЗУ (Поместить операнд 1 в стек) (Поместить операнд 2 в стек) (Поместить операнд

- 11. ВЫВОДЫ: Реализация в ЭВМ команд тех или иных форматов требует учета ряда факторов: затрат времени на

- 12. 2. Способы адресации процессоров

- 13. С целью сокращения длины команды в современных ЭВМ выполняются различные манипуляции адресом, именуемые режимами адресации, способами

- 14. Непосредственная адресация В команде находится операнд Прямая адресация ВИДЫ И СУЩНОСТЬ АДРЕСАЦИЙ Адресация со смещением Косвенная

- 15. Непосредственная адресация ВАРИАНТОВ НЕ ИМЕЕТ Прямая адресация ВОЗМОЖНЫЕ ВАРИАНТЫ ОТДЕЛЬНЫХ СПОСОБОВ АДРЕСАЦИИ Адресация со смещением РЕГИСТРОВАЯ

- 16. КОП Операц. часть А д р е с н а я ч а с т ь

- 17. Особенности реализации и применения адресации

- 18. Особенности реализации и применения непосредственной адресации не адресует вообще не обеспечивается наивысшее не обеспечивается

- 19. КОП Операц. часть А д р е с н а я ч а с т ь

- 20. Особенности реализации и применения прямой адресации ограничивается обеспечивается высокое не обеспечивается

- 21. КОП Операц. часть А д р е с н а я ч а с т ь

- 22. Особенности реализации и применения регистровой адресации не адресует обеспечивается высокое не обеспечивается

- 23. КОП Операц. часть А д р е с н а я ч а с т ь

- 24. Особенности реализации и применения косвенной регистровой адресации не ограничивается обеспечивается низкое не обеспечивается

- 25. Адресация со смещением БАЗОВАЯ ИНДЕКСНАЯ БАЗОВО-ИНДЕКСНАЯ ОТНОСИТЕЛЬНАЯ АВТОИНКРЕМЕНТНАЯ АВТОДЕКРЕМЕНТНАЯ

- 26. +1 КОП Операц. часть А д р е с н а я ч а с т

- 27. АВТОДЕКРЕМЕНТНАЯ АДРЕСАЦИЯ

- 28. Особенности реализации и применения автоинкрементной (автодекрементной) адресации не ограничивается обеспечивается высокое обеспечивается

- 29. СУЩНОСТЬ БАЗИРОВАНИЯ Начальный адрес массива Конечный адрес массива Массив данных a Адрес i-го элемента массива Смещение

- 30. КОП Операц. часть А д р е с н а я ч а с т ь

- 31. БАЗОВАЯ АДРЕСАЦИЯ (склеивание, конкатенация)

- 32. Особенности реализации и применения базовой адресации не ограничивается обеспечивается низкое обеспечивается

- 33. СУЩНОСТЬ ИНДЕКСАЦИИ База B Смещение D Массив Структура команды ЗУ ЗУ X=1 X=2 X=3 X=n База

- 34. КОП Операц. часть А д р е с н а я ч а с т ь

- 35. Особенности реализации и применения базово-индексной адресации не ограничивается обеспечивается низкое обеспечивается

- 37. Скачать презентацию

Роль профессиональных умений педагога в воспитании дошкольников

Роль профессиональных умений педагога в воспитании дошкольников Системы отопления. Техническая презентация для проектных и обслуживающих организаций

Системы отопления. Техническая презентация для проектных и обслуживающих организаций Необычные растения и животные в природе.

Необычные растения и животные в природе. Горьковский автомобильный завод (ГАЗ)

Горьковский автомобильный завод (ГАЗ) Рыбы - типичные водные животные.Строение рыб. Приспособление к водному образу жизни

Рыбы - типичные водные животные.Строение рыб. Приспособление к водному образу жизни Концепция ландшфтно-экологической ниши

Концепция ландшфтно-экологической ниши 20231015_master-klass

20231015_master-klass ФГОС дошкольного образования в коррекционной работе учителя-логопеда

ФГОС дошкольного образования в коррекционной работе учителя-логопеда Методика прогнозирования масштабов заражения сильнодействующими ядовитыми веществами при авариях

Методика прогнозирования масштабов заражения сильнодействующими ядовитыми веществами при авариях Защитные сооружения гражданской обороны. Сооружения защитные ГО и их классификация

Защитные сооружения гражданской обороны. Сооружения защитные ГО и их классификация Ходовое оборудование строительных машин. Общие сведения и классификация

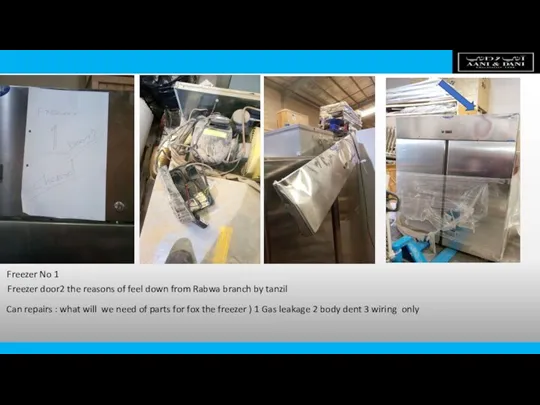

Ходовое оборудование строительных машин. Общие сведения и классификация Reports of old. Freezer

Reports of old. Freezer Электролиз. Применение

Электролиз. Применение Правовое обеспечение государственного управления – в пенсионной системе Российской Федерации

Правовое обеспечение государственного управления – в пенсионной системе Российской Федерации Адаптация детей раннего возраста к условиям ДОУ

Адаптация детей раннего возраста к условиям ДОУ Воспалительные заболевания височно-нижнечелюстного сустава

Воспалительные заболевания височно-нижнечелюстного сустава Презентация музыкально - дидактической игры

Презентация музыкально - дидактической игры Палех - город мастеров

Палех - город мастеров презентация к уроку географии ВЕТЕР

презентация к уроку географии ВЕТЕР Введение в радиологию

Введение в радиологию История баночки А.В. Чичкин Николая Верещагина

История баночки А.В. Чичкин Николая Верещагина Коварное желание. Синопсис

Коварное желание. Синопсис Образовательный проект Патриотическое воспитание дошкольников, через связь с социумом посредством проведения праздников и развлечений

Образовательный проект Патриотическое воспитание дошкольников, через связь с социумом посредством проведения праздников и развлечений Речевая играОтгадай кто?

Речевая играОтгадай кто? Отличия РНК от ДНК

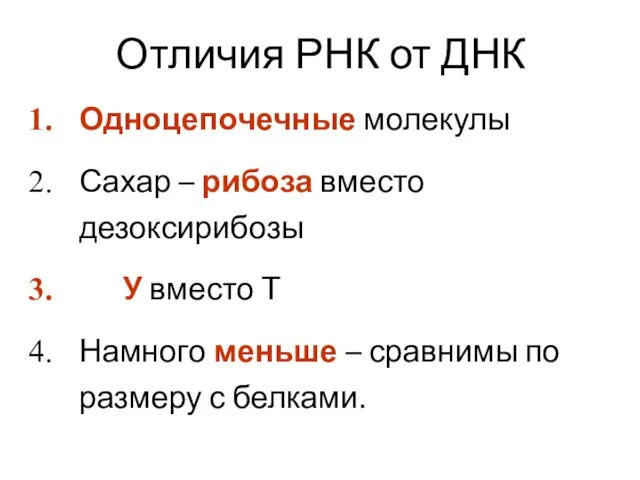

Отличия РНК от ДНК Непризнанные и самопровозглашенные государства

Непризнанные и самопровозглашенные государства Тренажер Таблицу умножения учим с увлечением

Тренажер Таблицу умножения учим с увлечением Разработка и технологии производства рекламного продукта. Творческая стратегия торговой марки

Разработка и технологии производства рекламного продукта. Творческая стратегия торговой марки