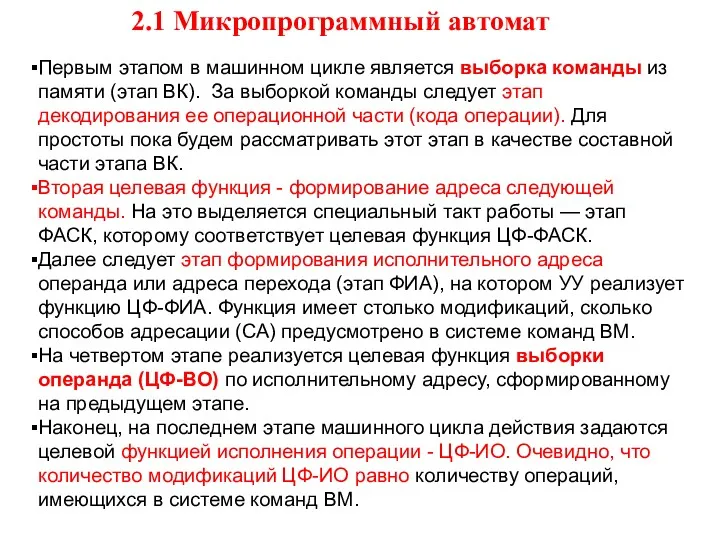

Первым этапом в машинном цикле является выборка команды из памяти (этап

ВК). За выборкой команды следует этап декодирования ее операционной части (кода операции). Для простоты пока будем рассматривать этот этап в качестве составной части этапа ВК.

Вторая целевая функция - формирование адреса следующей команды. На это выделяется специальный такт работы — этап ФАСК, которому соответствует целевая функция ЦФ-ФАСК.

Далее следует этап формирования исполнительного адреса операнда или адреса перехода (этап ФИА), на котором УУ реализует функцию ЦФ-ФИА. Функция имеет столько модификаций, сколько способов адресации (СА) предусмотрено в системе команд ВМ.

На четвертом этапе реализуется целевая функция выборки операнда (ЦФ-ВО) по исполнительному адресу, сформированному на предыдущем этапе.

Наконец, на последнем этапе машинного цикла действия задаются целевой функцией исполнения операции - ЦФ-ИО. Очевидно, что количество модификаций ЦФ-ИО равно количеству операций, имеющихся в системе команд ВМ.

2.1 Микропрограммный автомат

Без потерь и повреждений! (для курьеров, менеджеров клиентского сервиса и отдела продаж)

Без потерь и повреждений! (для курьеров, менеджеров клиентского сервиса и отдела продаж) Обезболивание в акушерстве

Обезболивание в акушерстве Виртуальная выставка. 205 лет М. Ю. Лермонтову

Виртуальная выставка. 205 лет М. Ю. Лермонтову Формирование навыка чтения и письма

Формирование навыка чтения и письма Применение различных способов для разложения на множители

Применение различных способов для разложения на множители Религия как одна из форм культуры

Религия как одна из форм культуры Выход проекта Я и моя Воркута

Выход проекта Я и моя Воркута Пословицы и поговорки. Народные приметы. Осенние загадки. Инсценирование произведения Н. Сладкова Осень

Пословицы и поговорки. Народные приметы. Осенние загадки. Инсценирование произведения Н. Сладкова Осень Тригонометрические выражения

Тригонометрические выражения День занимательных уроков

День занимательных уроков Презентация Зима

Презентация Зима Окружность (геометрия 7 класс)

Окружность (геометрия 7 класс) Проектирование локальной вычислительной сети магазина строительных инструментов

Проектирование локальной вычислительной сети магазина строительных инструментов Методический семинар

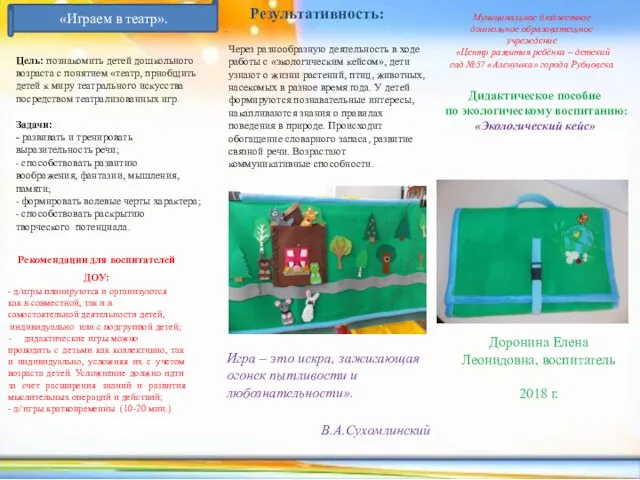

Методический семинар Влияние сюжетно-ролевых, подвижных, театрализованных, дидактических игр на развитие компетентностей детей дошкольного возраста

Влияние сюжетно-ролевых, подвижных, театрализованных, дидактических игр на развитие компетентностей детей дошкольного возраста Наполеон и Кутузов в романе Война и мир Л.Н. Толстого

Наполеон и Кутузов в романе Война и мир Л.Н. Толстого Фрезерные приспособления

Фрезерные приспособления Sacroma of the leg

Sacroma of the leg Теория привязанности через призму Ислама

Теория привязанности через призму Ислама Развитие навыков сотрудничества в совместной продуктивной деятельности детей. Средняя группа.

Развитие навыков сотрудничества в совместной продуктивной деятельности детей. Средняя группа. Подпорные стенки: назначение и основные конструктивные решения

Подпорные стенки: назначение и основные конструктивные решения Рабочая тетрадь по чистописанию (2 класс)

Рабочая тетрадь по чистописанию (2 класс) Выставление оценок в электронный журнал

Выставление оценок в электронный журнал Введение в проектное обучение и управление

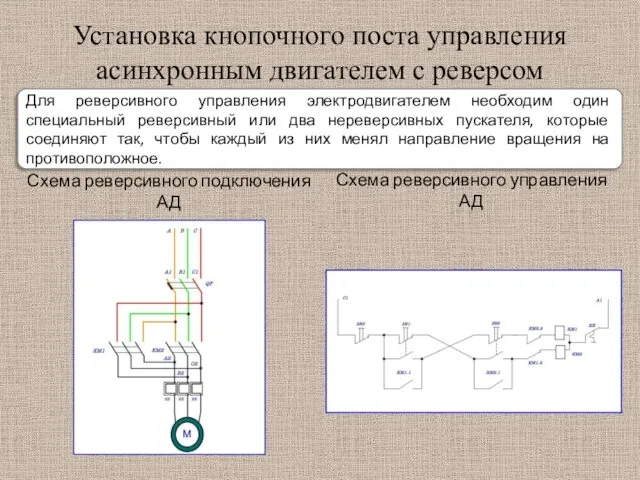

Введение в проектное обучение и управление Установка кнопочного поста управления асинхронным двигателем с реверсом

Установка кнопочного поста управления асинхронным двигателем с реверсом От Исландии до Пиренейского полуострова

От Исландии до Пиренейского полуострова Экология

Экология Заболевания органов кроветворения

Заболевания органов кроветворения