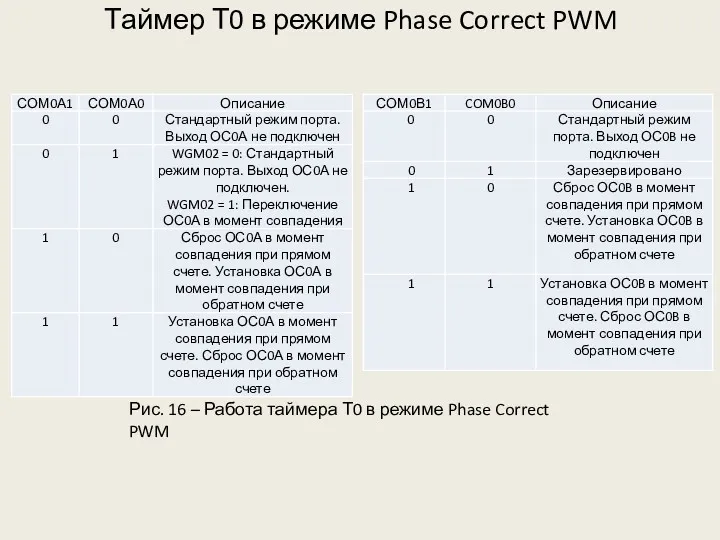

Таймер Т0

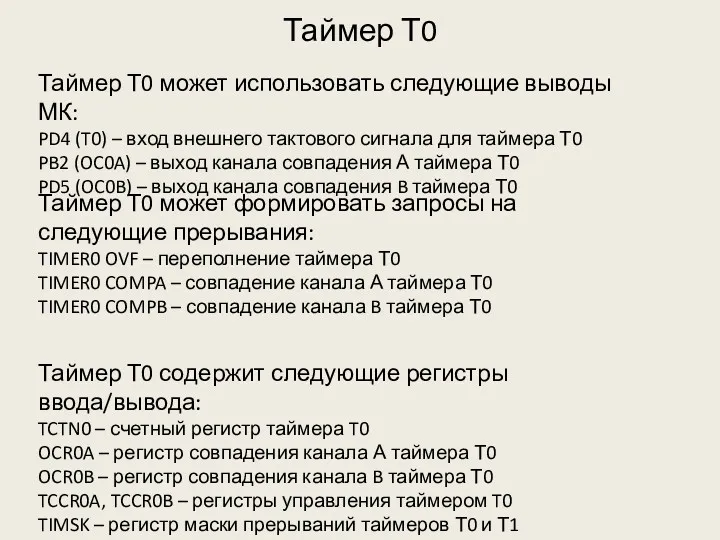

Бит 2 — OCIE0B: Разрешение прерываний таймера/счетчика 0 по совпадению

в канале В. Когда бит OCIE0B установлен в единицу, а флаг I регистра состояния также установлен, то прерывания по совпадению в канале В таймера 0 разрешены. Генерация запроса на прерывание происходит в момент совпадения, если бит OCF0B регистра TIFR установлен.

Бит 1 — TOIE0: Разрешение прерывания по переполнению таймера/счетчика 0. Если бит TOIE0 установлен в единицу, а также установлен флаг I регистра состояния, то прерывания по переполнению таймера 0 разрешены. Генерация запроса на прерывание происходит в случае переполнения таймера/счетчика 0, если бит TOV0 регистра TIFR установлен.

Бит 0 — OCIE0A: Разрешение прерываний таймера/счетчика 0 по совпадению в канале А. Когда установлены бит OCIE0A в единицу и флаг I регистра состояния, то прерывания по совпадению в канале В таймера 0 разрешены. Генерация запроса на прерывание происходит в момент совпадения, если бит OCF0A регистра TIFR установлен.

Рис. 2 – Описание регистра TIMSK

презентация работа с родителями по фгос

презентация работа с родителями по фгос Социальная структура общества

Социальная структура общества Древний Египет

Древний Египет 152446

152446 Культ личности И.В. Сталина. Массовые репрессии и создание централизованной системы управления страной

Культ личности И.В. Сталина. Массовые репрессии и создание централизованной системы управления страной Нормативные акты, регламентирующие автоперевозки

Нормативные акты, регламентирующие автоперевозки Кали-сантарана-упанишад

Кали-сантарана-упанишад презентация мастер-класса Понимание позиции - как один из способов формирования способности понимания у старших дошкольников

презентация мастер-класса Понимание позиции - как один из способов формирования способности понимания у старших дошкольников Великие люди Германии

Великие люди Германии МХК 8 КЛАСС 7

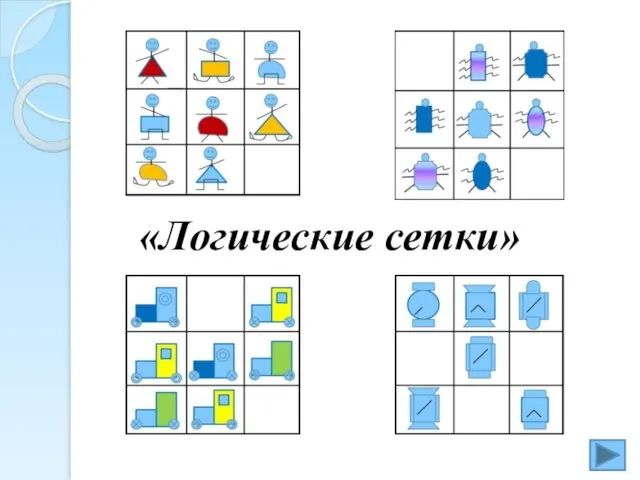

МХК 8 КЛАСС 7 Логические сетки

Логические сетки Социальная компетентность детей и подростков

Социальная компетентность детей и подростков Вимоги до оформлення матеріалів дипломної (або магістерської атестаційної) роботи (відповідно до Державного стандарту України)

Вимоги до оформлення матеріалів дипломної (або магістерської атестаційної) роботи (відповідно до Державного стандарту України) О вреде вейпа

О вреде вейпа Атмосферные фронты. Циклоны. Антициклоны.

Атмосферные фронты. Циклоны. Антициклоны. Исследуй снег. МКОУ Ихальская СОШ, 1 класс. Команда Природооткрыватели

Исследуй снег. МКОУ Ихальская СОШ, 1 класс. Команда Природооткрыватели Классный час Всё начинается с семьи...

Классный час Всё начинается с семьи... викторина Умники и умницы

викторина Умники и умницы Кафедра экономики предприятия

Кафедра экономики предприятия Духовная зрелость человека

Духовная зрелость человека Smart goal

Smart goal Церкви великомученика Димитрия Солунского

Церкви великомученика Димитрия Солунского Промислові будівлі та споруди

Промислові будівлі та споруди Почва. Часть 2. 5-8 класс

Почва. Часть 2. 5-8 класс Нарастание международных противоречий. Балканы - пороховая бочка Европы

Нарастание международных противоречий. Балканы - пороховая бочка Европы Физическое развитие детей дошкольного возраста и ФГОС

Физическое развитие детей дошкольного возраста и ФГОС Бунин Иван Александрович (1870-1953)

Бунин Иван Александрович (1870-1953) Первое школьное родительское собрание в 1 классе

Первое школьное родительское собрание в 1 классе