Содержание

- 2. Таймеры и процессоры событий Большинство задач управления, которые реализуются с помощью МК, требуют исполнения их в

- 3. Модули таймеров/счётчиков служат для приема информации о времени наступления тех или иных событий (от внутренних генераторов

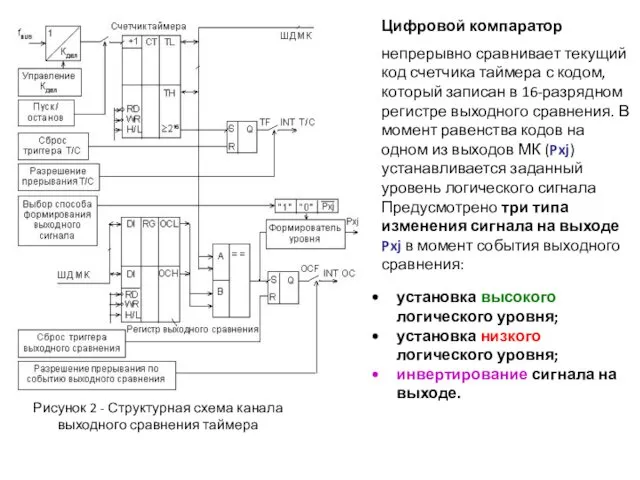

- 4. Рисунок 2 - Структурная схема канала выходного сравнения таймера Цифровой компаратор непрерывно сравнивает текущий код счетчика

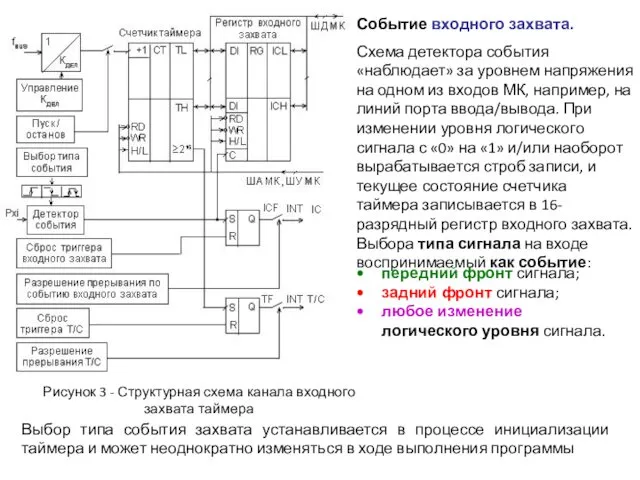

- 5. Рисунок 3 - Структурная схема канала входного захвата таймера Событие входного захвата. Схема детектора события «наблюдает»

- 6. Микроконтроллеры семейства Atmel AVR Mega в зависимости от модели имеют в своем составе от двух до

- 7. В составе всех микроконтроллеров семейства имеется также сторожевой таймер, являющийся непременным атрибутом всех современных микроконтроллеров. Сторожевой

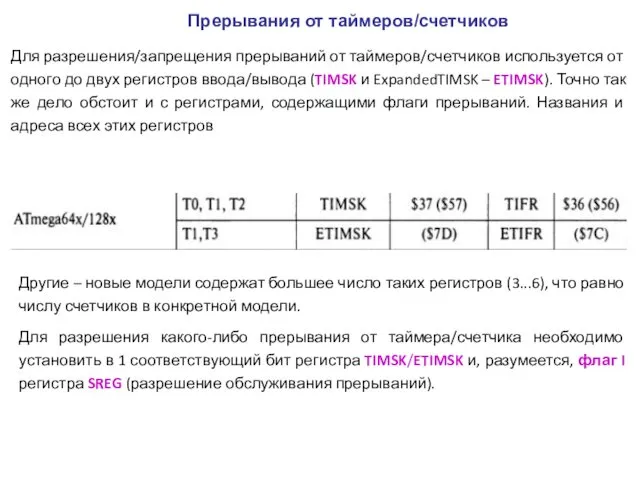

- 8. Для разрешения/запрещения прерываний от таймеров/счетчиков используется от одного до двух регистров ввода/вывода (TIMSK и ExpandedTIMSK –

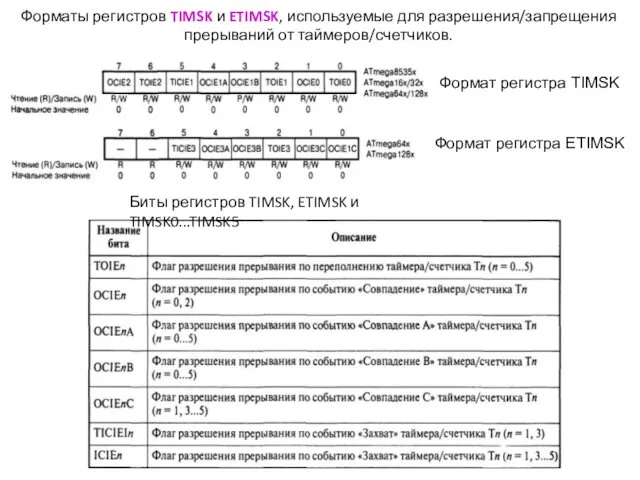

- 9. Биты регистров TIMSK, ETIMSK и TIMSK0...TIMSK5 Форматы регистров TIMSK и ETIMSK, используемые для разрешения/запрещения прерываний от

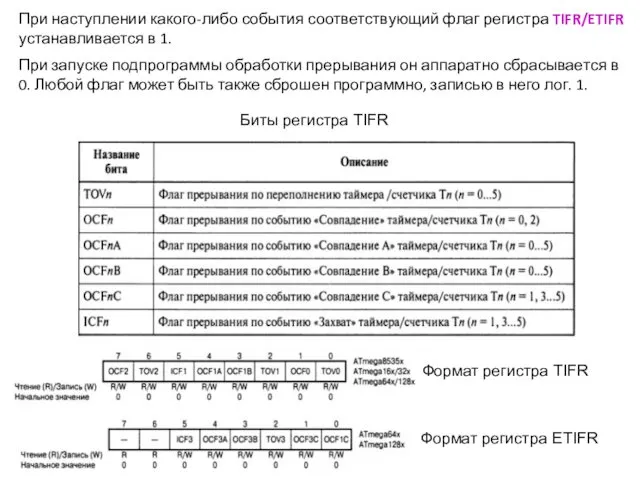

- 10. При наступлении какого-либо события соответствующий флаг регистра TIFR/ETIFR устанавливается в 1. При запуске подпрограммы обработки прерывания

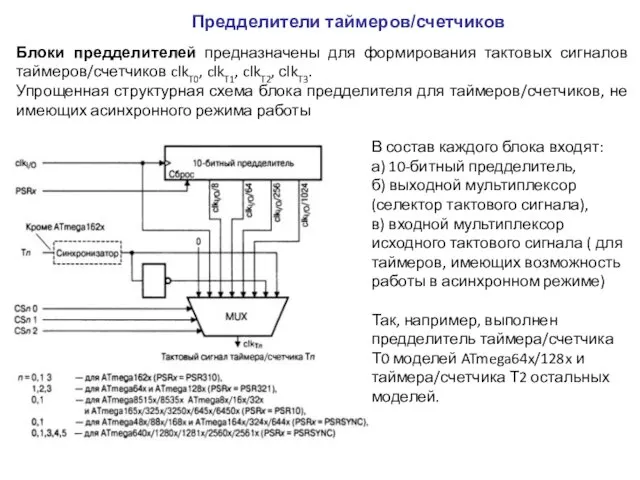

- 11. Блоки предделителей предназначены для формирования тактовых сигналов таймеров/счетчиков clkT0, clkT1, clkT2, сlkT3. Упрощенная структурная схема блока

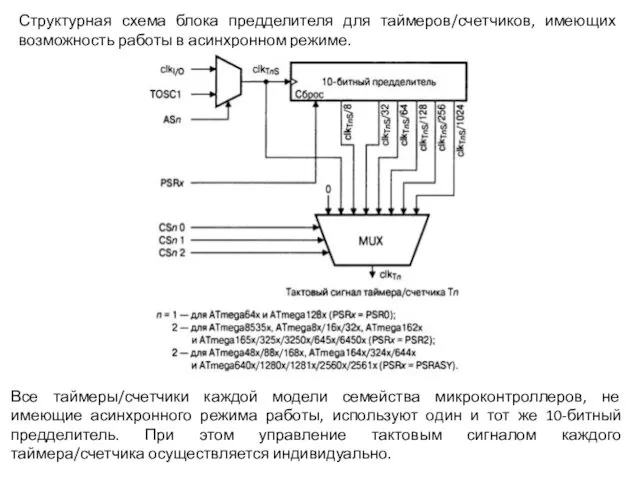

- 12. Структурная схема блока предделителя для таймеров/счетчиков, имеющих возможность работы в асинхронном режиме. Все таймеры/счетчики каждой модели

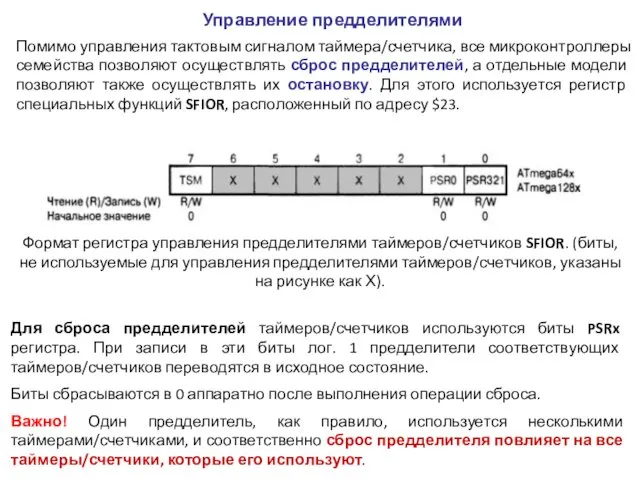

- 13. Помимо управления тактовым сигналом таймера/счетчика, все микроконтроллеры семейства позволяют осуществлять сброс предделителей, а отдельные модели позволяют

- 14. Остановка всех предделителей микроконтроллера осуществляется записью лог 1 в бит TSM регистра SFIOR. Запуск предделителей осуществляется

- 15. Практически все таймеры/счетчики, не имеющие асинхронного режима работы, могут тактироваться от внешнего сигнала. Внешний сигнал, поступает

- 16. Синхронизация внешнего сигнала осуществляется с частотой тактового сигнала микроконтроллера (состояние вывода Т1 считывается по нарастающему фронту

- 17. Формирование тактового сигнала таймера/счетчика clkT0(T2) осуществляется блоком предделителя. В качестве тактового сигнала clkT0(T2) таймеров/счетчиков, не имеющих

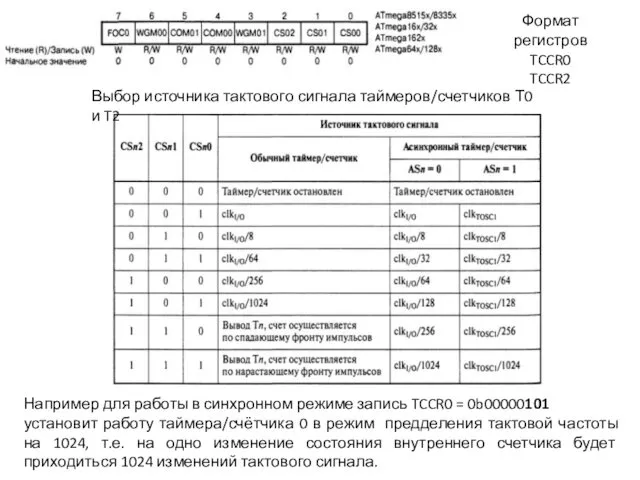

- 18. Выбор источника тактового сигнала таймеров/счетчиков Т0 и T2 Например для работы в синхронном режиме запись TCCR0

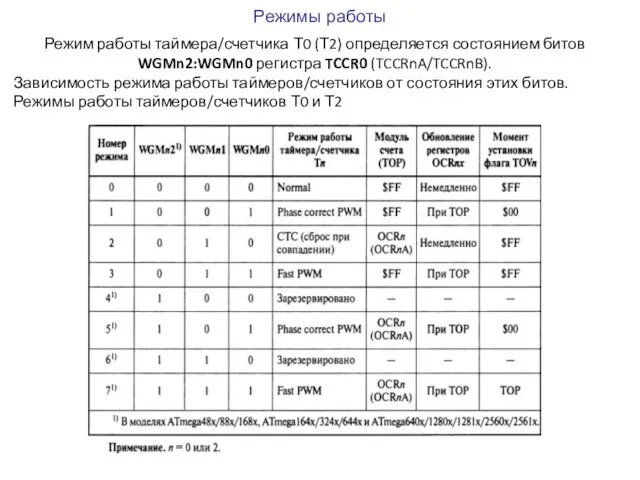

- 19. Режим работы таймера/счетчика Т0 (Т2) определяется состоянием битов WGMn2:WGMn0 регистра TCCR0 (TCCRnA/TCCRnB). Зависимость режима работы таймеров/счетчиков

- 20. Режим Normal - наиболее простой режим работы таймеров/счетчиков. Для некоторых таймеров/счетчиков, например, Т0 модели ATmega8x это

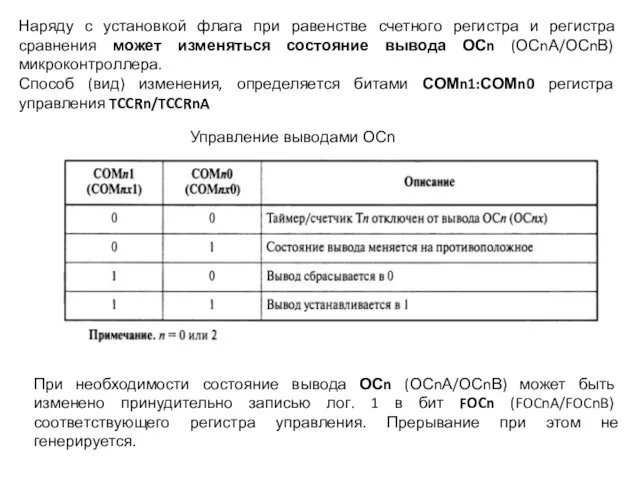

- 21. Управление выводами OCn Наряду с установкой флага при равенстве счетного регистра и регистра сравнения может изменяться

- 22. В режиме CTC счетный регистр TCNT тоже функционирует как обычный суммирующий счетчик, инкрементирование которого осуществляется по

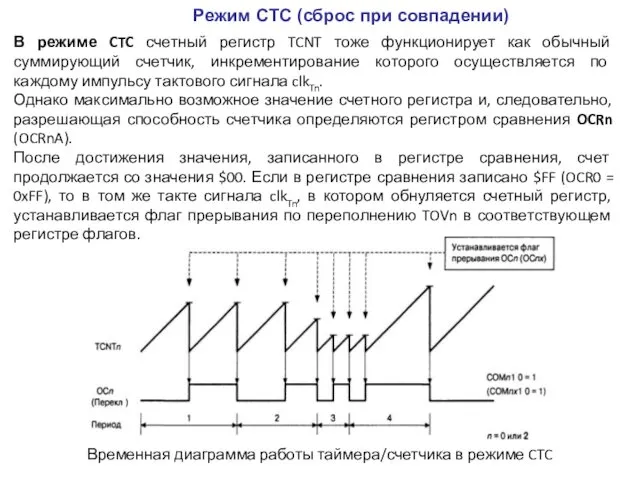

- 24. Скачать презентацию

Искусство формирования составов модельных поездов

Искусство формирования составов модельных поездов Характеристики методов обучения

Характеристики методов обучения Послеродовый гипопитуитаризм (синдром Шихана)

Послеродовый гипопитуитаризм (синдром Шихана) Биологиялық мембрананың өткізгіштік механаимі. Иондық каналдар және тасымалдаушылардың құрылысы мен функциясы

Биологиялық мембрананың өткізгіштік механаимі. Иондық каналдар және тасымалдаушылардың құрылысы мен функциясы Голицыно – город будущего

Голицыно – город будущего звуки т д

звуки т д Вегетативная (автономная, висцеральная) нервная система. Часть 3

Вегетативная (автономная, висцеральная) нервная система. Часть 3 Ислам өркениеті

Ислам өркениеті Презентации Диск

Презентации Диск Разработка и анализ инвестиционных проектов

Разработка и анализ инвестиционных проектов Презентация к уроку Мужества Парад 7 ноября 1941 года в г.Куйбышев

Презентация к уроку Мужества Парад 7 ноября 1941 года в г.Куйбышев Из чего состоит радиоуправляемая автомодель

Из чего состоит радиоуправляемая автомодель Микроклональное размножение растений

Микроклональное размножение растений Производство оптического бесцветного стекла

Производство оптического бесцветного стекла Виды плана

Виды плана Построение вариационной кривой

Построение вариационной кривой ОАО Брестский ликероводочный завод Белалко

ОАО Брестский ликероводочный завод Белалко Выступление на занятии мастер - класс № 1 по теме Критерии личностного роста учителя

Выступление на занятии мастер - класс № 1 по теме Критерии личностного роста учителя Виробництво продуктів харчування у світі

Виробництво продуктів харчування у світі Внеклассное мероприятие для 3 класса Новое о светофорах

Внеклассное мероприятие для 3 класса Новое о светофорах Графические изображения статистических данных

Графические изображения статистических данных Лекція 2. Ф.Риз

Лекція 2. Ф.Риз Интерьер жилого дома

Интерьер жилого дома Презентация к внеклассному мероприятию Космос

Презентация к внеклассному мероприятию Космос Понятийный аппарат научного исследования, его содержание и характеристика

Понятийный аппарат научного исследования, его содержание и характеристика презентация 15.04

презентация 15.04 Презентация проекта 9 Мая в старшей группе

Презентация проекта 9 Мая в старшей группе Мы путешественники! Конспект выпускного занятия с использованием ИКТ в подготовительной группе Диск Диск

Мы путешественники! Конспект выпускного занятия с использованием ИКТ в подготовительной группе Диск Диск