Содержание

- 2. Термины Команда. Микрооперация или микрокоманда. Микропрограмма. Микропрограммный автомат.

- 3. Повышение производительности процессоров Конвейеризация. Суперскаляризация. Увеличение количества исполнительных блоков. Введение принципа динамического исполнения команд. Гипертрейдинг. Параллелизм

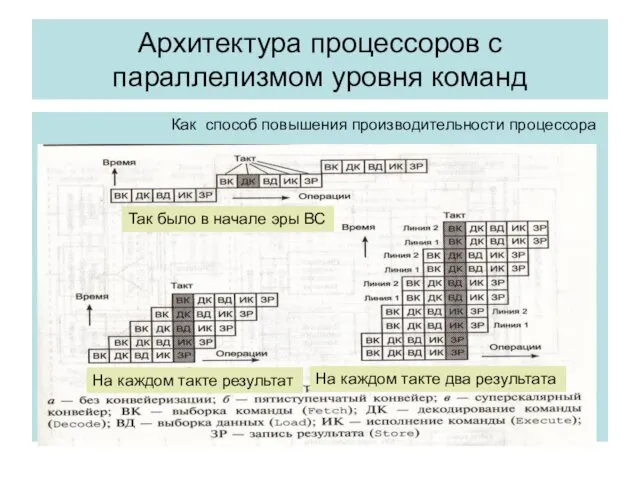

- 4. Архитектура процессоров с параллелизмом уровня команд Как способ повышения производительности процессора Так было в начале эры

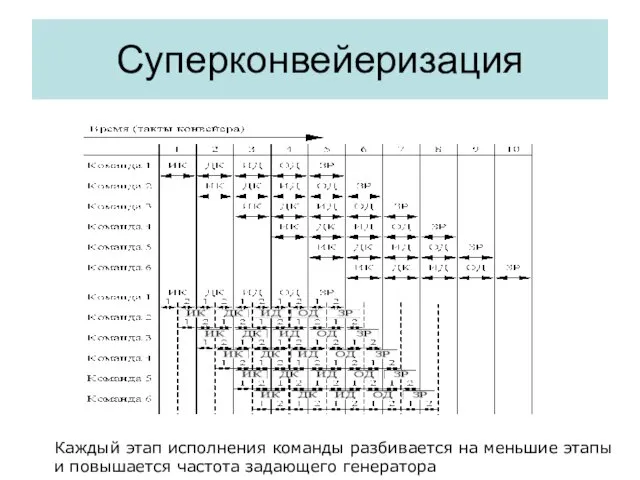

- 5. Суперконвейеризация Каждый этап исполнения команды разбивается на меньшие этапы и повышается частота задающего генератора

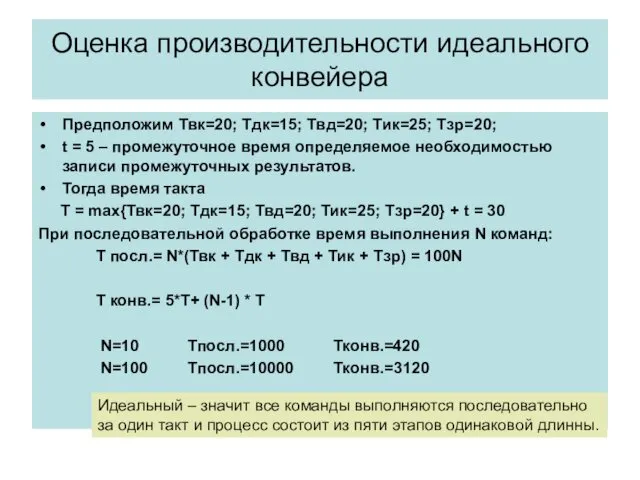

- 6. Оценка производительности идеального конвейера Предположим Твк=20; Тдк=15; Твд=20; Тик=25; Тзр=20; t = 5 – промежуточное время

- 7. Конвейер с точки зрения схемотехники КС RG КС RG КС RG CИ1 CИ2 CИ3 n Чем

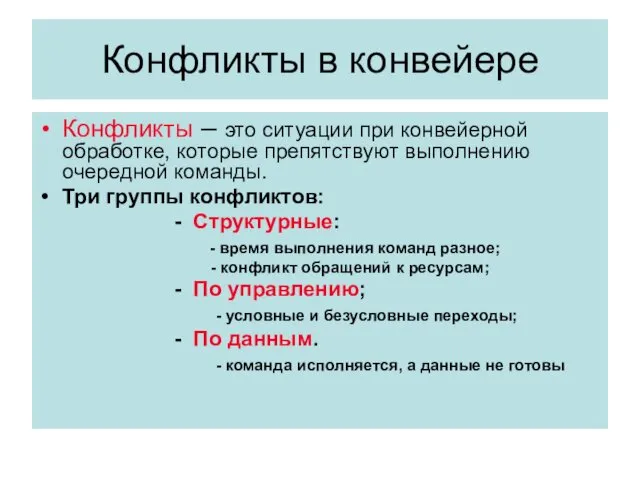

- 8. Конфликты в конвейере Конфликты – это ситуации при конвейерной обработке, которые препятствуют выполнению очередной команды. Три

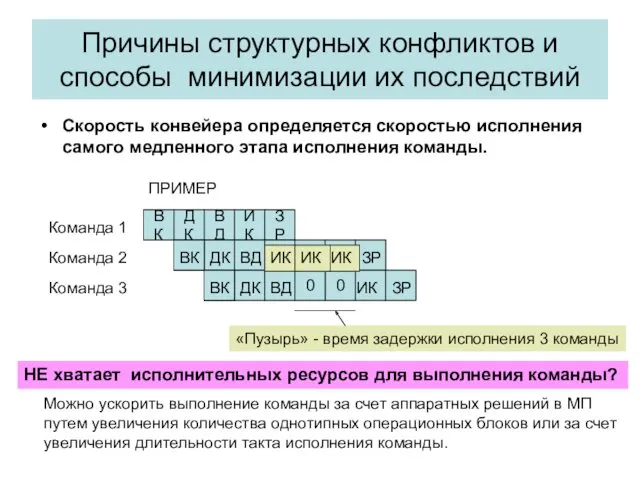

- 9. Причины структурных конфликтов и способы минимизации их последствий Скорость конвейера определяется скоростью исполнения самого медленного этапа

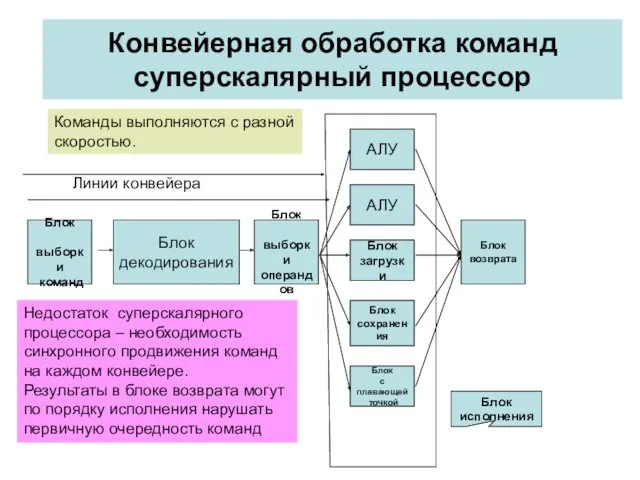

- 10. Конвейерная обработка команд суперскалярный процессор Блок выборки команд Блок декодирования Блок выборки операндов АЛУ АЛУ Блок

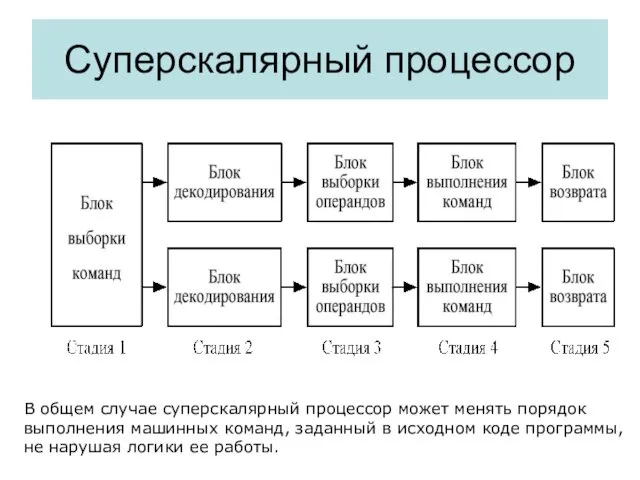

- 11. Суперскалярный процессор В общем случае суперскалярный процессор может менять порядок выполнения машинных команд, заданный в исходном

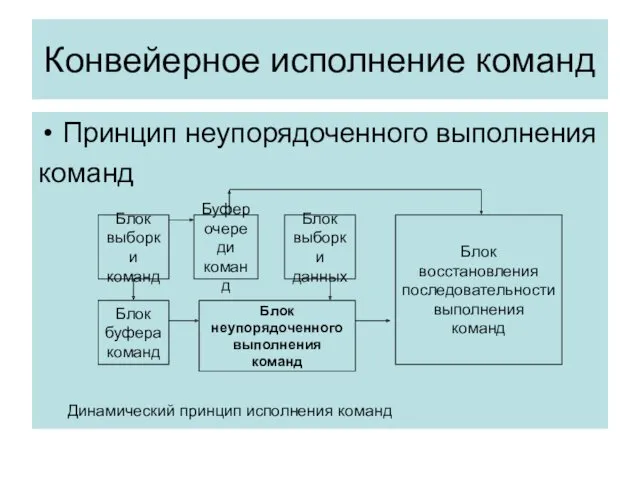

- 12. Конвейерное исполнение команд Принцип неупорядоченного выполнения команд Блок выборки команд Блок буфера команд Буфер очереди команд

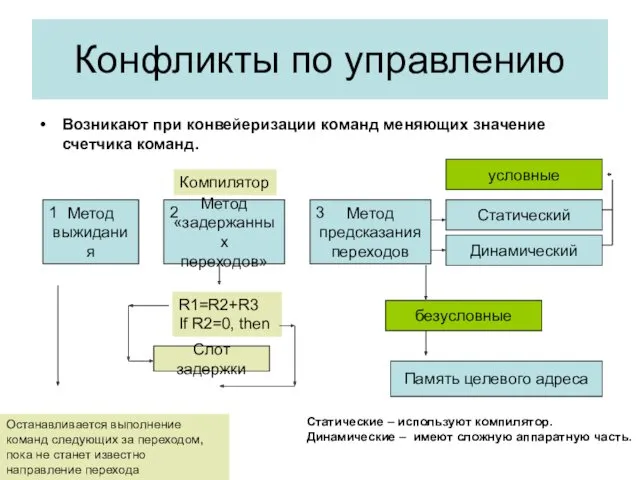

- 13. Конфликты по управлению Возникают при конвейеризации команд меняющих значение счетчика команд. Метод выжидания Метод «задержанных переходов»

- 14. Статическое предсказание переходов Осуществляется на основе некоторой априорной информации о подлежащей исполнению программе. Известны следующие стратегии:

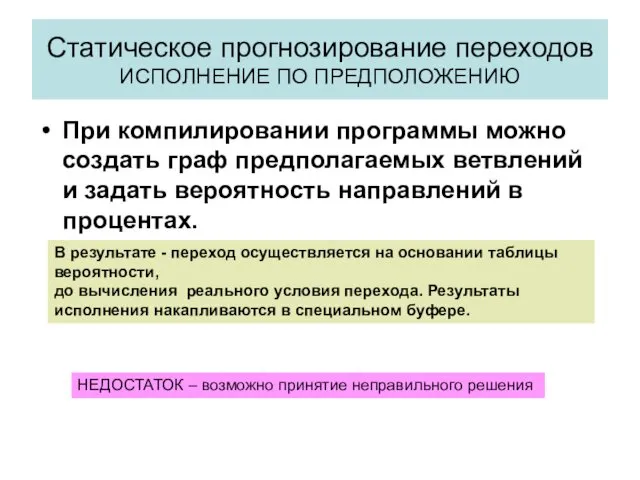

- 15. Статическое прогнозирование переходов ИСПОЛНЕНИЕ ПО ПРЕДПОЛОЖЕНИЮ При компилировании программы можно создать граф предполагаемых ветвлений и задать

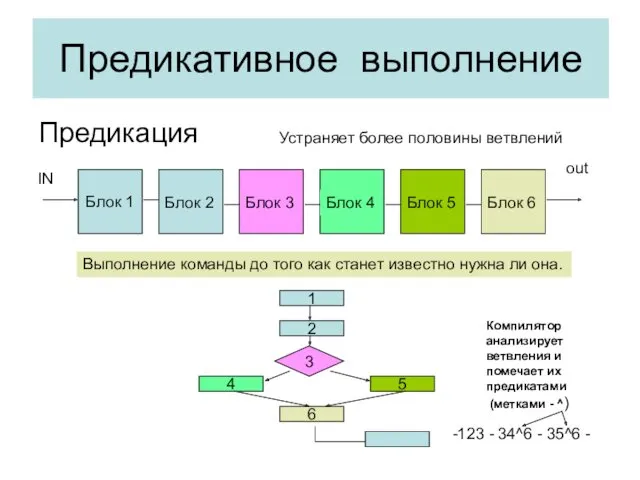

- 16. Предикативное выполнение Предикация Блок 1 Блок 2 Блок 3 Блок 5 Блок 4 Блок 6 IN

- 17. Динамическое предсказание переходов Решение о наиболее вероятном исходе команды перехода принимается в ходе вычислений исходя из

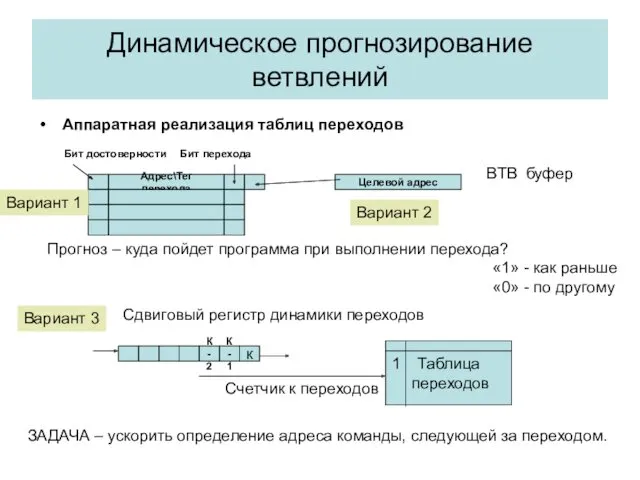

- 18. Динамическое прогнозирование ветвлений Аппаратная реализация таблиц переходов Адрес\Тег перехода Бит перехода Бит достоверности Целевой адрес Вариант

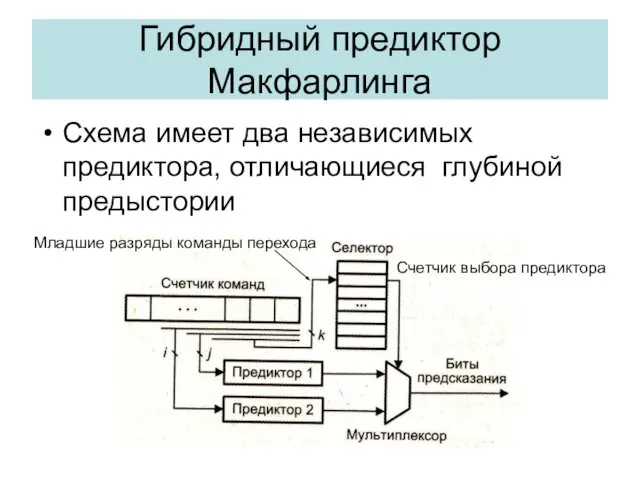

- 19. Гибридный предиктор Макфарлинга Схема имеет два независимых предиктора, отличающиеся глубиной предыстории Счетчик выбора предиктора Младшие разряды

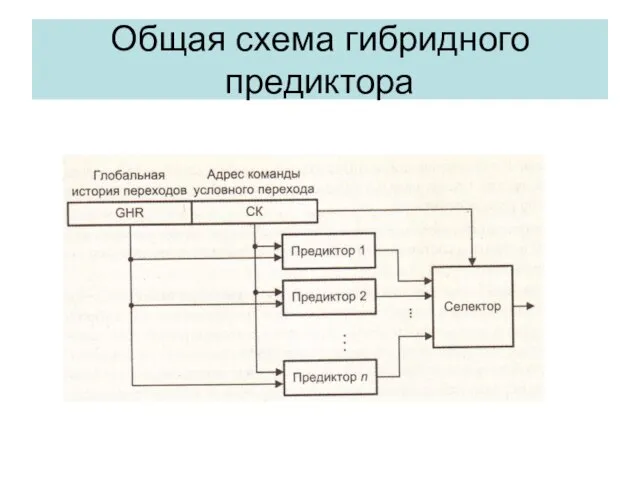

- 20. Общая схема гибридного предиктора

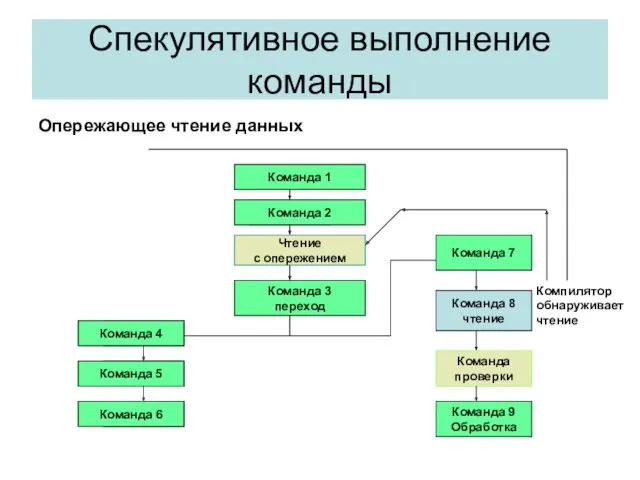

- 21. Опережающее чтение данных Спекулятивное выполнение команды Команда 1 Чтение с опережением Команда проверки Команда 9 Обработка

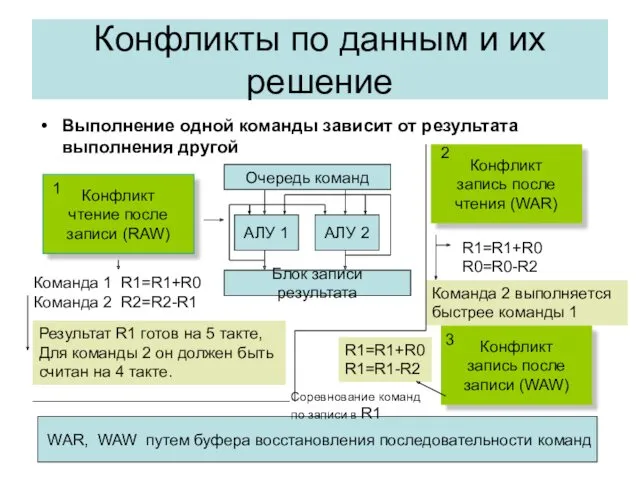

- 22. Выполнение одной команды зависит от результата выполнения другой Конфликты по данным и их решение Конфликт чтение

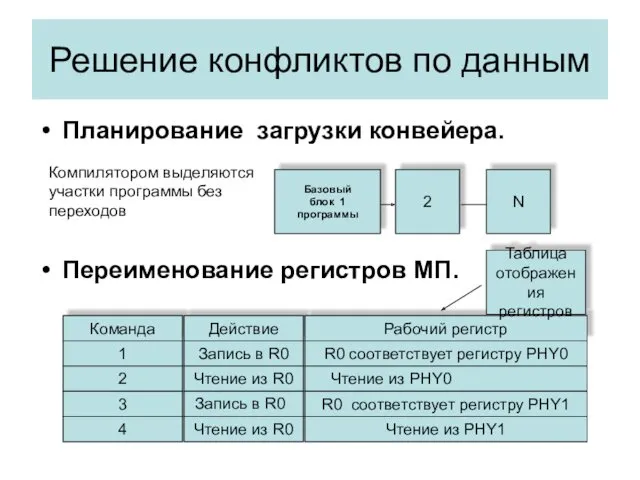

- 23. Планирование загрузки конвейера. Переименование регистров МП. Решение конфликтов по данным Базовый блок 1 программы 2 Команда

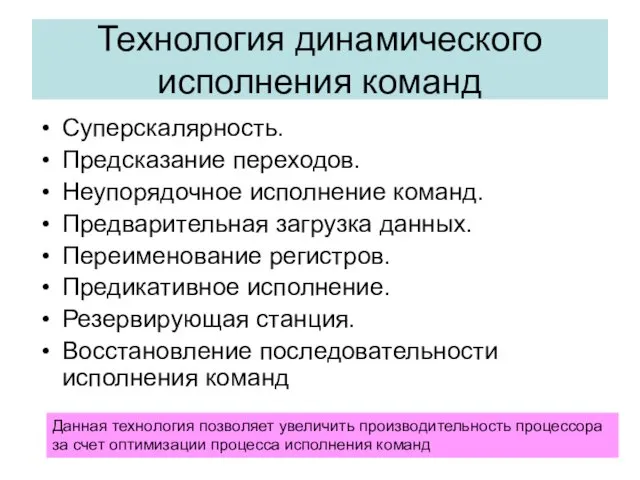

- 24. Технология динамического исполнения команд Суперскалярность. Предсказание переходов. Неупорядочное исполнение команд. Предварительная загрузка данных. Переименование регистров. Предикативное

- 25. Характеристика конвейeров МП Intel и AMD

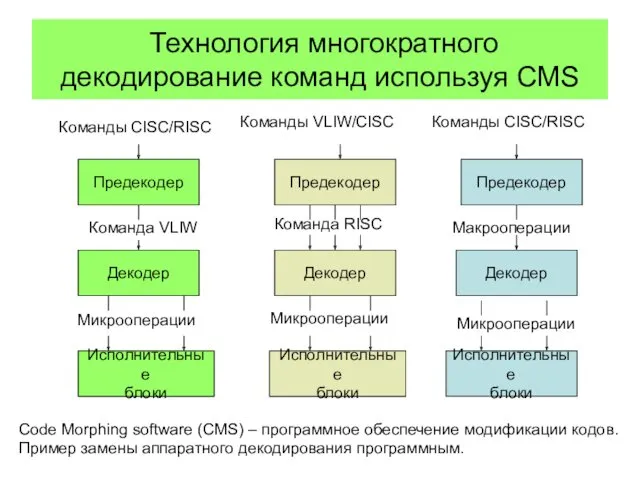

- 26. Технология многократного декодирование команд используя CMS Предекодер Предекодер Предекодер Декодер Исполнительные блоки Команды CISC/RISC Команда VLIW

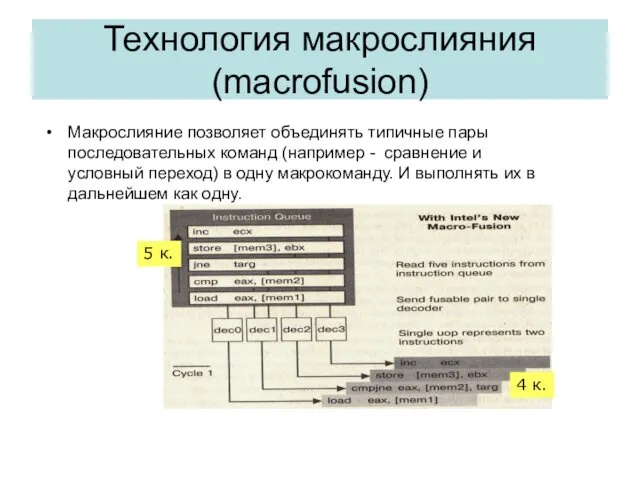

- 27. Технология макрослияния (macrofusion) Макрослияние позволяет объединять типичные пары последовательных команд (например - сравнение и условный переход)

- 28. Технология микрослияния (Micro-op fusion) Команды при декодировании могут использовать одинаковые микрокоманды Технология предусматривает однократный вызов микрокоманды

- 29. Технология резервирующей станции Команды выполняются с разным быстродействием. Команды могут зависеть друг от друга. Командам могут

- 30. Микроархитектура Pentium2 Устройство сопряжения с шиной Кэш первого уровня для команд Кэш первого уровня для данных

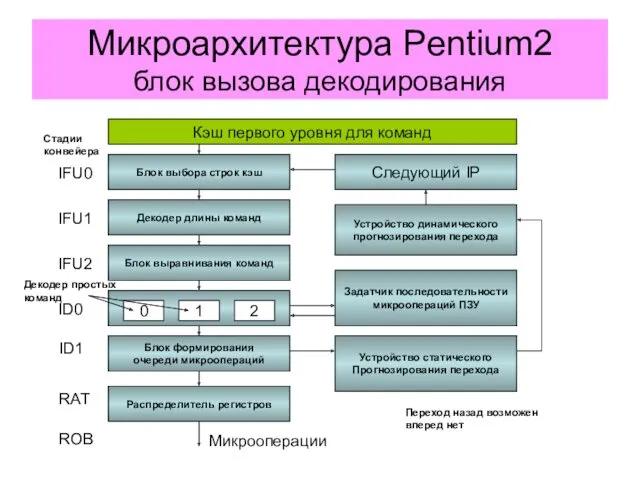

- 31. Микроархитектура Pentium2 блок вызова декодирования Кэш первого уровня для команд Блок выбора строк кэш Декодер длины

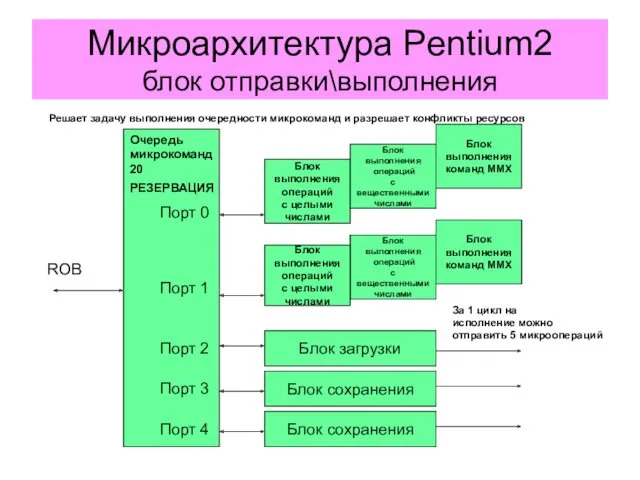

- 32. Микроархитектура Pentium2 блок отправки\выполнения Очередь микрокоманд 20 РЕЗЕРВАЦИЯ Блок выполнения операций с целыми числами Блок выполнения

- 33. Микроархитектура Pentium2 блок возврата Отвечает: - за отправку результатов в регистры или устройства, которым они требуются.

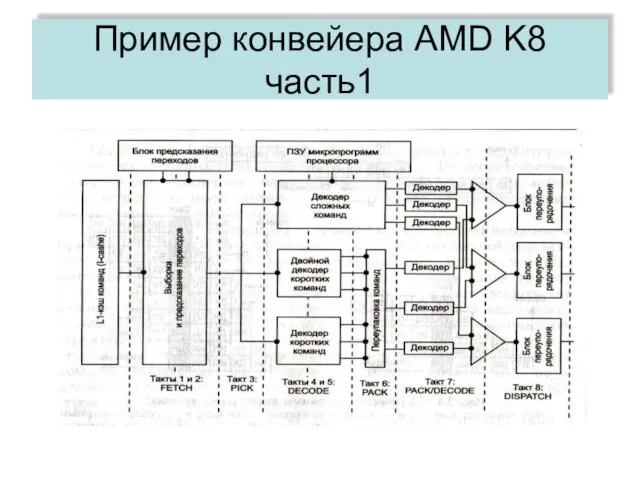

- 34. Пример конвейера AMD K8 часть1

- 35. Пример конвейера AMD K8 часть 2

- 36. Проблемы суперскальных МП Простои конвейеров из-за нерегулярной загрузки функциональных устройств МП. Наличие одного счетчика команд. Ограничение

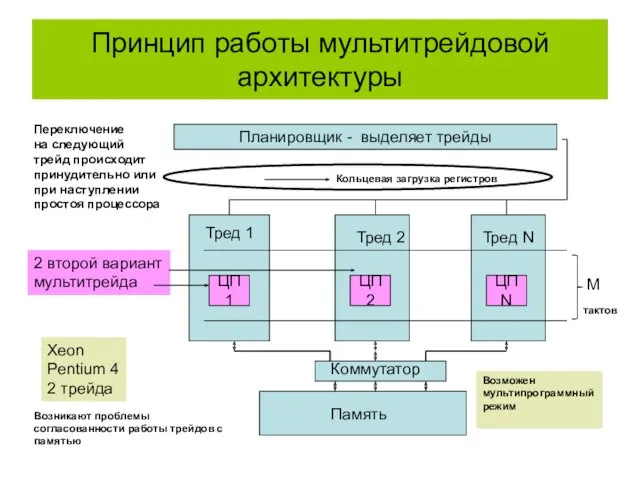

- 37. Мультитрейдовые микропроцессоры Тред – вычислительный процесс обслуживаемый отдельным набором регистров. Однотрейдовый микропроцессор – имеет один счетчик

- 38. Принцип работы мультитрейдовой архитектуры Тред 1 Тред 2 Тред N Память Коммутатор M тактов Планировщик -

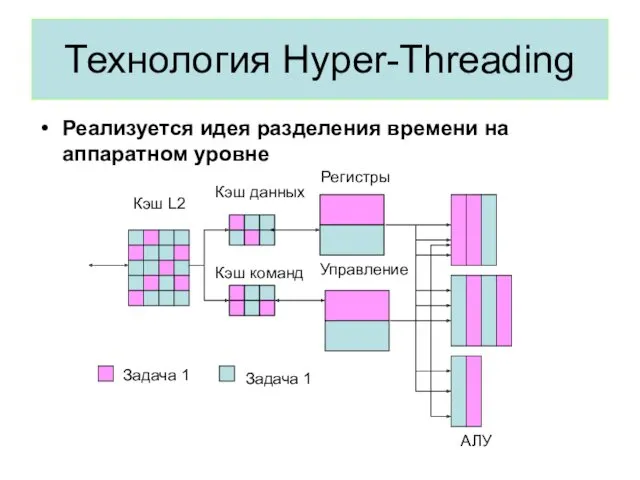

- 39. Технология Hyper-Threading Реализуется идея разделения времени на аппаратном уровне Задача 1 Задача 1 АЛУ Регистры Управление

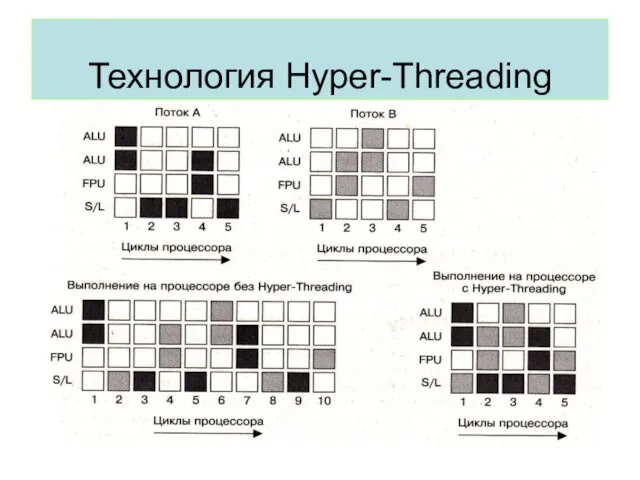

- 40. Технология Hyper-Threading

- 41. Itanium Использование сложных команд переменной длины, обрабатываемых последовательно Использование простых команд одинаковой длины, сгруппированных в связки

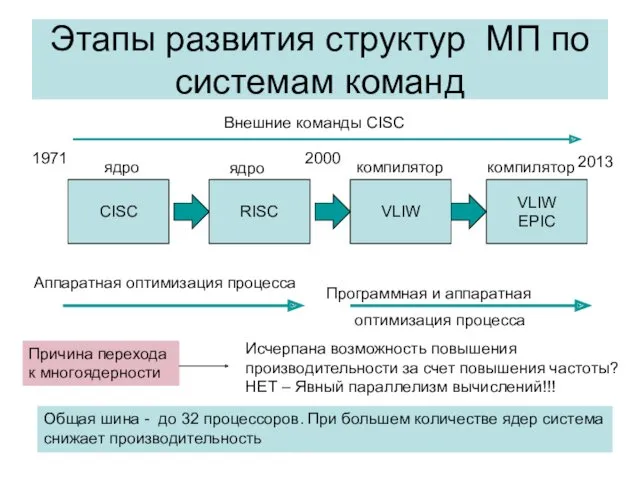

- 42. Этапы развития структур МП по системам команд CISC RISC VLIW VLIW EPIC Внешние команды CISC ядро

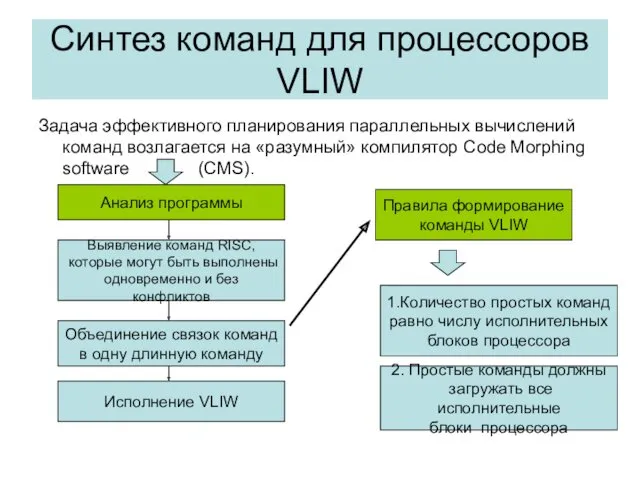

- 43. Синтез команд для процессоров VLIW Задача эффективного планирования параллельных вычислений команд возлагается на «разумный» компилятор Code

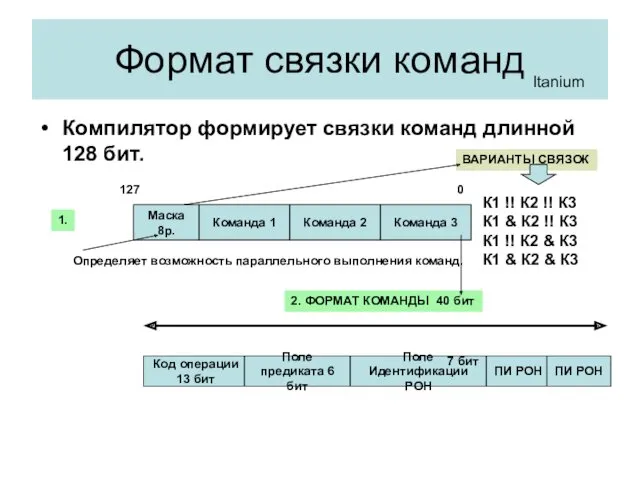

- 44. Формат связки команд Компилятор формирует связки команд длинной 128 бит. Itanium Маска 8р. Команда 1 Команда

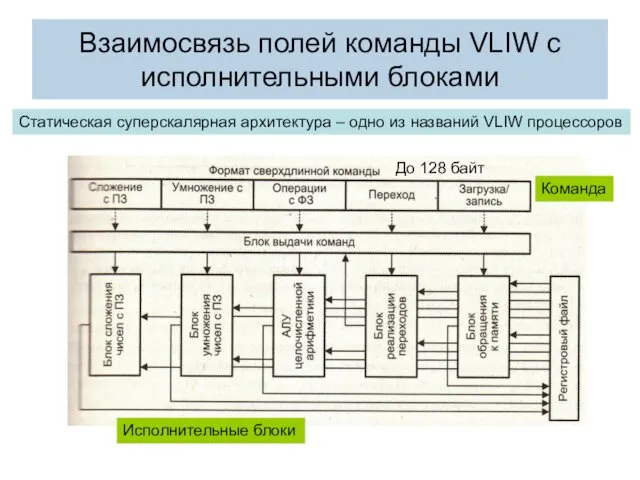

- 45. Взаимосвязь полей команды VLIW с исполнительными блоками До 128 байт Статическая суперскалярная архитектура – одно из

- 47. Скачать презентацию

Шаблоны для презентаций -школьные 1

Шаблоны для презентаций -школьные 1 Методы педагогического исследования. Работа с литературой

Методы педагогического исследования. Работа с литературой Ах, лето красное. Игра

Ах, лето красное. Игра Использование репрезентативной системы в воспитании и обучении

Использование репрезентативной системы в воспитании и обучении Вторая жизнь мусора

Вторая жизнь мусора Марк Леви

Марк Леви Культура Киевской Руси IX - XIII веков

Культура Киевской Руси IX - XIII веков Методы сведения балансов производственного пара. Причины возникновения дебалансов пара

Методы сведения балансов производственного пара. Причины возникновения дебалансов пара Электрические нагрузки. (Лекция 2)

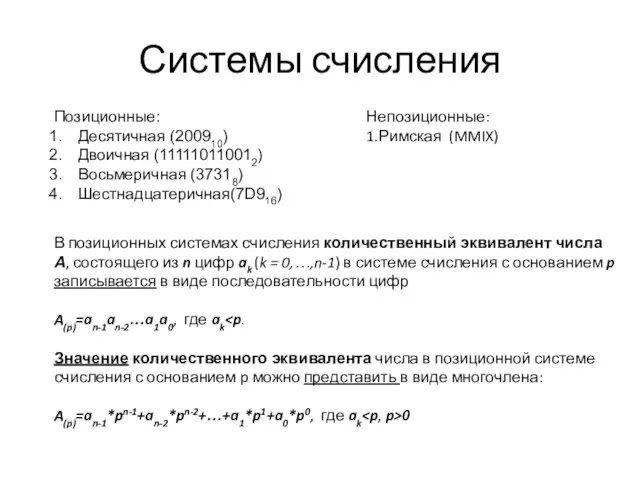

Электрические нагрузки. (Лекция 2) Системы счисления

Системы счисления Індія

Індія 10. Австрійська та Рос. імперії

10. Австрійська та Рос. імперії Буддизм. Түсінік

Буддизм. Түсінік Население и страны Европы

Население и страны Европы Метод учебного проекта

Метод учебного проекта Қазіргі әлемдегі машина жасау өнеркәсібінің дамуы

Қазіргі әлемдегі машина жасау өнеркәсібінің дамуы Рыба охлажденная

Рыба охлажденная Имена существительные собственные и нарицательные

Имена существительные собственные и нарицательные Кремнийорганикалық қосылыстар

Кремнийорганикалық қосылыстар Улица полна неожиданностей

Улица полна неожиданностей Проектная деятельность учащихся на уроках и внеурочное время

Проектная деятельность учащихся на уроках и внеурочное время Семейство нелетающих морских птиц - пингвины

Семейство нелетающих морских птиц - пингвины Абрамов Федор Александрович (1920-1983)

Абрамов Федор Александрович (1920-1983) Ламинированные напольные покрытия

Ламинированные напольные покрытия Фронтовая поэзия Г.К. Суворова

Фронтовая поэзия Г.К. Суворова Защитники Приднестровья в 1990-е годы

Защитники Приднестровья в 1990-е годы Второе Пришествие

Второе Пришествие Цели урока

Цели урока