Содержание

- 2. Цифровая схемотехника Аннотация Освоение цифровой техники начиная с математических основ, принципов построения логических комбинационных и последовательностных

- 3. Цифровая схемотехника #5 Лекция. Последовательностные устойства Доцент, к.т.н. Мусапирова Гульзада Даулетбековна g.musapirova@aues.kz

- 4. Литература Основная: 1.Немцов М.В. Электротехника и электроника. / М.В. Немцов, М.Л. Немцова – М: Академия, 2014.

- 5. Последовательностные устойства К ним относятся устройства, обладающие памятью, т.е. устройства со способностью сохранять предыдущее состояние. Поэтому,

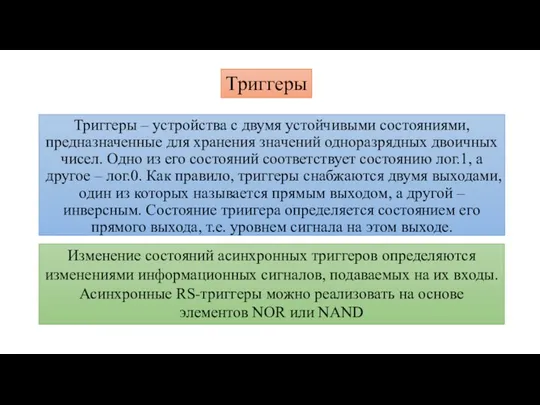

- 6. Триггеры – устройства с двумя устойчивыми состояниями, предназначенные для хранения значений одноразрядных двоичных чисел. Одно из

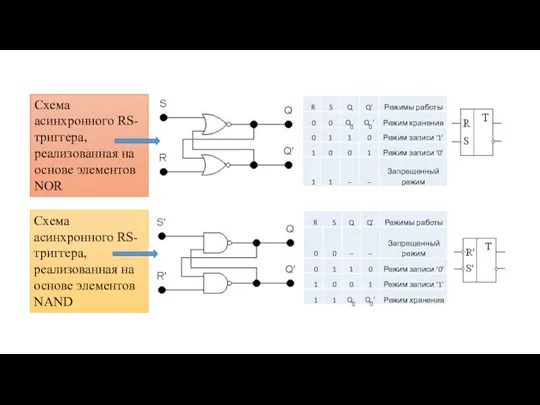

- 7. Схема асинхронного RS-триггера, реализованная на основе элементов NOR Схема асинхронного RS-триггера, реализованная на основе элементов NAND

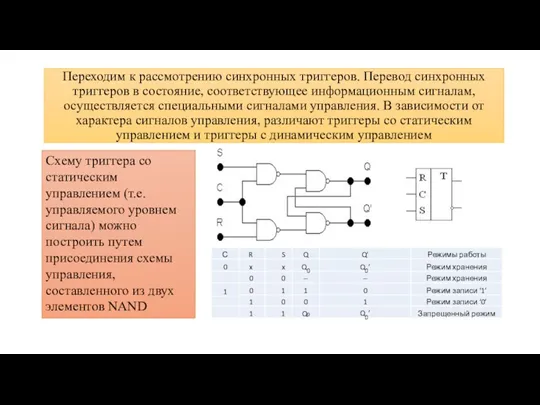

- 8. Переходим к рассмотрению синхронных триггеров. Перевод синхронных триггеров в состояние, соответствующее информационным сигналам, осуществляется специальными сигналами

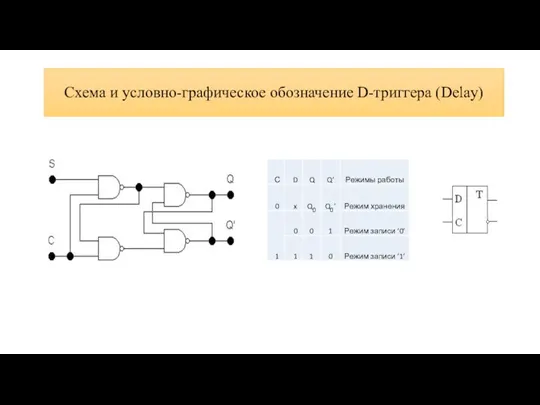

- 9. Схема и условно-графическое обозначение D-триггера (Delay)

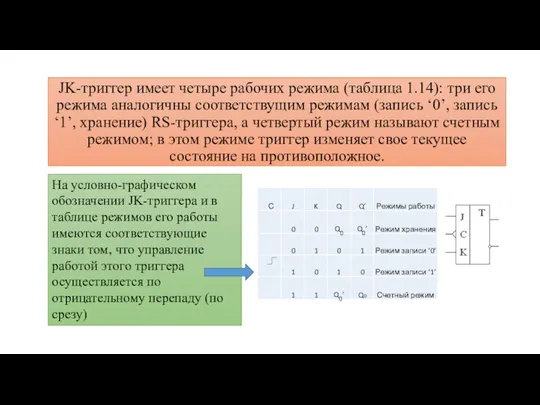

- 10. JK-триггер имеет четыре рабочих режима (таблица 1.14): три его режима аналогичны соответствущим режимам (запись ‘0’, запись

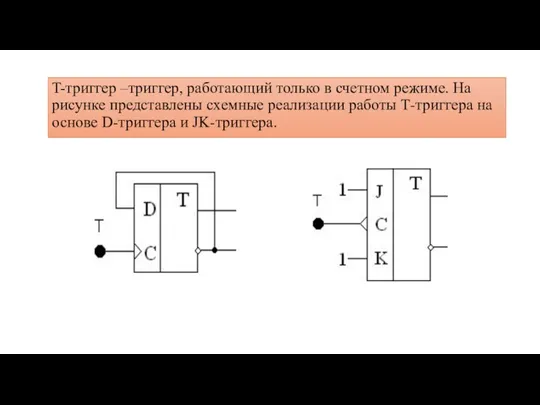

- 11. T-триггер –триггер, работающий только в счетном режиме. На рисунке представлены схемные реализации работы Т-триггера на основе

- 12. Контролные вопросы Последовательностные устройства? Триггер? Синхронные триггеры? Асинхронные триггеры? RS-триггер с прямыми входами? RS-триггер с инверсными

- 14. Скачать презентацию

Мамуля, с днём рождения

Мамуля, с днём рождения phpJS89XV_pamyatki-matem

phpJS89XV_pamyatki-matem Пасха - Светлое Воскресенье Господне

Пасха - Светлое Воскресенье Господне Поделки из помпонов

Поделки из помпонов Артикуляционная гимнастика (презентация)

Артикуляционная гимнастика (презентация) Управление качеством

Управление качеством Определение параллельных прямых. Секущая. Углы, образованные при пересечении двух прямых секущей

Определение параллельных прямых. Секущая. Углы, образованные при пересечении двух прямых секущей Zombie Apocalypse. EGE by helgabel

Zombie Apocalypse. EGE by helgabel Pu-239

Pu-239 Умные технологии в жилых помещениях. История появления. Технология и оборудование для систем умного дома

Умные технологии в жилых помещениях. История появления. Технология и оборудование для систем умного дома Внутренняя среда организма

Внутренняя среда организма Театрализованная деятельность как средство коррекции эмоционально-волевой сферы детей с задержкой психического развития

Театрализованная деятельность как средство коррекции эмоционально-волевой сферы детей с задержкой психического развития Продолжение портфолио Юбилей детского сада

Продолжение портфолио Юбилей детского сада Классный час. Тема: День пожилых людей.

Классный час. Тема: День пожилых людей. Класс Пресмыкающиеся (Рептилии)

Класс Пресмыкающиеся (Рептилии) Игра Что забыл нарисовать художник

Игра Что забыл нарисовать художник Соединительно-тканный массаж

Соединительно-тканный массаж Основы проектирования и оборудование биотехнологических производств

Основы проектирования и оборудование биотехнологических производств Arduino: умный дом

Arduino: умный дом Ощущения и виды ощущений

Ощущения и виды ощущений Презентация Мини-музея Игрушки

Презентация Мини-музея Игрушки Головоломки на разрезание

Головоломки на разрезание Интегрированный урок по истории и информатике в 7 классе на тему Культура России во второй половине 18 века. Защита проектов.

Интегрированный урок по истории и информатике в 7 классе на тему Культура России во второй половине 18 века. Защита проектов. Презентация к акции Весенние первоцветы

Презентация к акции Весенние первоцветы Презентация к уроку Семяя в православной традиции

Презентация к уроку Семяя в православной традиции Былины. Композиция былины

Былины. Композиция былины Три мира в романе М.А.Булгакова Мастер и Маргарита.

Три мира в романе М.А.Булгакова Мастер и Маргарита. Project Friends for life

Project Friends for life