Харьковский национальный университет радиоэлектроники

Кафедра КИТС Кораблев Н.М.

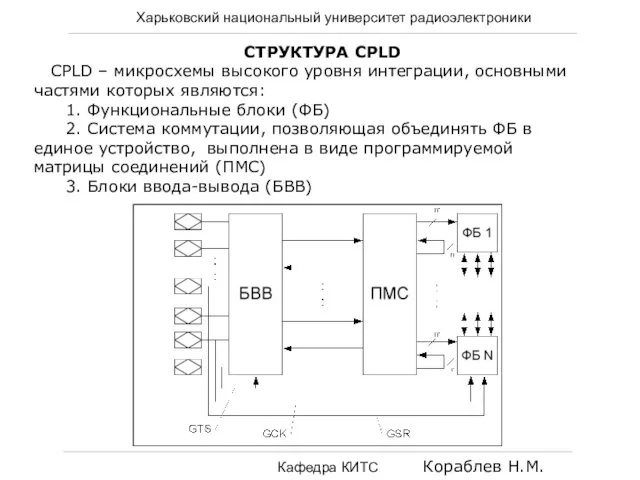

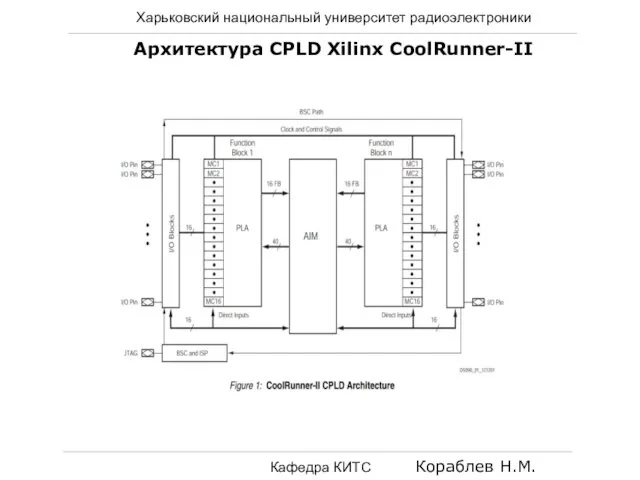

Архитектура CPLD Xilinx

CoolRunner-II

Основные функции:

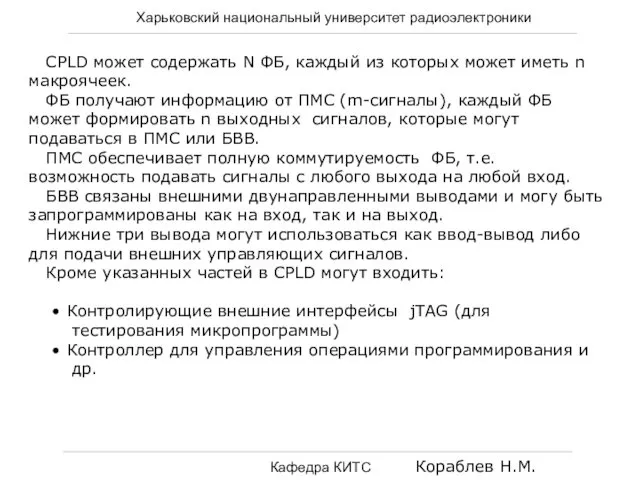

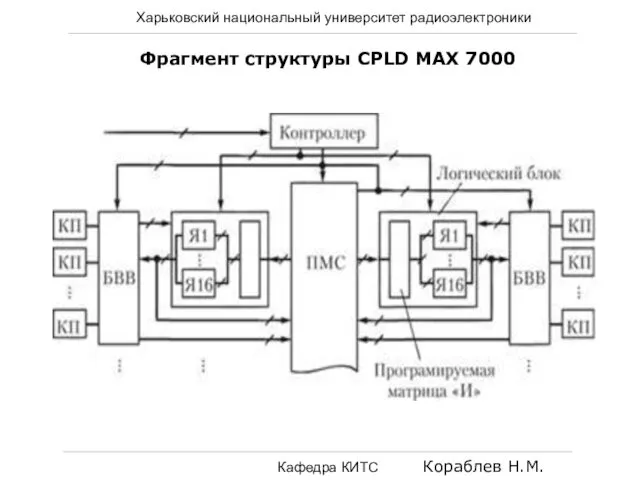

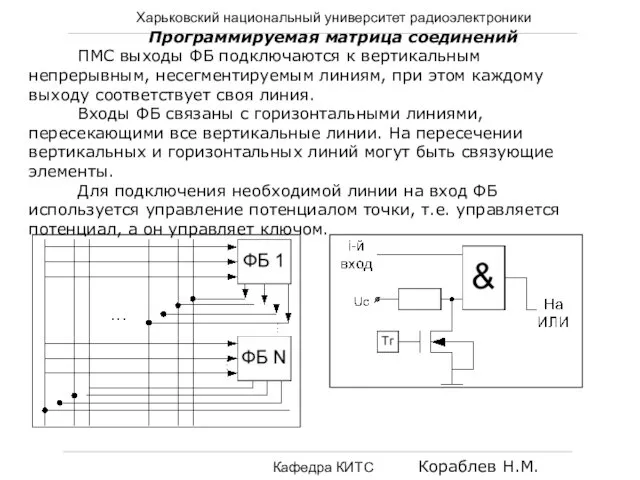

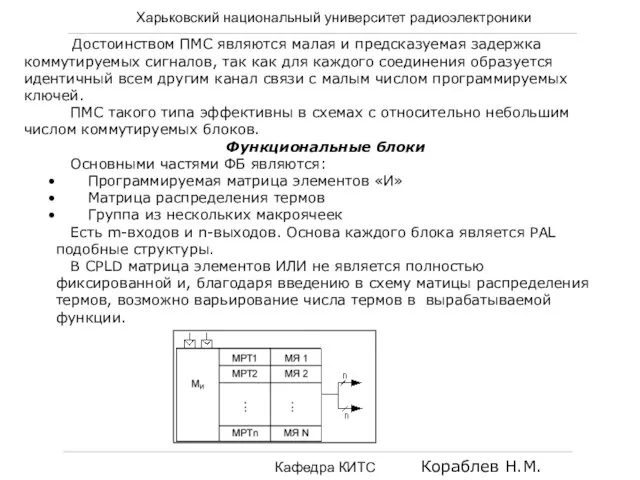

- Этот CPLD имеет несколько функциональных блоков, начиная с «Функционального блока 1» до «Функционального блока n» (это число колеблется от 2 до 32 в случае CPLD CoolRunner-II)

- 16 строк вывода из каждого функционального блока поступают в AIM (расширенную матрицу межсоединений), тогда как 40 строк сигналов вводятся в функциональные блоки из AIM.

- Каждый функциональный блок имеет 16 макроэлементов (от MC1 до MC16).

Каждый MacroCell имеет доступ к 16 сигналам из блоков ввода / вывода

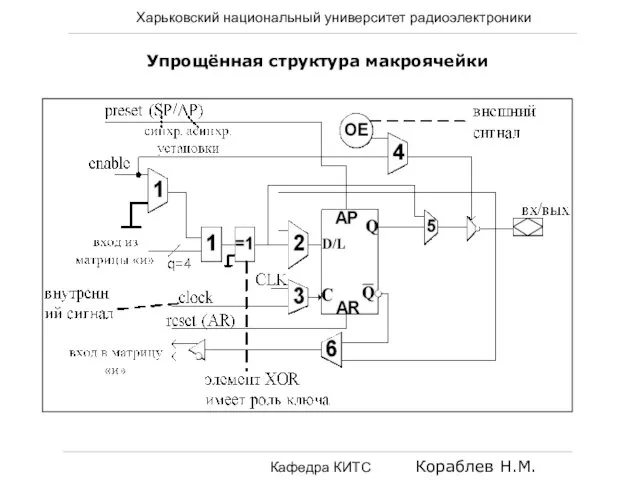

- Структура MacroCell показана ниже. Каждая макроячейка содержит 1 массив триггеров и PLA с суммой продуктов, которые пользователи могут использовать для создания комбинаторной или последовательной логики. Таким образом, максимальное число триггеров, доступных в CoolRunner-II CLPD (XC2C512), составляет 512! (Запомните это число, мы сравним его с количеством триггеров в FPGA)

- AIM может быть запрограммирован на соединение сигналов, как мы хотим. Но, как мы видели во втором пункте выше, количество сигналов ограничено для каждого функционального блока.

Проектная деятельность как составная часть современного образования

Проектная деятельность как составная часть современного образования Источники права

Источники права Современные строительные технологии

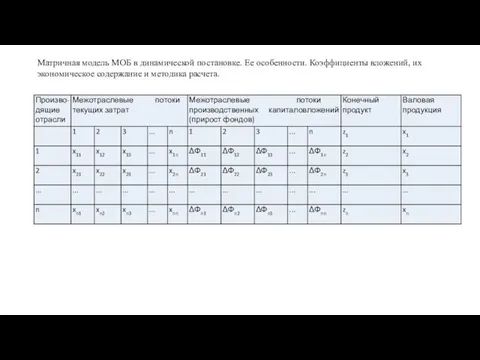

Современные строительные технологии Матричная модель МОБ в динамической постановке

Матричная модель МОБ в динамической постановке Христианство. Основные направления христианства – сравнительная характеристика

Христианство. Основные направления христианства – сравнительная характеристика Любимые игрушки. Лепка из пластилина

Любимые игрушки. Лепка из пластилина Реконструкция электрооборудования многоквартирного жилого дома

Реконструкция электрооборудования многоквартирного жилого дома Системы электронного документооборота

Системы электронного документооборота Наблюдение за состоянием пациентов и интенсивная терапия, во время анестезии

Наблюдение за состоянием пациентов и интенсивная терапия, во время анестезии Оперативная память

Оперативная память Блокада Ленинграда Диск

Блокада Ленинграда Диск Нефтегазоность Севернего Устюрта

Нефтегазоность Севернего Устюрта Формирование комфортной городской среды

Формирование комфортной городской среды Комплексная безопасность информационных систем. Асимметричные алгоритмы шифрования. (Лекция 8)

Комплексная безопасность информационных систем. Асимметричные алгоритмы шифрования. (Лекция 8) Food

Food История дорожного движения

История дорожного движения Презентация балет Щелкунчик П.И.Чайковский

Презентация балет Щелкунчик П.И.Чайковский презентация к занятию В гости к зайке

презентация к занятию В гости к зайке Дягилев

Дягилев Презентация MsPP Дни воинской славы России, часть 2

Презентация MsPP Дни воинской славы России, часть 2 Категорія числа іменників

Категорія числа іменників Космический КВН (презентация)

Космический КВН (презентация) Циркуляция вектора напряженности вихревого электрического поля

Циркуляция вектора напряженности вихревого электрического поля По следам рудознатцев

По следам рудознатцев КЛАССНЫЙ ЧАС

КЛАССНЫЙ ЧАС Zarządzanie procesami

Zarządzanie procesami Рибні консерви і ікра риб

Рибні консерви і ікра риб Австро-Венгрия в XIX - начале XX века

Австро-Венгрия в XIX - начале XX века