Содержание

- 2. Микропроцессор — это центральный блок персонального компьютера, предназначенный для управления работой всех остальных блоков и выполнения

- 3. Большинство современных процессоров для ПК основаны на циклическом процессе последовательной обработки информации, изобретённого Джоном фон Нейманом.

- 4. Скорость перехода от одного этапа цикла к другому определяется тактовым генератором. Тактовый генератор вырабатывает импульсы, служащие

- 5. Процессор выставляет число, хранящееся в регистре счётчика команд, на шину адреса, и отдаёт памяти команду чтения;

- 6. Процессор получает число с шины данных, интерпретирует его как команду (машинную инструкцию) из своей системы команд

- 7. Снова выполняется п. 1. Данный цикл выполняется неизменно, и именно он называется процессом (откуда и произошло

- 8. чтение и дешифрация команд из основной памяти; чтение данных из основной памяти и регистров адаптеров внешних

- 9. обработка данных и их запись в основную память и регистры адаптеров внешних устройств; выработка управляющих сигналов

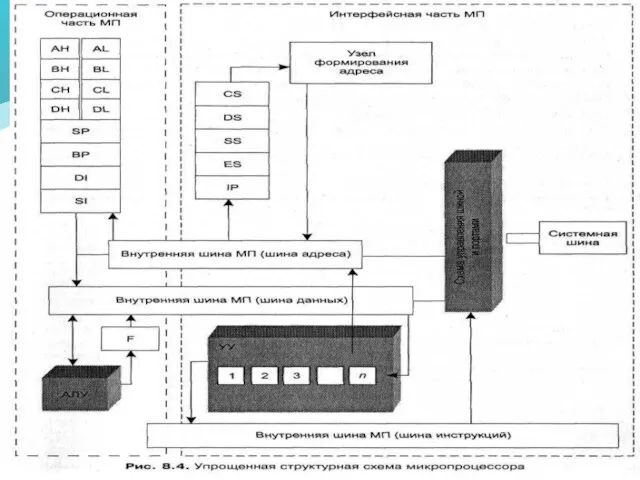

- 10. Арифметико-логическое устройство; Устройство управления; Микропроцессорная память; Интерфейсная система микропроцессора. Состав процессора:

- 12. Арифметико-логическое устройство (АЛУ) предназначено для выполнения арифметических и логических операций преобразования информации. Функционально в простейшем варианте

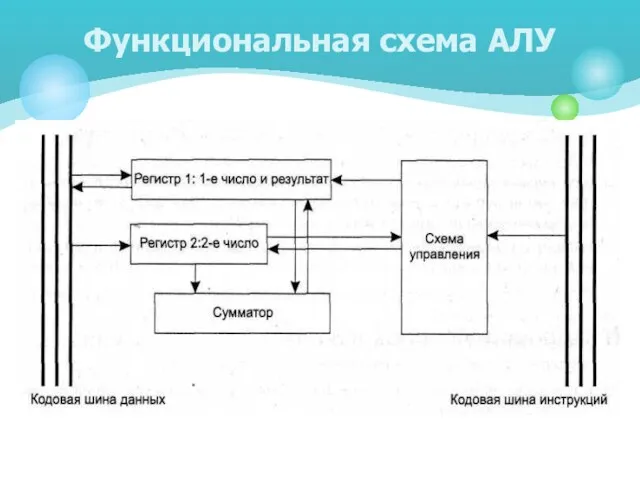

- 13. Функциональная схема АЛУ

- 14. Сумматор — вычислительная схема, выполняющая процедуру сложения поступающих на ее вход двоичных кодов; сумматор имеет разрядность

- 15. Регистры — быстродействующие ячейки памяти различной длины: регистр 1 имеет разрядность двойного слова, а регистр 2

- 16. Схемы управления принимают по кодовым шинам инструкций управляющие сигналы от устройства управления и преобразуют их в

- 17. АЛУ выполняет арифметические операции «+», «–», «×» и «÷» только над двоичной информацией с запятой, фиксированной

- 18. Выполнение операций над двоичными числами с плавающей запятой и над двоично-кодированными десятичными числами осуществляется с привлечением

- 19. Устройство управления координирует взаимодействие различных частей компьютера. Выполняет следующие основные функции: 2. Устройство управления (УУ)

- 20. формирует и подает во все блоки машины в нужные моменты времени определенные сигналы управления (управляющие импульсы),

- 21. формирует адреса ячеек памяти, используемых выполняемой операцией, и передает эти адреса в соответствующие блоки компьютера; получает

- 22. Упрощенная функциональная схема УУ

- 23. регистр команд — запоминающий регистр, в котором хранится код команды: код выполняемой операции (КОП) и адреса

- 24. дешифратор операций — логический блок, выбирающий в соответствии с поступающим из регистра команд кодом операции (КОП)

- 25. узел формирования адреса (находится в интерфейсной части МП) — устройство, вычисляющее полный адрес ячейки памяти (регистра)

- 26. Микропроцессорная память предназначена для кратковременного хранения, записи и выдачи информации, используемой в вычислениях непосредственно в ближайшие

- 27. Микропроцессорная память строится на регистрах и используется для обеспечения высокого быстродействия компьютера, так как основная память

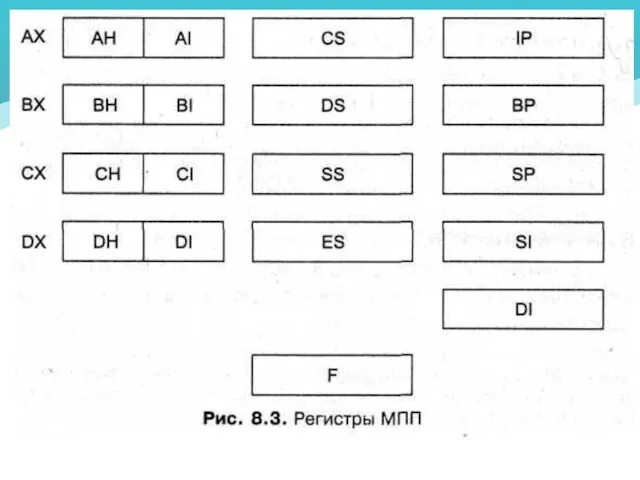

- 29. Все регистры можно разделить на четыре группы: универсальные регистры: АХ, ВХ, СХ, DX; сегментные регистры: CS,

- 30. Регистры АХ, ВХ, СХ и DX являются универсальными (их часто называют регистрами общего назначения — РОН);

- 31. каждый из них может использоваться для временного хранения любых данных, при этом позволено работать с каждым

- 32. регистр АХ — регистр-аккумулятор, через его порты осуществляется ввод-вывод данных в МП, а при выполнении операций

- 33. регистр ВХ часто используется для хранения адреса базы в сегменте данных и начального адреса поля памяти

- 34. регистр СХ — регистр-счетчик, используется как счетчик числа повторений при циклических операциях;

- 35. регистр DX используется как расширение регистра-аккумулятора при работе с 32-разрядными числами и при выполнении операций умножения

- 36. Регистры сегментной адресации CS, DS, SS, ES используются для хранения начальных адресов полей памяти (сегментов), отведенных

- 37. Регистры смещений (внутрисегментной адресации) IP, SP, BP, SI, DI предназначены для хранения относительных адресов ячеек памяти

- 38. регистр SP (Slack Pointer) смещение вершины стека (текущего адреса стека); регистр BP (Base Pointer) — смещение

- 39. Регистр флагов F содержит условные одноразрядные признаки-маски, или флаги, управляющие прохождением программы в ПК; флаги работают

- 40. Всего в регистре содержится 9 флагов: 6 из них статусные, они отражают результаты операций, выполненных в

- 41. Статусные флаги: CF (Carry Flag) — флаг переноса. Содержит значение «переносов» (0 или 1) из старшего

- 42. Статусные флаги: AF (Auxiliary Carry Flag) — флаг логического переноса в двоично-десятичной арифметике. Вспомогательный флаг переноса

- 43. Статусные флаги: SF (Sign Flag) — флаг знака. Устанавливается в соответствии со знаком результата после арифметических

- 44. Управляющие флаги: TF (Trap Flag) — флаг системного прерывания (трассировки). Единичное состояние этого флага переводит процессор

- 45. Управляющие флаги: DF (Direction Flag) — флаг направления. Используется в строковых операциях для задания направления обработки

- 46. Интерфейсная часть МП предназначена для связи и согласования МП с системной шиной ПК, а также для

- 47. Порты ввода-вывода - это пункты системного интерфейса ПК, через которые МП обменивается информацией с другими устройствами.

- 48. Схема управления шиной и портами выполняет следующие функции: формирование адреса порта и управляющей информации для него

- 50. Скачать презентацию

Путешествие по родному краю. Конкурсы

Путешествие по родному краю. Конкурсы Курсовое проектирование как одна из форм подготовки конкурентоспособного специалиста

Курсовое проектирование как одна из форм подготовки конкурентоспособного специалиста Развитие социологии (до 1940-х гг.)

Развитие социологии (до 1940-х гг.) American history

American history Презентация Открытка к 8 марта

Презентация Открытка к 8 марта Технологиялық машиналар және жабдықтар

Технологиялық машиналар және жабдықтар Итоговое сочинение. Критерии оценивания

Итоговое сочинение. Критерии оценивания Проектная задача Буклет для дошкольника

Проектная задача Буклет для дошкольника Лазерная физика. Основные задачи курса

Лазерная физика. Основные задачи курса Буровые растворы. Бурение нефтяных и газовых скважин

Буровые растворы. Бурение нефтяных и газовых скважин Ранние формы религии. Часть I

Ранние формы религии. Часть I Анализ аптечного ассортимента лекарственного растительного сырья, содержащего эфирные масла и препаратов из него

Анализ аптечного ассортимента лекарственного растительного сырья, содержащего эфирные масла и препаратов из него Машины для противоэрозионной обработки почв

Машины для противоэрозионной обработки почв Урок химии в 8 классе Обобщающее повторение по теме сложные вещества

Урок химии в 8 классе Обобщающее повторение по теме сложные вещества Транспортная логистика. (Раздел 2.3)

Транспортная логистика. (Раздел 2.3) Психолого-педагогическое сопровождение семьи, воспитывающей ребенка раннего и дошкольного возраста

Психолого-педагогическое сопровождение семьи, воспитывающей ребенка раннего и дошкольного возраста Строительство поверхностной обработки покрытий

Строительство поверхностной обработки покрытий Doping-legalization

Doping-legalization Русская народная сказка Теремок

Русская народная сказка Теремок красивая речь ребенка

красивая речь ребенка Значение и перспективы развития тары и упаковки в управлении товародвижением в компании “СПСР экспресс”

Значение и перспективы развития тары и упаковки в управлении товародвижением в компании “СПСР экспресс” Давление. 7 класс

Давление. 7 класс Une petite histoire

Une petite histoire Военнослужащие и взаимоотношения между ними

Военнослужащие и взаимоотношения между ними Морфофункциональная характеристика скелета и аппарата движения нижних конечностей человека

Морфофункциональная характеристика скелета и аппарата движения нижних конечностей человека Медиация равных

Медиация равных род.собрание

род.собрание Смешанное вскармливание. Лекция

Смешанное вскармливание. Лекция