Содержание

- 2. Экономическая целесообразность использования микроконтроллеров STM32 Современный уровень развития технологии обеспечил возможность создания микроконтроллеров с 32- битной

- 3. Компания STMicroelectronics разрабатывала 32 -битные микроконтроллеры на основе ядер ARM7 и ARM9 Новое поколение 32- битных

- 4. Архитектура микроконтроллеров STM32 Микроконтроллеры семейства STM32 выполнены на основе ядра Cortex-M3, которое подключено к flash-памяти по

- 5. Обзор платформы STM32 Микроконтроллеры STM32 изначально выпускались в 14 различных вариантах, разделенные на две группы: Performance

- 6. Группа Performance Line (рабочие частоты до 72 МГц)

- 7. Группа Aссess Line (тактовая частота до 36 МГц)

- 8. Микроконтроллеры работают от 2В-ого источника питания на тактовой частоте 72МГц и потребляют с учетом нахождения в

- 9. Линейка микроконтроллеров STM32

- 10. АРХИТЕКТУРА

- 11. NVIC – неотъемлемая часть процессора Cortex-M3. Модуль NVIC в процессоре Cortex-M3 осуществляет обработку прерываний аппаратными средствами.

- 12. Шинная матрица (Bus matrix) Шинная матрица — это развитие идеи простого контроллера шины: здесь шины соединены

- 13. Ядро Cortex-M3 Выполняет инструкции, производит вычисления в своём арифметико-логическом устройстве (АЛУ) Его Гарвардская архитектура позволяет одновременно

- 14. СИСТЕМНОЕ ПРОГРАММИРОВАНИЕ

- 15. Библиотека поддержки ядра Ядро ARM Cortex-M3 выходит за рамки обычного понятия ядра микроконтроллера и представляет собой

- 16. Структура CMSIS CMSIS состоит из трех файлов: core_m3.h - вспомогательные функции доступа к регистрам ядра; startup_stm32f10x_xx.s

- 17. Стандартная библиотека STM32 Стандартная библиотека для работы с периферийными модулями написана в соответствии со стандартом ANSI

- 18. Модификация библиотек Библиотека содержит три файла, доступные для модификации пользователем: файл конфигурации библиотеки stm32f10x_conf.h файлы обработчиков

- 19. ПРОГРАММНО-ИНСТРУМЕНТАЛЬНАЯ СРЕДА

- 20. Выбор программного инструментария под ARM-архитектуру

- 21. ОСВОЕНИЕ ПЛАТФОРМЫ

- 22. Отладочная плата STM32VLDiscovery Плата реализована на микроконтроллере линейки «Value Line» STM32F100RBT6 Имеет программатор-отладчик ST-Link с выведенным

- 24. Скачать презентацию

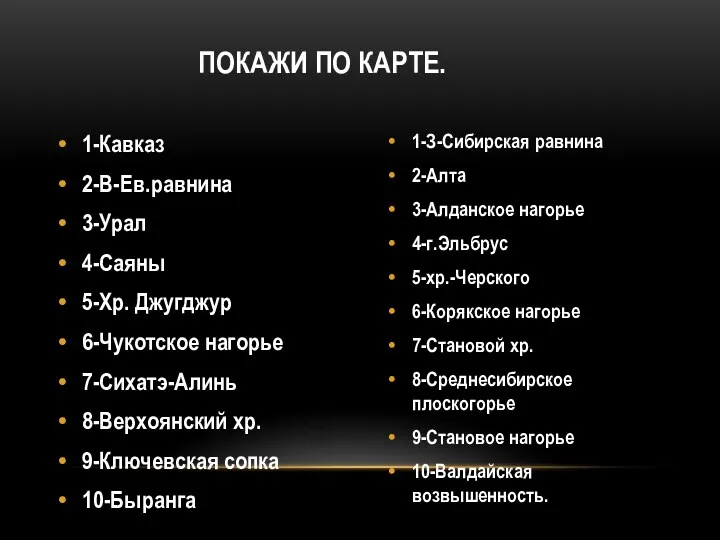

Итоговый контроль по теме Рельеф России 8кл

Итоговый контроль по теме Рельеф России 8кл 20231130_prezentatsiya1_0

20231130_prezentatsiya1_0 Кислотность почвы

Кислотность почвы Кислоты

Кислоты Ecological problems Climate change

Ecological problems Climate change Система управления безопасностью полетов эксплуатанта. Управление факторами риска

Система управления безопасностью полетов эксплуатанта. Управление факторами риска Вода- самое удивительное вещество в природе.

Вода- самое удивительное вещество в природе. Илон Ривс. Основатель компаний SpaceX и X.com

Илон Ривс. Основатель компаний SpaceX и X.com Презентация аппликация Разноцветный дождик

Презентация аппликация Разноцветный дождик Здравствуй солнышко!

Здравствуй солнышко! Поражающие факторы ядерного оружия

Поражающие факторы ядерного оружия Люминесцентный анализ пищевых продуктов

Люминесцентный анализ пищевых продуктов Презентация к уроку технологии 1 класс Работа с бумагой. Коллаж Дикие животные. Проектная деятельность на уроке технологии.

Презентация к уроку технологии 1 класс Работа с бумагой. Коллаж Дикие животные. Проектная деятельность на уроке технологии. Понятие многогранника

Понятие многогранника Настоящая любовь

Настоящая любовь Обучение учащихся с помощью серий задач на уроках математики

Обучение учащихся с помощью серий задач на уроках математики Эволюция ОС Windows. Рождение операционной системы Windows

Эволюция ОС Windows. Рождение операционной системы Windows Внешняя политика СССР в 1964-1985 гг

Внешняя политика СССР в 1964-1985 гг Биоенергетика. Общие пути катаболизма

Биоенергетика. Общие пути катаболизма Ребенок - пешеход как участник дорожного движения

Ребенок - пешеход как участник дорожного движения Подготовка руд к плавке и производство чугуна. Раздел 2

Подготовка руд к плавке и производство чугуна. Раздел 2 Коллекторского агентство ООО АврораКонсалт. Предложение о продаже

Коллекторского агентство ООО АврораКонсалт. Предложение о продаже Дробление. Биологическое значение дробления

Дробление. Биологическое значение дробления Парка станцій. Призначення і позначення парків.Види

Парка станцій. Призначення і позначення парків.Види Согласный звук [Ф] - [Ф’]. Буквы Ф, ф

Согласный звук [Ф] - [Ф’]. Буквы Ф, ф советы выпускникам

советы выпускникам Консультация для воспитателей

Консультация для воспитателей Газобаллонное оборудование четвертого поколения

Газобаллонное оборудование четвертого поколения