Содержание

- 2. Уровни абстракции

- 3. Принстонская архитектура

- 4. Гарвардская архитектура

- 5. Архитектуры CISC и RISC

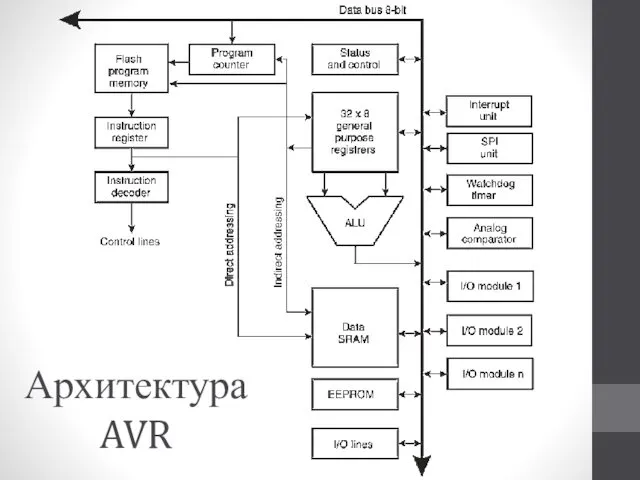

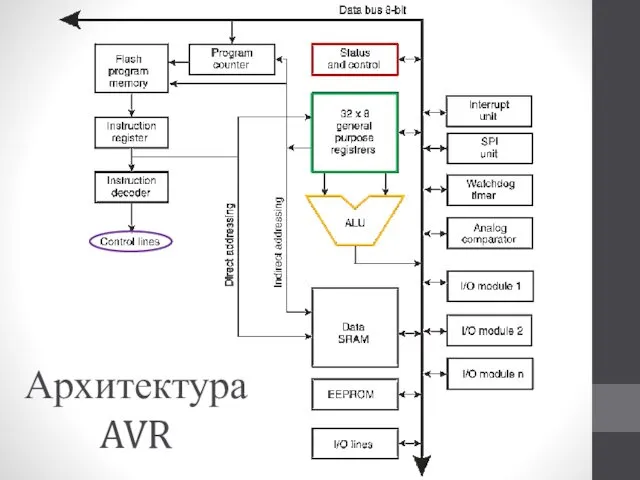

- 6. Архитектура AVR

- 7. Транзистор – всему голова База Эмиттер Коллектор Транзистор – это кнопка, которая нажимается не пальцем, а

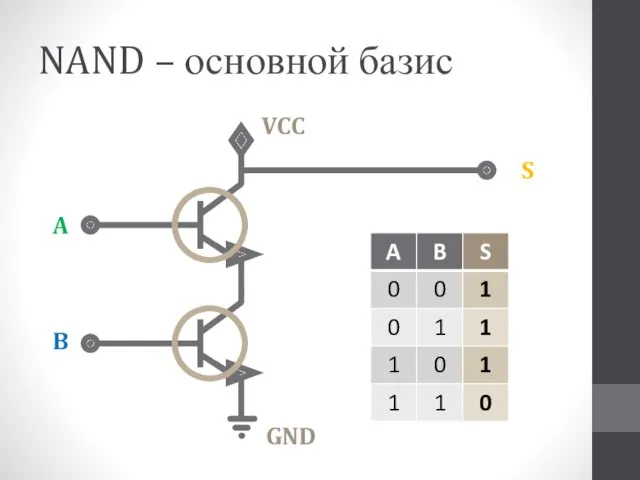

- 8. NAND – основной базис GND VCC A B S

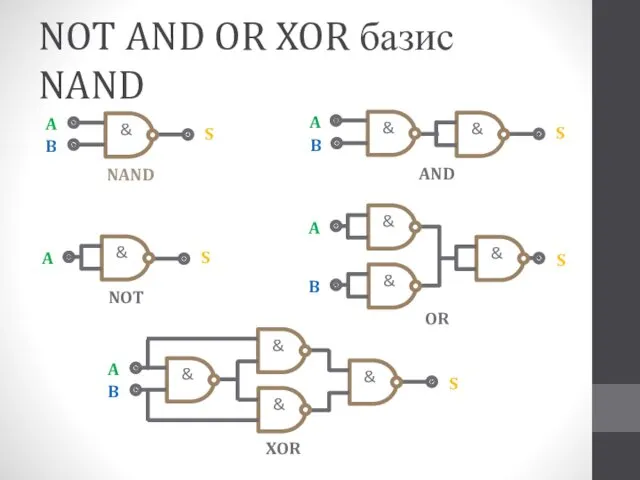

- 9. NOT AND OR XOR базис NAND

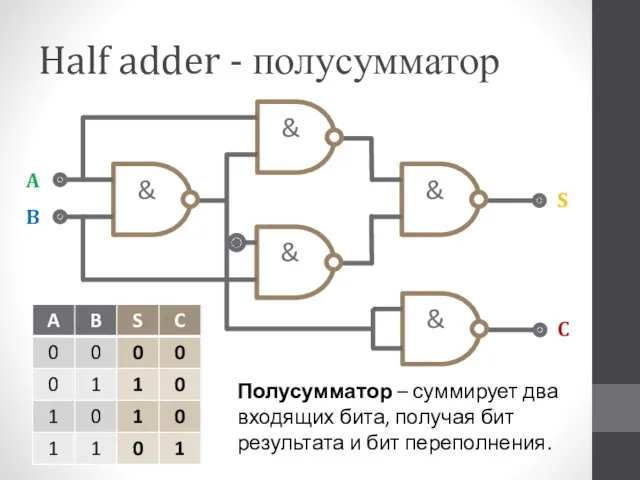

- 10. Half adder - полусумматор Полусумматор – суммирует два входящих бита, получая бит результата и бит переполнения.

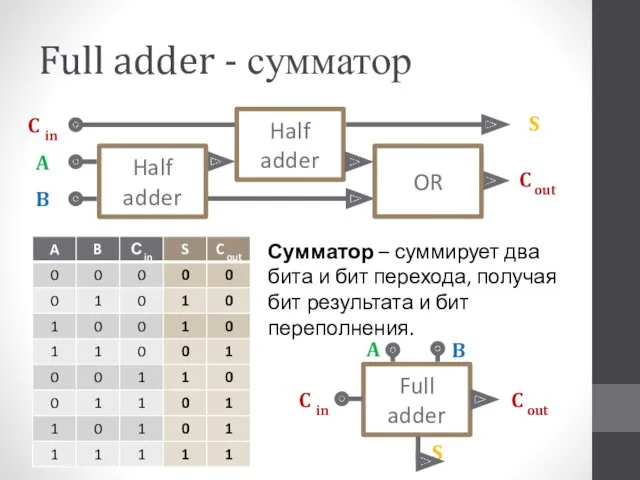

- 11. Full adder - сумматор A B S Half adder S C out Half adder OR Сумматор

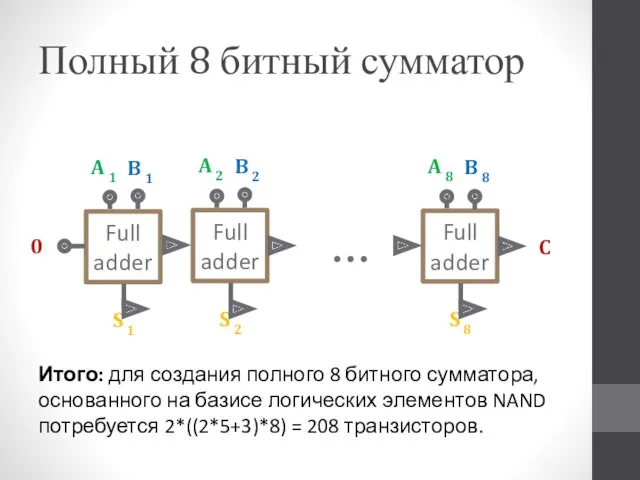

- 12. Полный 8 битный сумматор Итого: для создания полного 8 битного сумматора, основанного на базисе логических элементов

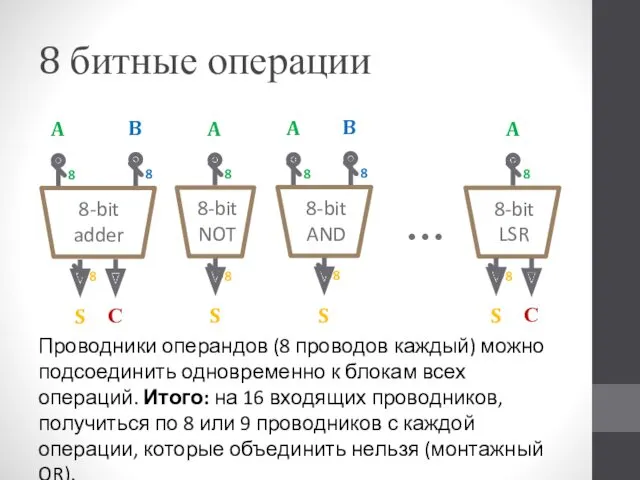

- 13. 8 битные операции Проводники операндов (8 проводов каждый) можно подсоединить одновременно к блокам всех операций. Итого:

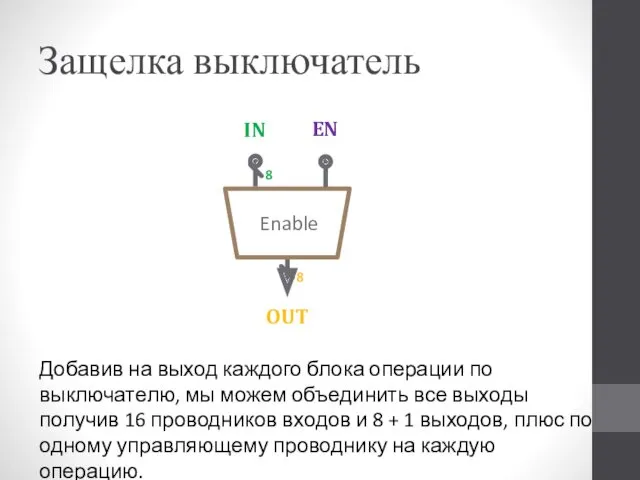

- 14. Защелка выключатель Добавив на выход каждого блока операции по выключателю, мы можем объединить все выходы получив

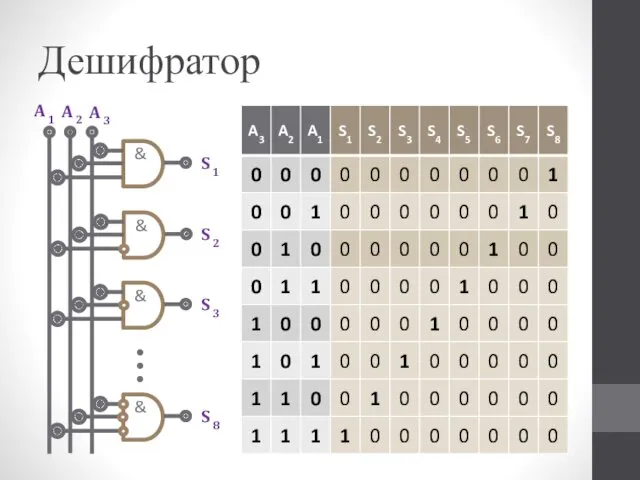

- 15. Дешифратор

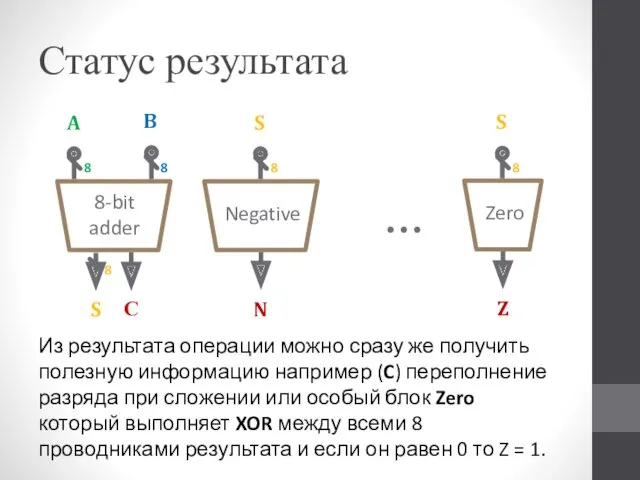

- 16. Статус результата Из результата операции можно сразу же получить полезную информацию например (C) переполнение разряда при

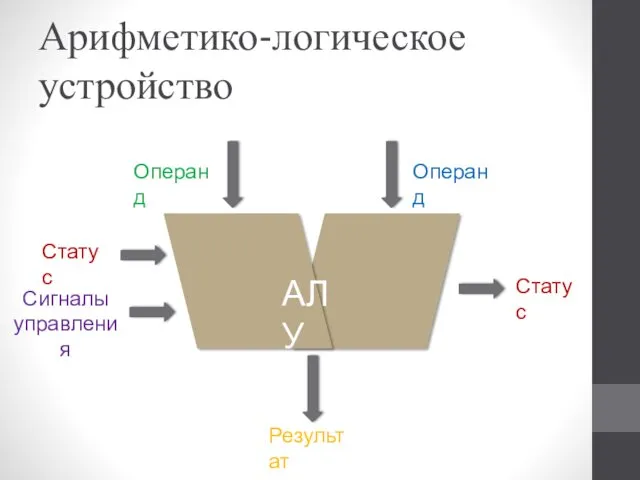

- 17. Арифметико-логическое устройство Операнд Операнд Статус Статус Сигналы управления Результат АЛУ

- 18. Архитектура AVR

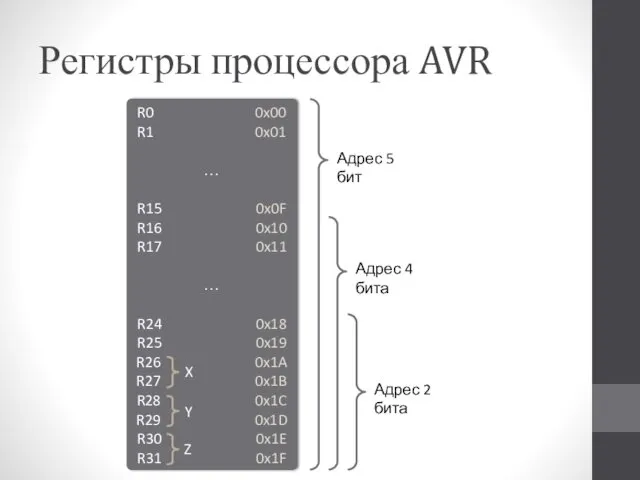

- 19. R0 0x00 R1 0x01 … R15 0x0F R16 0x10 R17 0x11 … R24 0x18 R25 0x19

- 20. Память AVR

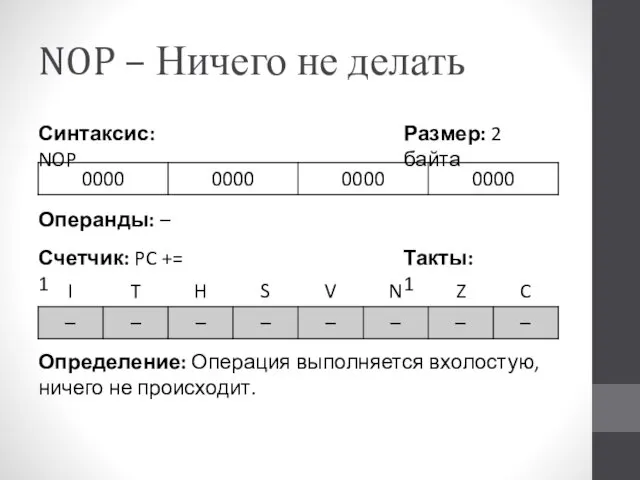

- 21. NOP – Ничего не делать Определение: Операция выполняется вхолостую, ничего не происходит. Синтаксис: NOP Размер: 2

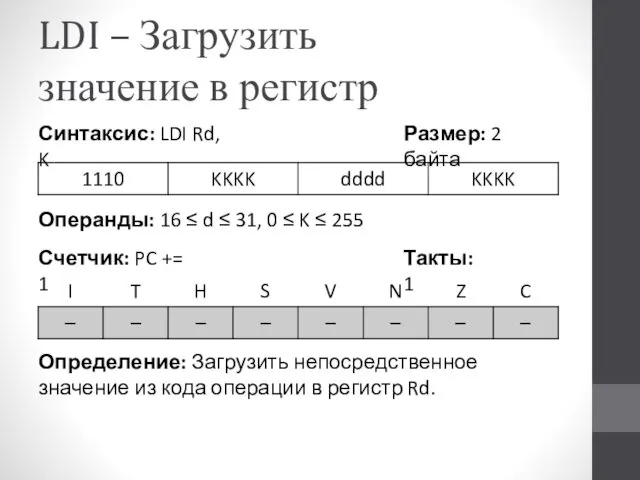

- 22. LDI – Загрузить значение в регистр Определение: Загрузить непосредственное значение из кода операции в регистр Rd.

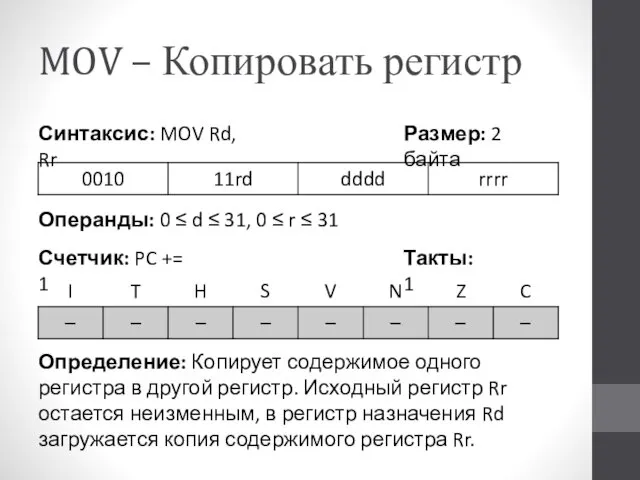

- 23. MOV – Копировать регистр Определение: Копирует содержимое одного регистра в другой регистр. Исходный регистр Rr остается

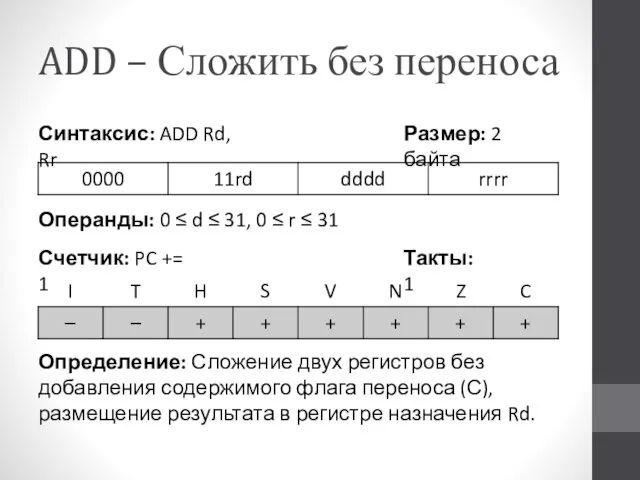

- 24. ADD – Сложить без переноса Определение: Сложение двух регистров без добавления содержимого флага переноса (С), размещение

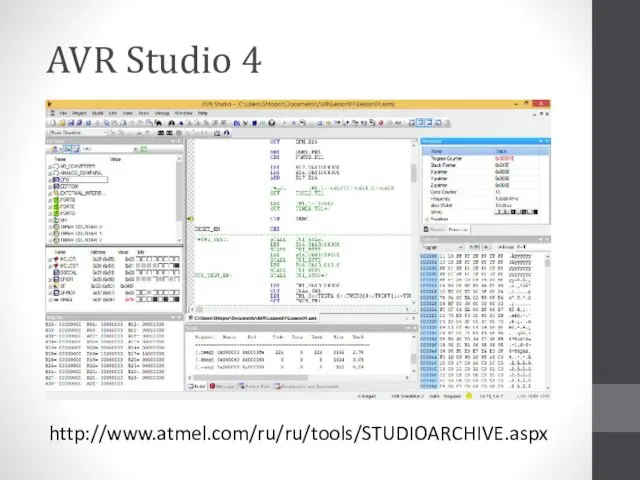

- 25. AVR Studio 4 http://www.atmel.com/ru/ru/tools/STUDIOARCHIVE.aspx

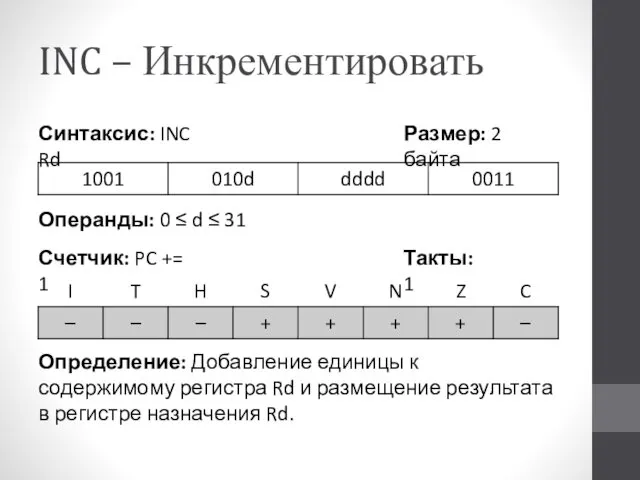

- 26. INC – Инкрементировать Определение: Добавление единицы к содержимому регистра Rd и размещение результата в регистре назначения

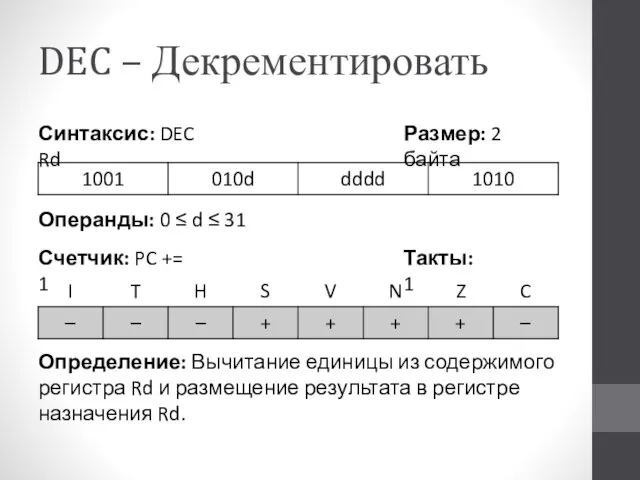

- 27. DEC – Декрементировать Определение: Вычитание единицы из содержимого регистра Rd и размещение результата в регистре назначения

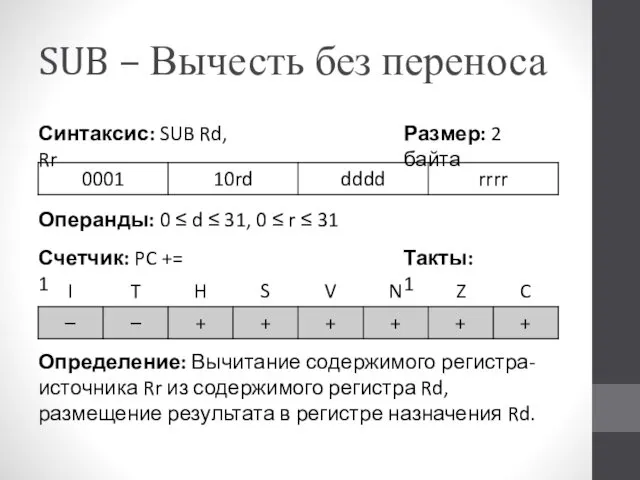

- 28. SUB – Вычесть без переноса Определение: Вычитание содержимого регистра-источника Rr из содержимого регистра Rd, размещение результата

- 30. Скачать презентацию

Знакомство с редактором Visual Basic. Принципы создания собственных макросов. Средства отладки

Знакомство с редактором Visual Basic. Принципы создания собственных макросов. Средства отладки Потоки в сетях. Задача о максимальном потоке

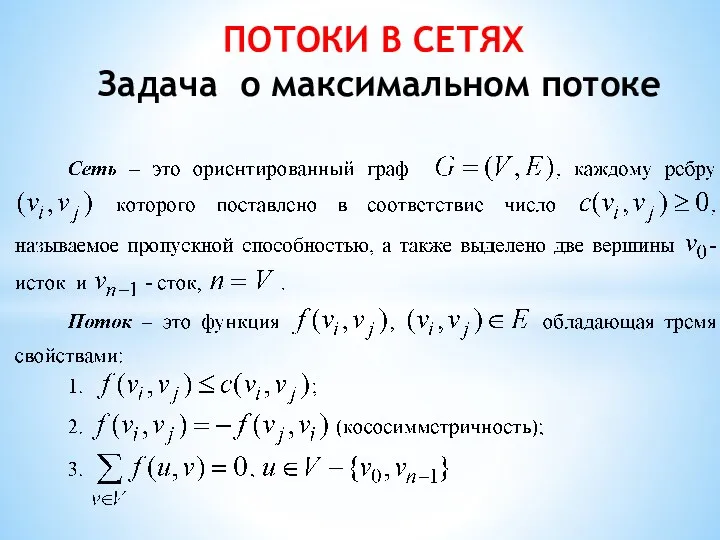

Потоки в сетях. Задача о максимальном потоке Команды общего назначения

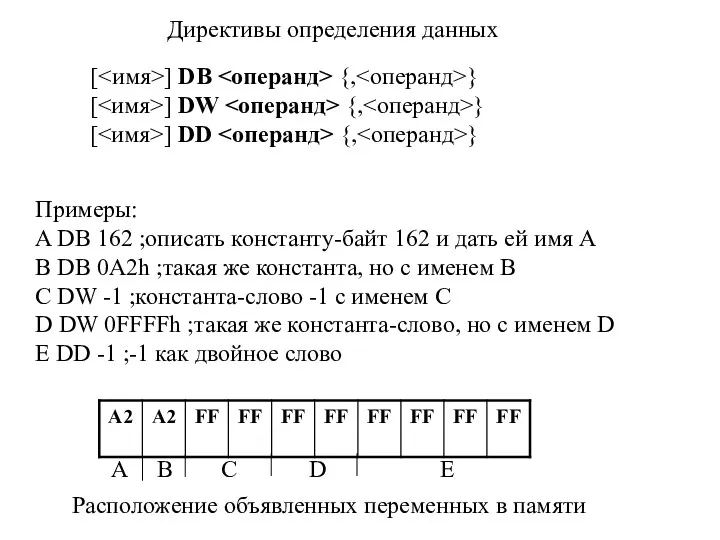

Команды общего назначения Файл и файловые системы

Файл и файловые системы Шаблони в мові С++

Шаблони в мові С++ Информационные технологии. Visual Basic

Информационные технологии. Visual Basic Современные направления в развитии информационного обеспечения логистики

Современные направления в развитии информационного обеспечения логистики Развертка YII2. Установка Open Server. Установка YII2

Развертка YII2. Установка Open Server. Установка YII2 Creating Session Beans

Creating Session Beans Кіберспорт. Історія електронного спорту

Кіберспорт. Історія електронного спорту Web-страницы. Язык HTML и др

Web-страницы. Язык HTML и др Краткая характеристика содержания произведения печати или рукописи - аннотация

Краткая характеристика содержания произведения печати или рукописи - аннотация Флешь - анимация

Флешь - анимация Тестирование программного обеспечения

Тестирование программного обеспечения AT Command Server. Marvell Confidentia

AT Command Server. Marvell Confidentia 123

123 Анализ угроз информационной безопасности (1). Лекция 4

Анализ угроз информационной безопасности (1). Лекция 4 Электронные ресурсы для науки и образования. Тенденции развития библиотечно-информационного обслуживания

Электронные ресурсы для науки и образования. Тенденции развития библиотечно-информационного обслуживания Топ 5 популярных видео-блогеров

Топ 5 популярных видео-блогеров Создание документов средствами текстового процессора

Создание документов средствами текстового процессора Платформа – основа бизнеса и вечный источник колиентов

Платформа – основа бизнеса и вечный источник колиентов Программное обеспечение компьютера

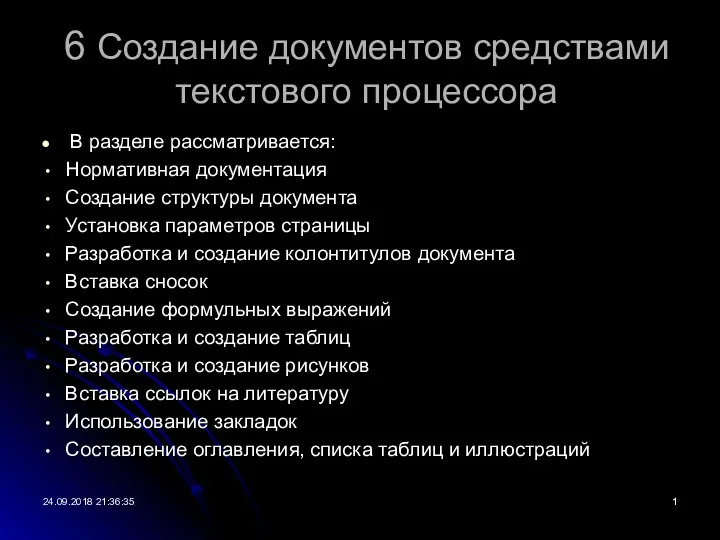

Программное обеспечение компьютера Проектирование изделий из листового металла в NX

Проектирование изделий из листового металла в NX Информационные технологии обучения персонала. Состав базы данных для определения потребности в обучении:

Информационные технологии обучения персонала. Состав базы данных для определения потребности в обучении: Архитектура ПК

Архитектура ПК Графический редактор

Графический редактор Видеосистема. Теоретические основы

Видеосистема. Теоретические основы Servlet. Epam Java training

Servlet. Epam Java training