Содержание

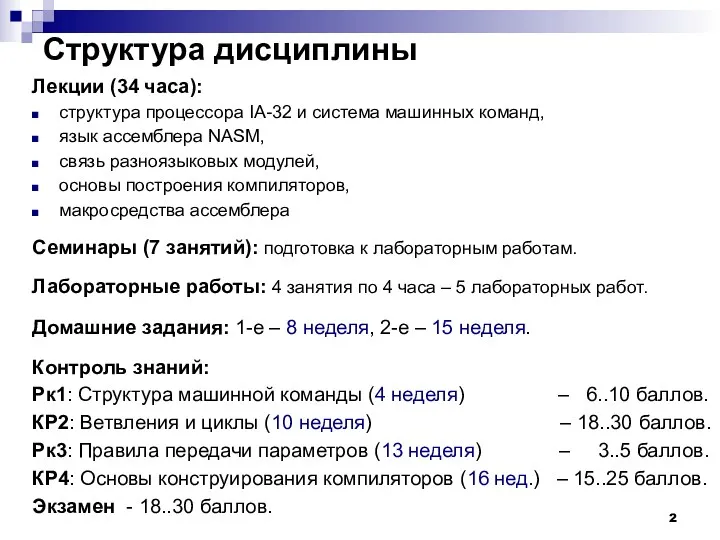

- 2. Структура дисциплины Лекции (34 часа): структура процессора IA-32 и система машинных команд, язык ассемблера NASM, связь

- 3. Цели и задачи дисциплины Цель дисциплины: изучение программирования на языках низкого уровня и основ конструирования компиляторов

- 4. Литература не покрывает курса! Основная литература Г.С. Иванова, Т.Н. Ничушкина. Главы 1-4. Учебные пособия в эл.

- 5. Глава 1 Организация ядра ЭВМ на базе IA-32 МГТУ им. Н.Э. Баумана Факультет Информатика и системы

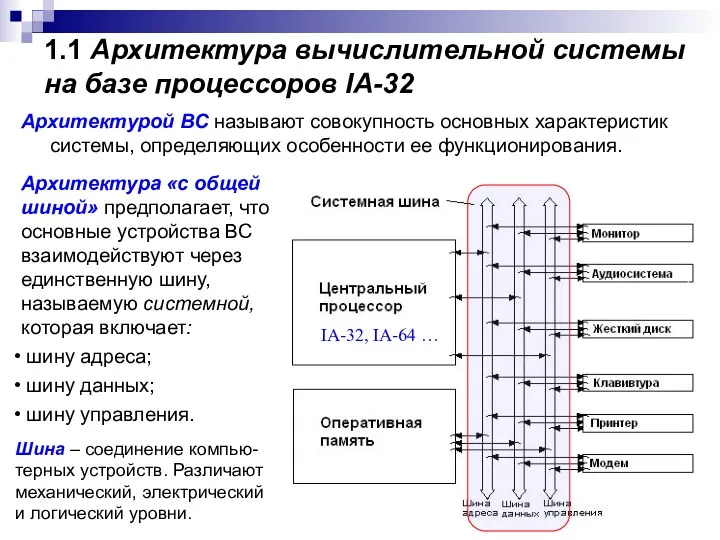

- 6. 1.1 Архитектура вычислительной системы на базе процессоров IA-32 Архитектурой ВС называют совокупность основных характеристик системы, определяющих

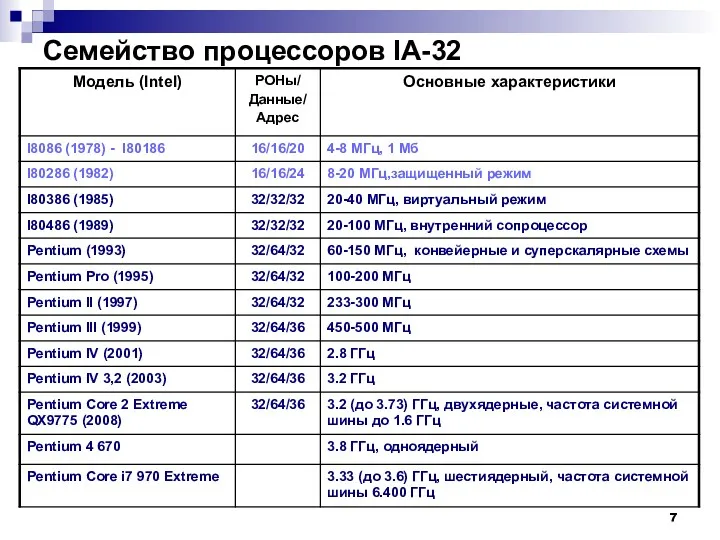

- 7. Семейство процессоров IA-32

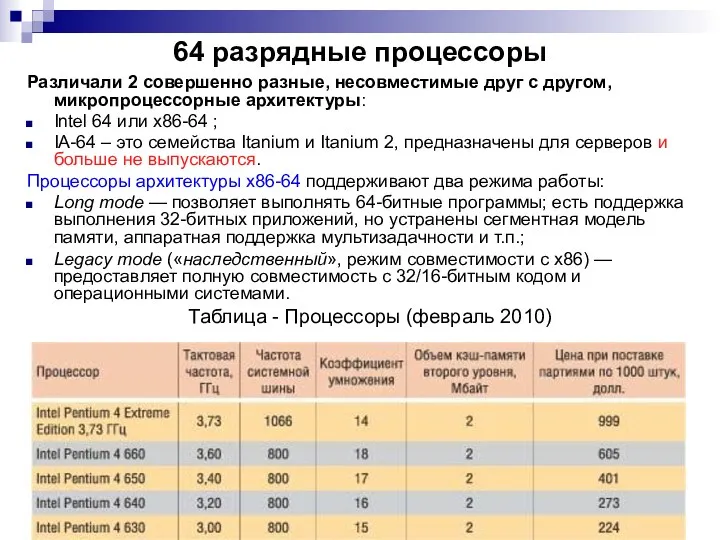

- 8. 64 разрядные процессоры Различали 2 совершенно разные, несовместимые друг с другом, микропроцессорные архитектуры: Intel 64 или

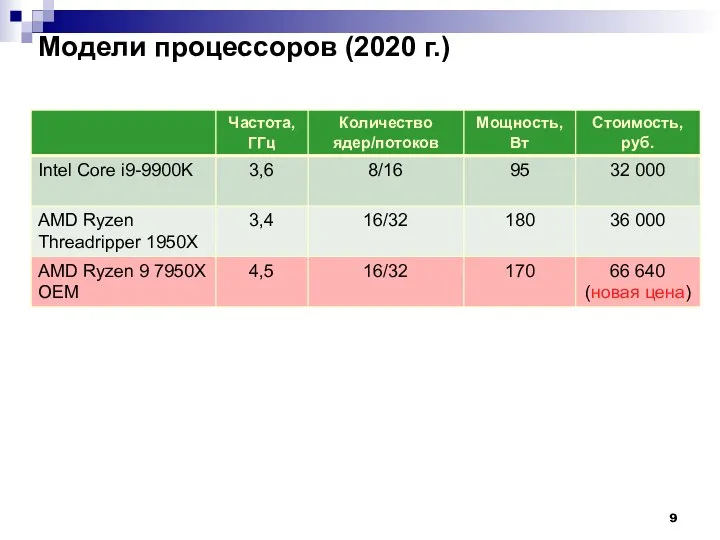

- 9. Модели процессоров (2020 г.)

- 10. 1.2 Программная модель процессора i8086 Под программной моделью процессора понимается совокупность его характеристик, существенных для разработки

- 11. Оперативная память Оперативная память ВС организована как последовательность бай-тов, которым соответствуют номера – целые числа от

- 12. Типы обрабатываемых данных целые числа – представляются в двоичной системе счисления, со знаком или без знака,

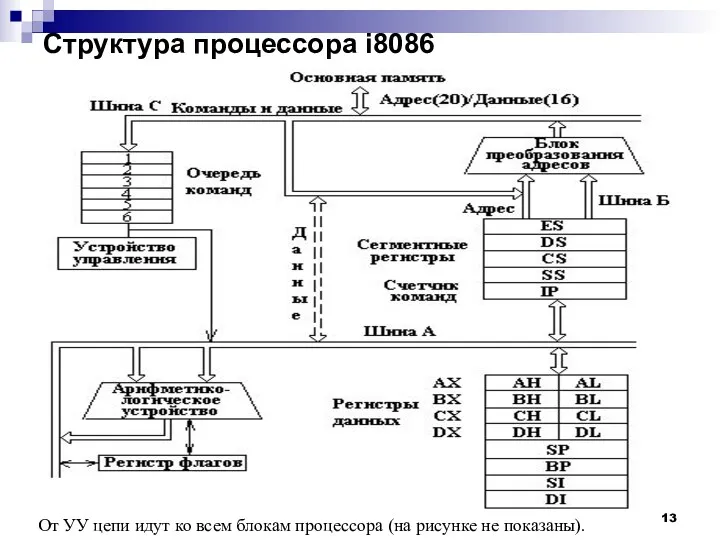

- 13. Структура процессора i8086 От УУ цепи идут ко всем блокам процессора (на рисунке не показаны).

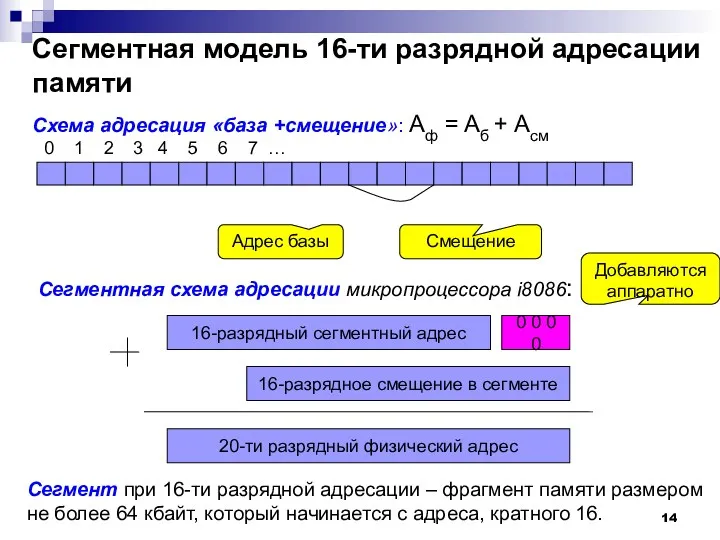

- 14. Сегментная модель 16-ти разрядной адресации памяти 0 1 2 3 4 5 6 7 … Адрес

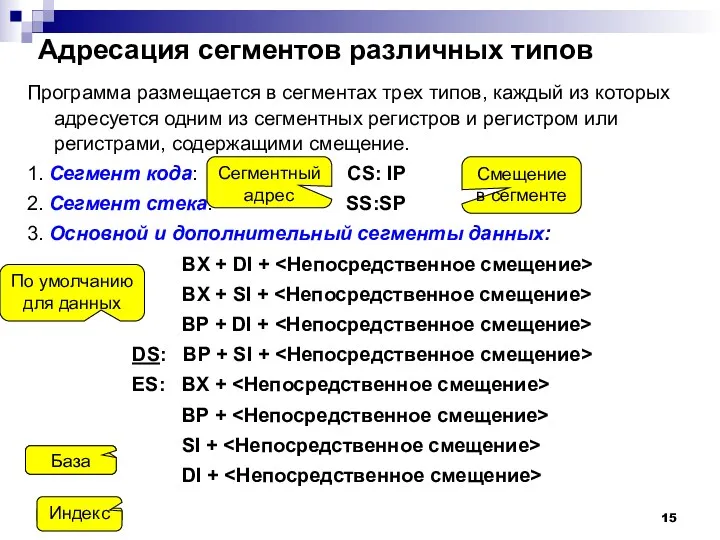

- 15. Адресация сегментов различных типов Программа размещается в сегментах трех типов, каждый из которых адресуется одним из

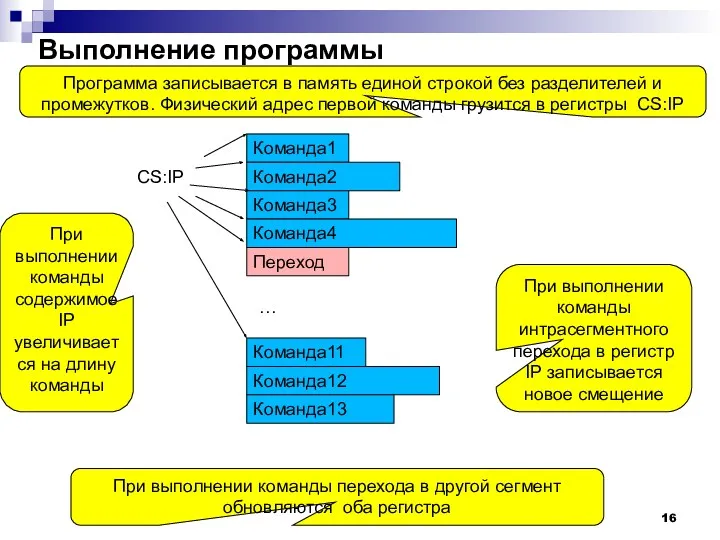

- 16. Выполнение программы Программа записывается в память единой строкой без разделителей и промежутков. Физический адрес первой команды

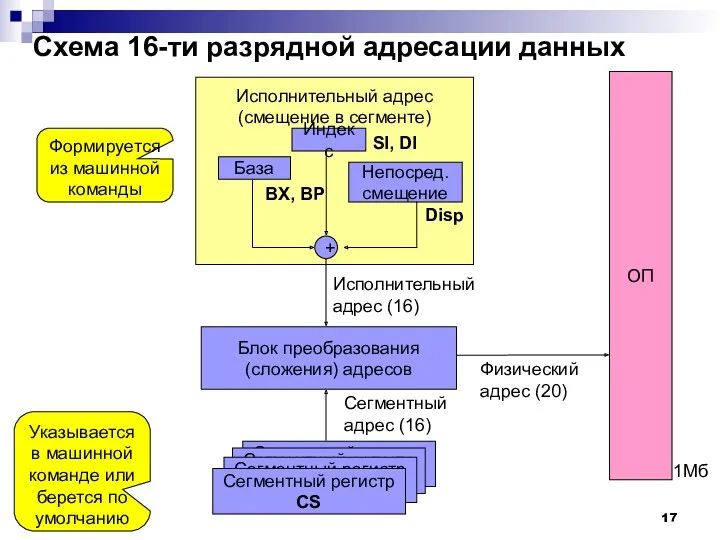

- 17. Схема 16-ти разрядной адресации данных Исполнительный адрес (смещение в сегменте) База Индекс Непосред. смещение + Блок

- 18. Система машинных команд i8086. Форматы команды MOV D - 1- в регистр, 0 - из регистра

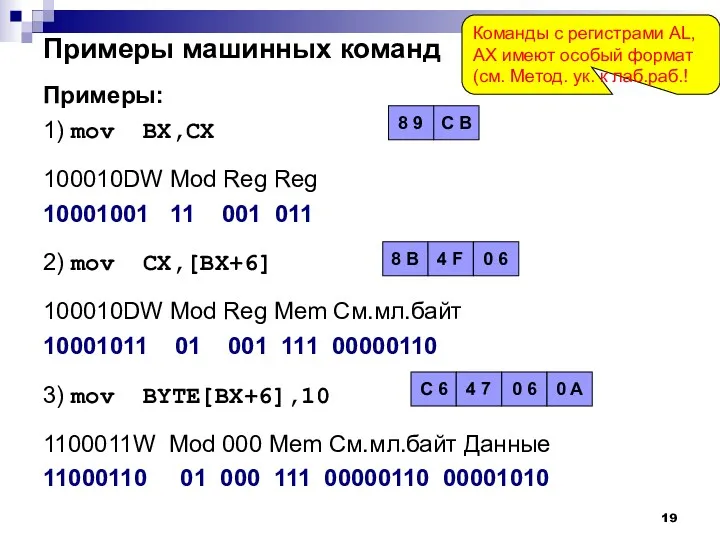

- 19. Примеры машинных команд Примеры: 1) mov BX,CX 100010DW Mod Reg Reg 10001001 11 001 011 2)

- 20. 1.3 Программная модель процессоров IA-32 Процессоры IA-32 могут функционировать в одном из трех режимов: реальной адресации

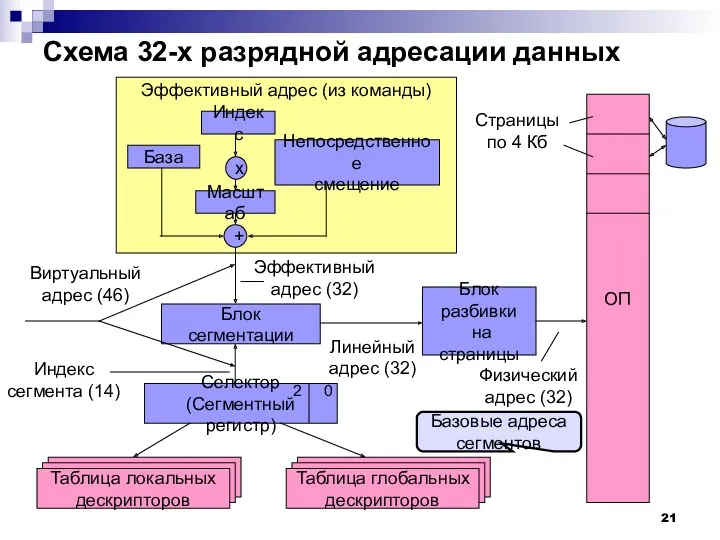

- 21. Эффективный адрес (из команды) Схема 32-х разрядной адресации данных База Индекс Непосредственное смещение Масштаб x +

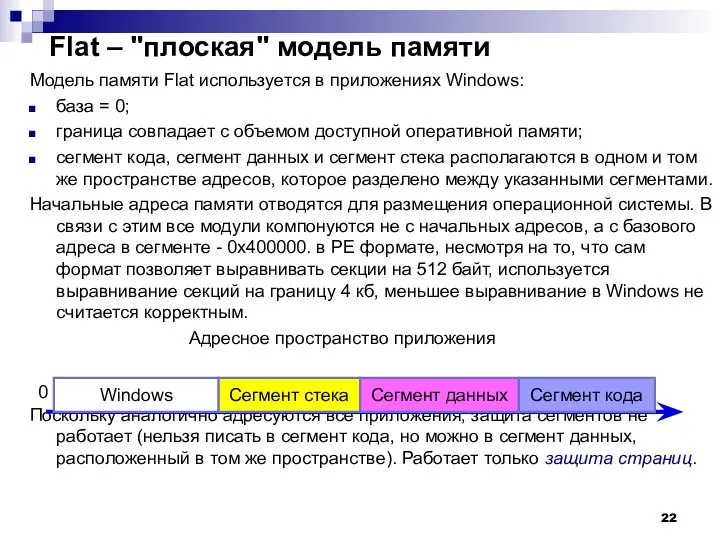

- 22. Flat – "плоская" модель памяти Модель памяти Flat используется в приложениях Windows: база = 0; граница

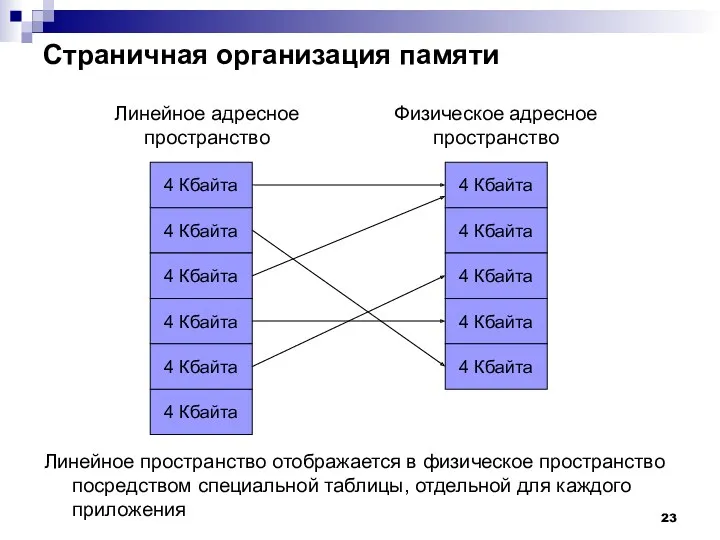

- 23. Страничная организация памяти 4 Кбайта 4 Кбайта 4 Кбайта 4 Кбайта 4 Кбайта 4 Кбайта 4

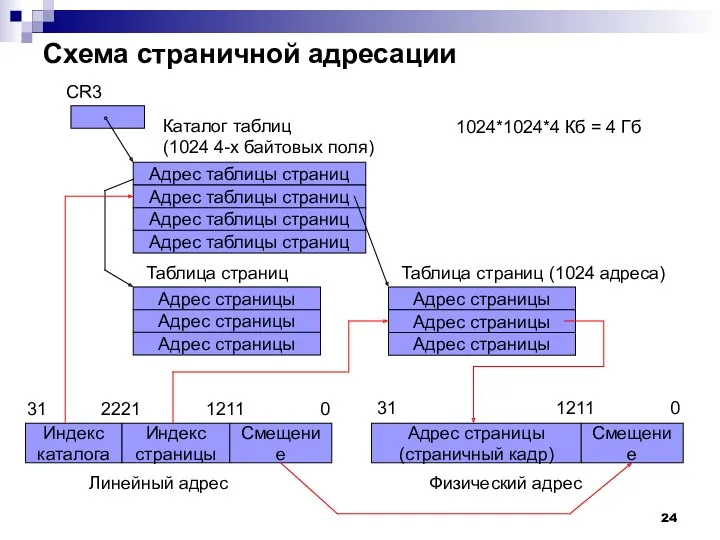

- 24. Схема страничной адресации Адрес таблицы страниц Адрес таблицы страниц Адрес таблицы страниц Адрес таблицы страниц Адрес

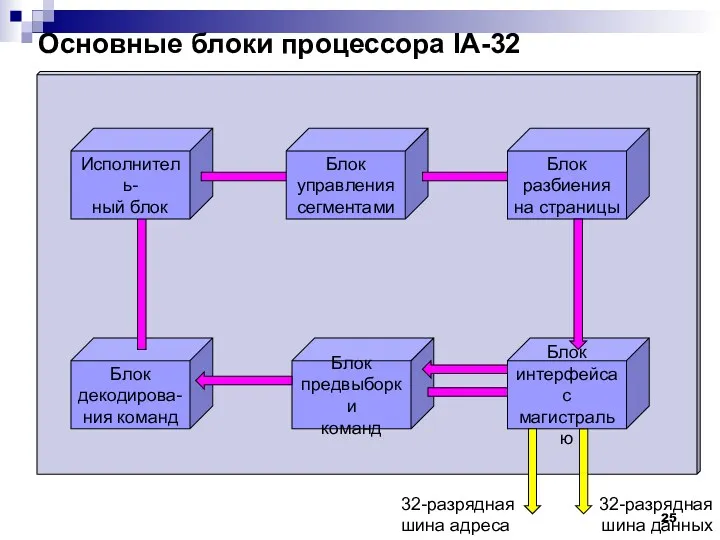

- 25. Основные блоки процессора IA-32 Блок декодирова- ния команд Блок предвыборки команд Исполнитель- ный блок Блок управления

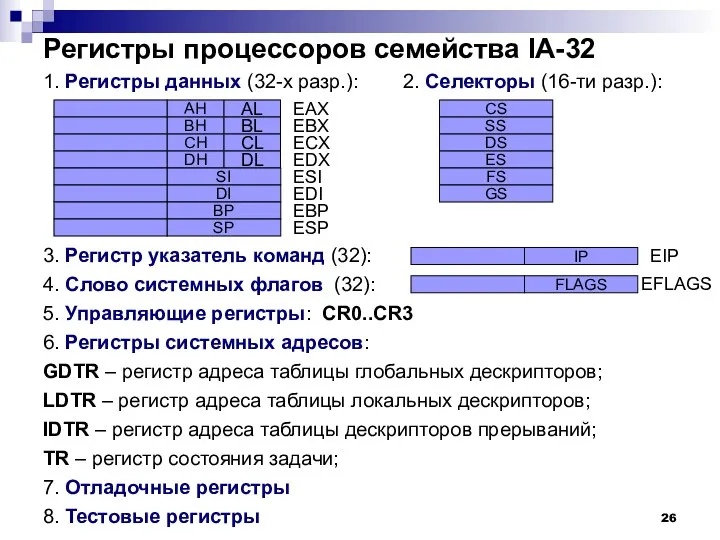

- 26. Регистры процессоров семейства IA-32 1. Регистры данных (32-х разр.): 2. Селекторы (16-ти разр.): 3. Регистр указатель

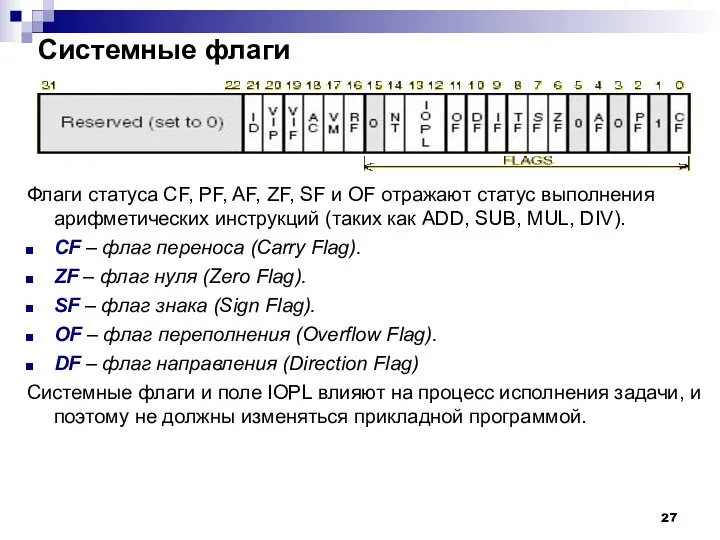

- 27. Системные флаги Флаги статуса CF, PF, AF, ZF, SF и OF отражают статус выполнения арифметических инструкций

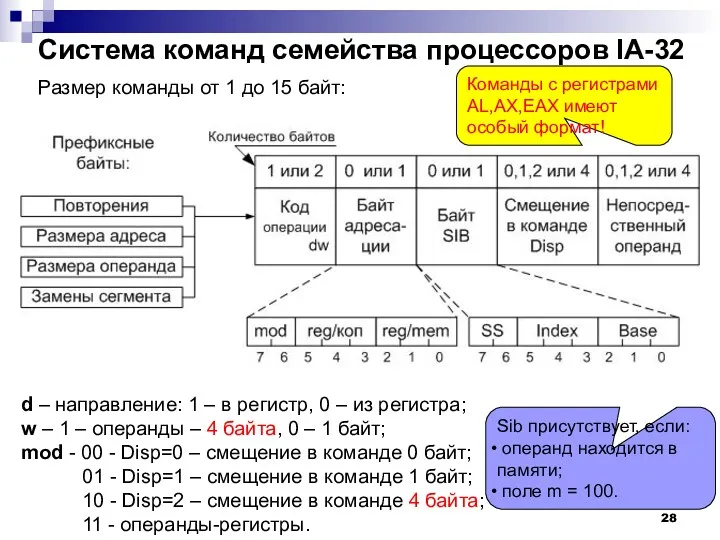

- 28. Система команд семейства процессоров IA-32 Размер команды от 1 до 15 байт: d – направление: 1

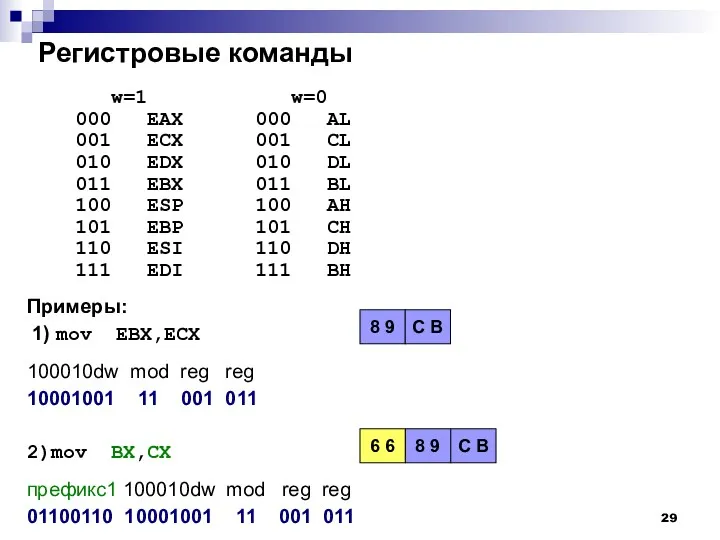

- 29. Регистровые команды w=1 w=0 000 EAX 000 AL 001 ECX 001 CL 010 EDX 010 DL

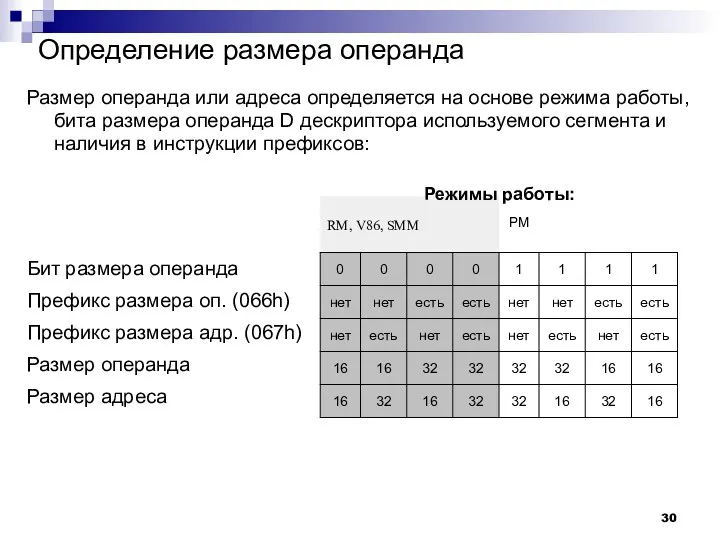

- 30. Определение размера операнда Размер операнда или адреса определяется на основе режима работы, бита размера операнда D

- 31. Схемы адресации памяти без байта Sib 1) mov ECX, [DS:EBX+6] 100010dw mod reg mem cм.мл.байт 10001011

- 32. Схемы адресации памяти без байта Sib (2) 4) mov ECX, [DS:BX+6] префикс 100010dw mod reg mem

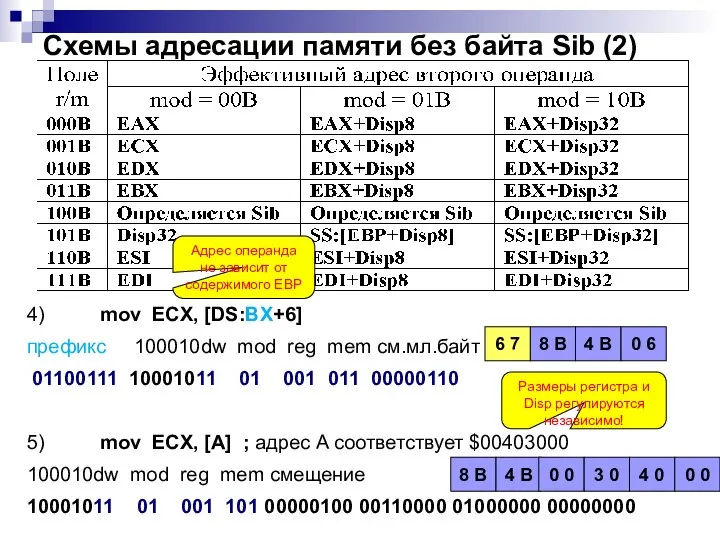

- 33. Схемы адресации памяти с байтом Sib ss – масштаб; index – индексный регистр; base – базовый

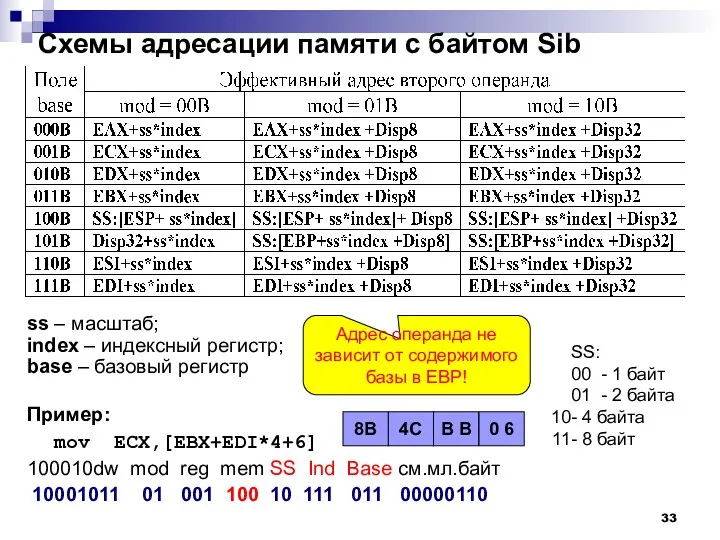

- 35. Скачать презентацию

![Схемы адресации памяти без байта Sib 1) mov ECX, [DS:EBX+6]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/608399/slide-30.jpg)

Возможности динамических (электронных) таблиц

Возможности динамических (электронных) таблиц Performance Evaluation of Real-Time Operating Systems

Performance Evaluation of Real-Time Operating Systems Линейное программирование

Линейное программирование Подпрограммы в языке Паскаль

Подпрограммы в языке Паскаль Основные понятия и определения информатики. Часть 3

Основные понятия и определения информатики. Часть 3 Администрирование информационных систем. Введение

Администрирование информационных систем. Введение Нормализация. Получение реляционной схемы из ER-схемы

Нормализация. Получение реляционной схемы из ER-схемы Режимы и способы обработки данных

Режимы и способы обработки данных Разработка клиентских веб-приложений

Разработка клиентских веб-приложений Измерение информации. Алфавитный подход

Измерение информации. Алфавитный подход Компьютерные сети

Компьютерные сети Сервер InterBase

Сервер InterBase Дискретная математика: теория алгоритмов и сложность вычислений

Дискретная математика: теория алгоритмов и сложность вычислений Computers keyboard

Computers keyboard Захист інформації та як сервіс Електронної бібліотеки

Захист інформації та як сервіс Електронної бібліотеки Кодування інформації

Кодування інформації Основные сведения об автоматизированных системах управления химикотехнологическими системами. Назначение и основные функции

Основные сведения об автоматизированных системах управления химикотехнологическими системами. Назначение и основные функции Глобальна комп'ютерна мережа

Глобальна комп'ютерна мережа Multithreading. User Group’s Web Site

Multithreading. User Group’s Web Site Модели и моделирование

Модели и моделирование Застосунок моніторингу роботи віддалених пристроїв шляхом віртуалізації USB-інтерфейсу

Застосунок моніторингу роботи віддалених пристроїв шляхом віртуалізації USB-інтерфейсу Программирование на языке Python. Базовый уровень. Модуль 2. Строки и списки. Списки (занятие 1)

Программирование на языке Python. Базовый уровень. Модуль 2. Строки и списки. Списки (занятие 1) Оптическое волокно в сети доступа

Оптическое волокно в сети доступа Автоматизация процессного управления

Автоматизация процессного управления Логические задачи и способы их решения

Логические задачи и способы их решения Деревья. Лекция 5

Деревья. Лекция 5 Computer

Computer Алгоритм создания объемной детали в Компас-3D LT

Алгоритм создания объемной детали в Компас-3D LT