Слайд 2

Goal

Build an AI for connect-5 (Gomoku) in FPGA hardware and leverage

Vivado’s High Level Synthesis functions

The AI should run faster than its software counterpart running on a top of the line general purpose PC

The AI should be competitive with software AIs on Gomocup

Слайд 3

Literature Review

Began by looking at papers from ICFPT design competition

2013: Blokus

2012:

Connect-6 Variant

Most papers use a board evaluation function and brute force every possible

Sometimes search forward n-ply using a minimax tree, but cannot examine every move

Слайд 4

Board Evaluation

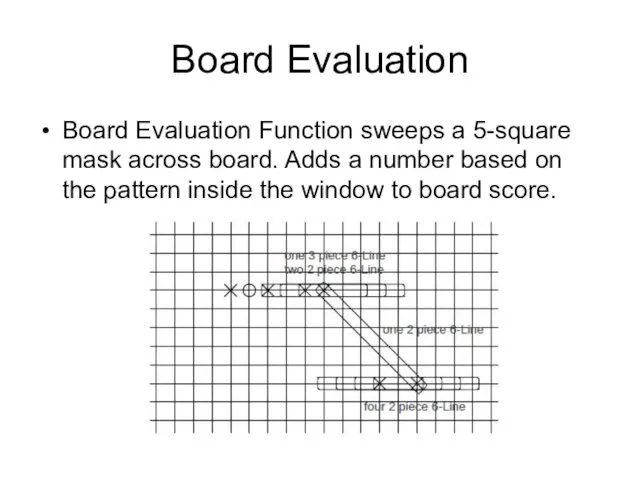

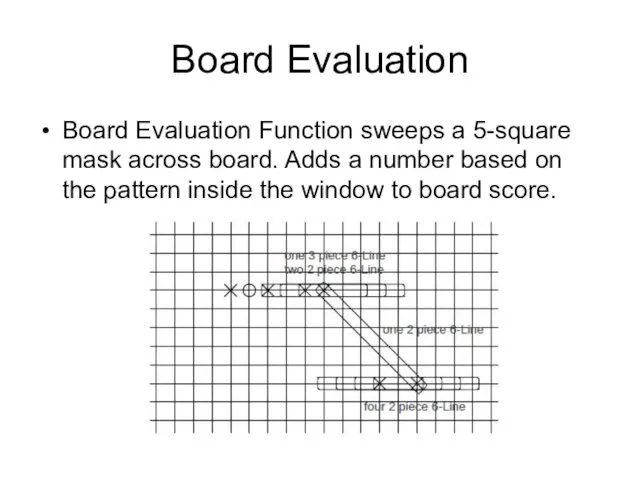

Board Evaluation Function sweeps a 5-square mask across board. Adds

a number based on the pattern inside the window to board score.

Слайд 5

Board Evaluation (Cont.)

If the board is represented with a bit-board, the

BEF is just bit-manipulation, and can be done in hardware in parallel

Other mask functions can be used to determine relevant squares (squares which extend or block a pattern) and trim away irrelevant positions

Слайд 6

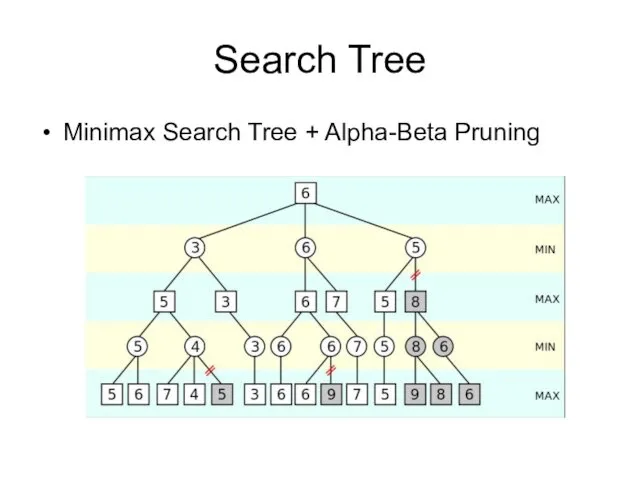

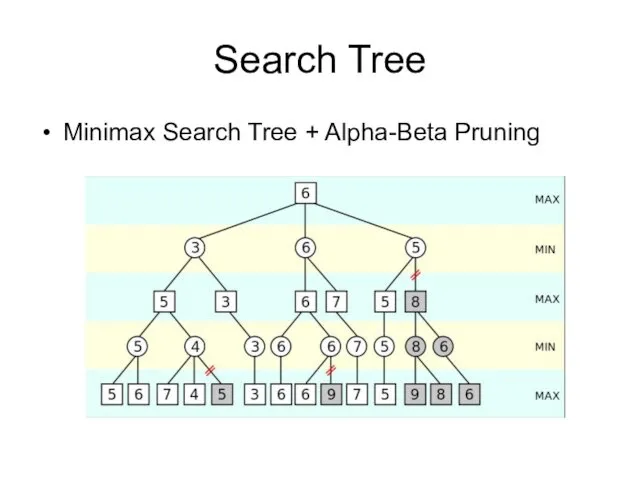

Search Tree

Minimax Search Tree + Alpha-Beta Pruning

Слайд 7

Search Tree (Cont.)

To avoid dynamic memory allocation, we will specify how

many moves per level and the maximum height of the tree

The traversal algorithm will also be sequential and not recursive

Possible to parallelize the traversal in hardware

Слайд 8

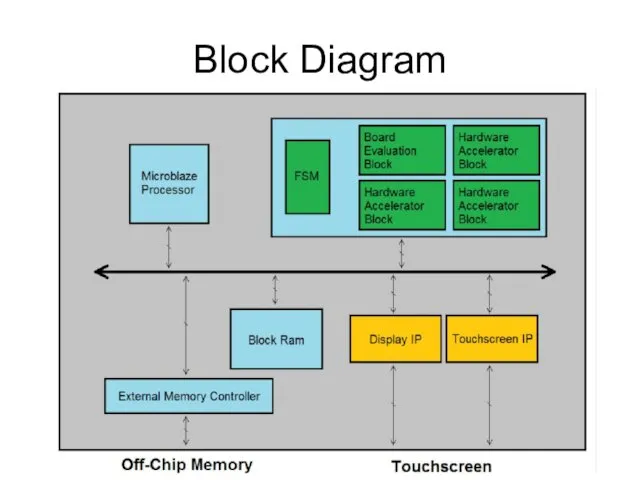

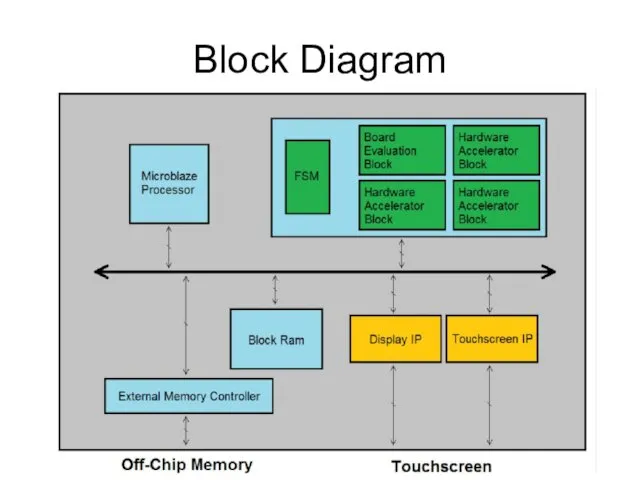

Hardware Acceleration

Instead of checking the squares in a mask sequentially, a

hardware module can do all the checks in one cycle

CPU writes data to predefined locations, the block reads the data, performs the calculations, and write back result

FSM used to track program state and alert CPU when hardware modules are done

Слайд 9

Классный час к празднику 23 февраля Путешествие в разные страны за днём мужчин

Классный час к празднику 23 февраля Путешествие в разные страны за днём мужчин Органическая химия.Белки.Жиры.Углеводы.

Органическая химия.Белки.Жиры.Углеводы. Комплексно-тематическое планирование Книжкина неделя

Комплексно-тематическое планирование Книжкина неделя Оформление древнерусских книг

Оформление древнерусских книг Видільна система. 8 клас

Видільна система. 8 клас Основы обороны государства. Лекция 5

Основы обороны государства. Лекция 5 Презентация Стихи Агнии Барто

Презентация Стихи Агнии Барто Ленин Владимир Ильич - человек, “перевернувший Россию”

Ленин Владимир Ильич - человек, “перевернувший Россию” Выдающаяся личность Джаред Падалеки

Выдающаяся личность Джаред Падалеки презентация Лекарственные растения

презентация Лекарственные растения Половое воспитание

Половое воспитание Энергосбережение в строительстве. Япония

Энергосбережение в строительстве. Япония Расчет одиночных трубчатых колодцев (скважин)

Расчет одиночных трубчатых колодцев (скважин) Тұздар химиялық қосылыстар класы

Тұздар химиялық қосылыстар класы Смертная казнь. Отношение общества к данной мере наказания

Смертная казнь. Отношение общества к данной мере наказания Игра Подари картинки Боре

Игра Подари картинки Боре Программа ИГРАЛОЧКА. Игра как средство развития логического мышления

Программа ИГРАЛОЧКА. Игра как средство развития логического мышления Лес - наше богатство. Викторина

Лес - наше богатство. Викторина Геморрагический васкулит у детей

Геморрагический васкулит у детей Экосистемы. Понятие экосистемы

Экосистемы. Понятие экосистемы Виброакустический метод диагностирования технического состояния колесно-моторного блока

Виброакустический метод диагностирования технического состояния колесно-моторного блока Социальная политика ТРАНСАЭРО

Социальная политика ТРАНСАЭРО Зороастризм

Зороастризм Проект Театр своими руками

Проект Театр своими руками Алгоритмы решения задач по химии (I часть)

Алгоритмы решения задач по химии (I часть) Всероссийская акция Привет солдату

Всероссийская акция Привет солдату Триггеры и их классификация

Триггеры и их классификация Портфолио профессиональной деятельности воспитателя Николенко Татьяны Николаевны

Портфолио профессиональной деятельности воспитателя Николенко Татьяны Николаевны