Содержание

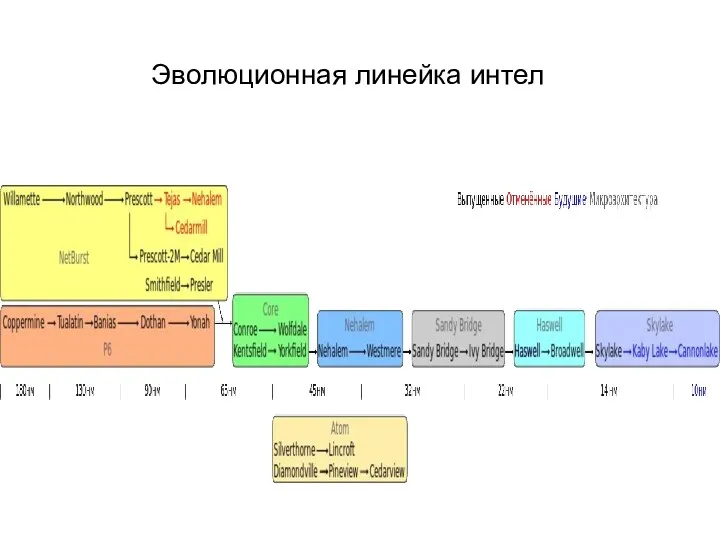

- 2. Эволюционная линейка интел

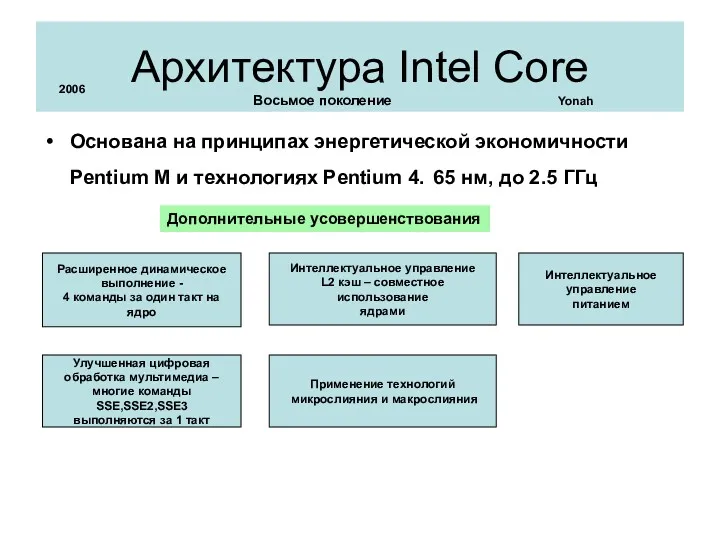

- 3. Архитектура Intel Core Основана на принципах энергетической экономичности Pentium M и технологиях Pentium 4. 65 нм,

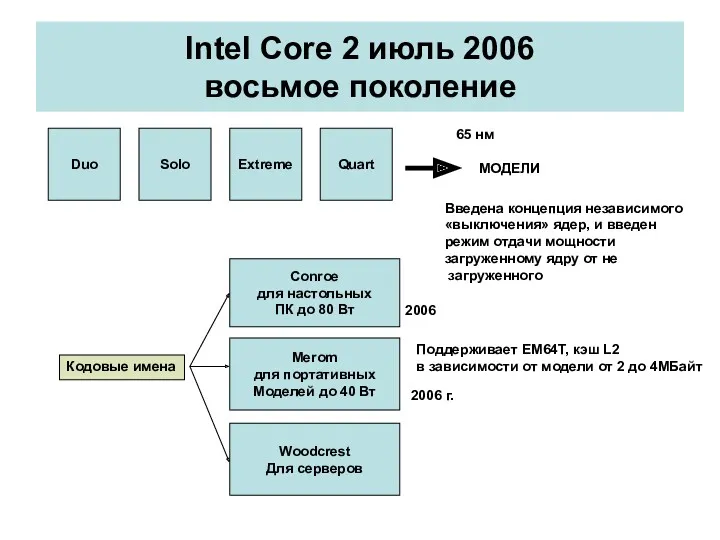

- 4. Intel Core 2 июль 2006 восьмое поколение Duo Solo Extreme Quart Кодовые имена Conroe для настольных

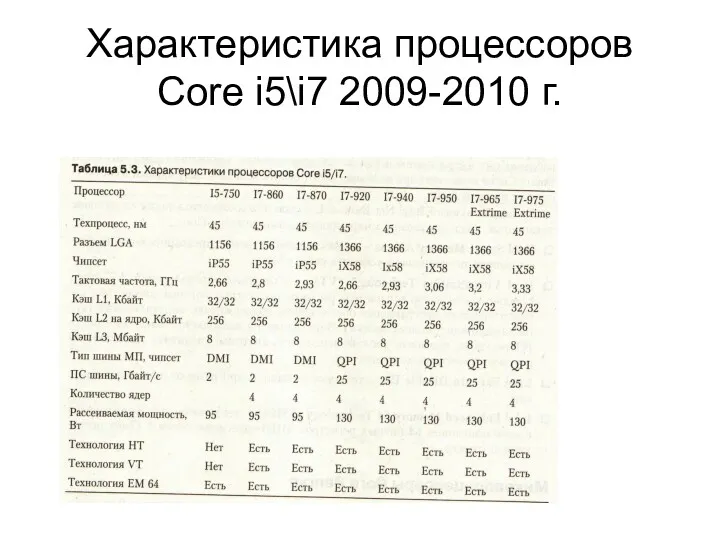

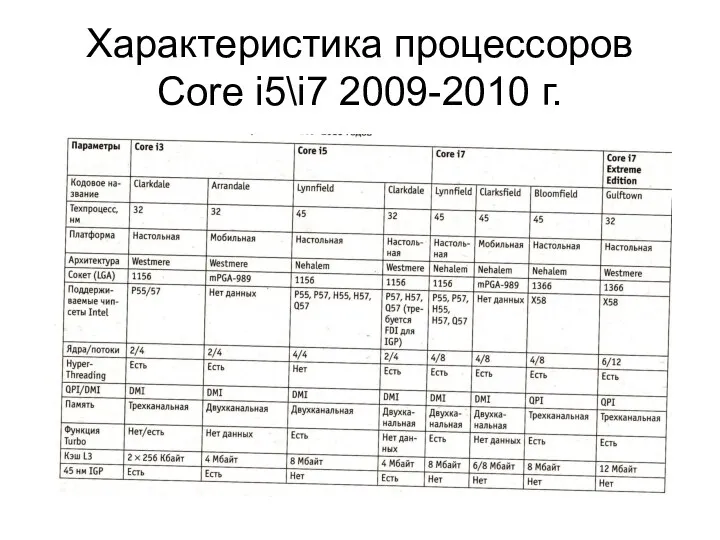

- 5. Характеристика процессоров Core i5\i7 2009-2010 г.

- 6. Характеристика процессоров Core i5\i7 2009-2010 г.

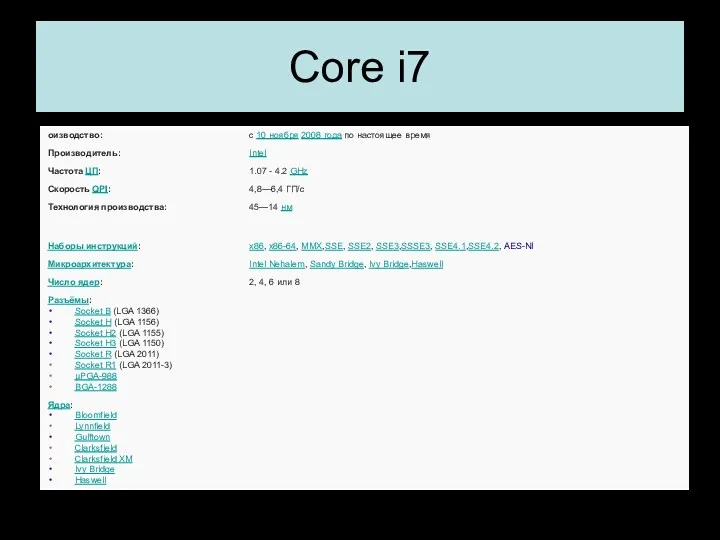

- 7. Core i7

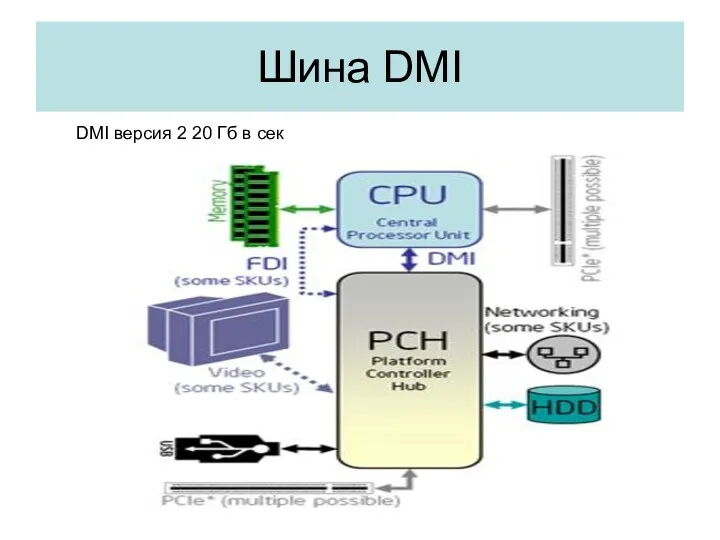

- 8. Шина DMI DMI версия 2 20 Гб в сек

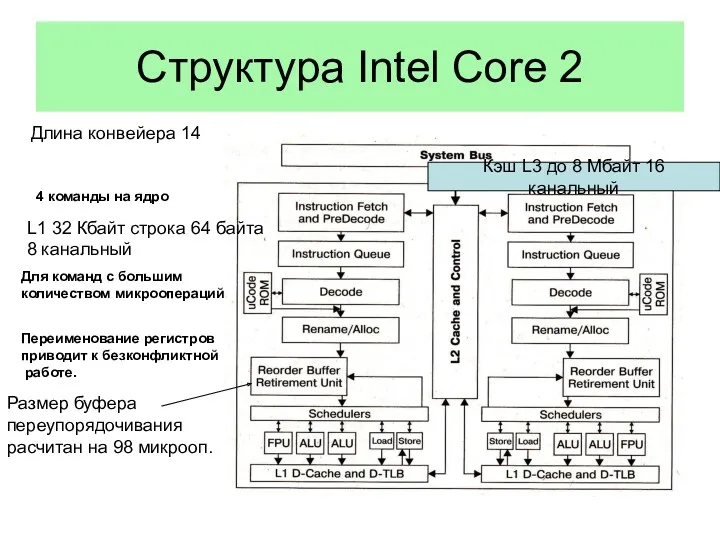

- 9. Структура Intel Core 2 Переименование регистров приводит к безконфликтной работе. Для команд с большим количеством микроопераций

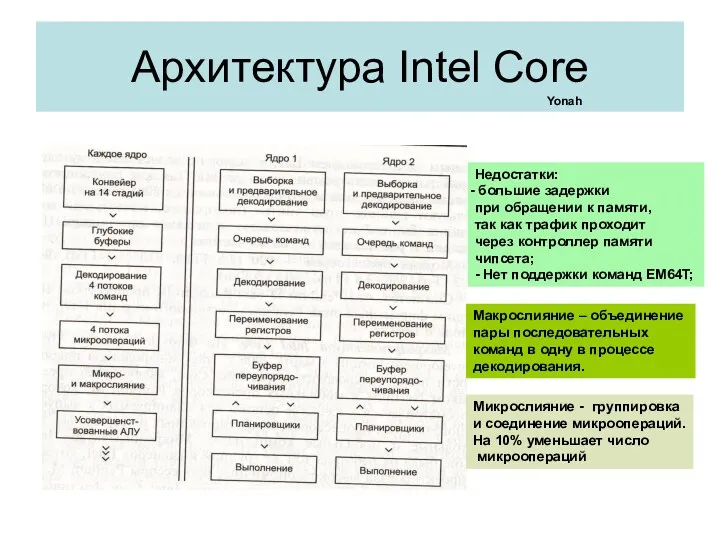

- 10. Архитектура Intel Core Yonah Недостатки: большие задержки при обращении к памяти, так как трафик проходит через

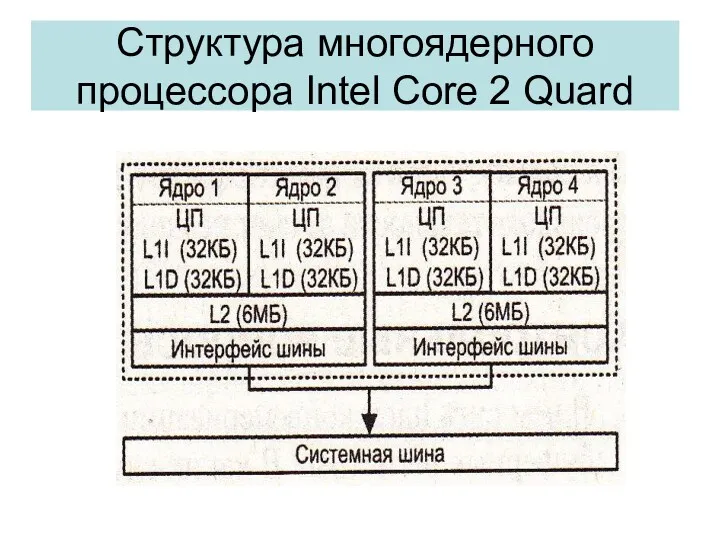

- 11. Структура многоядерного процессора Intel Core 2 Quard

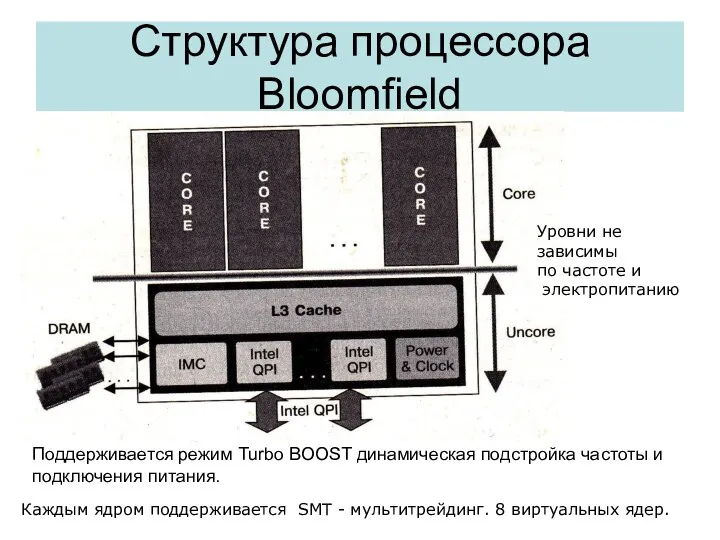

- 12. Структура процессора Bloomfield Уровни не зависимы по частоте и электропитанию Каждым ядром поддерживается SMT - мультитрейдинг.

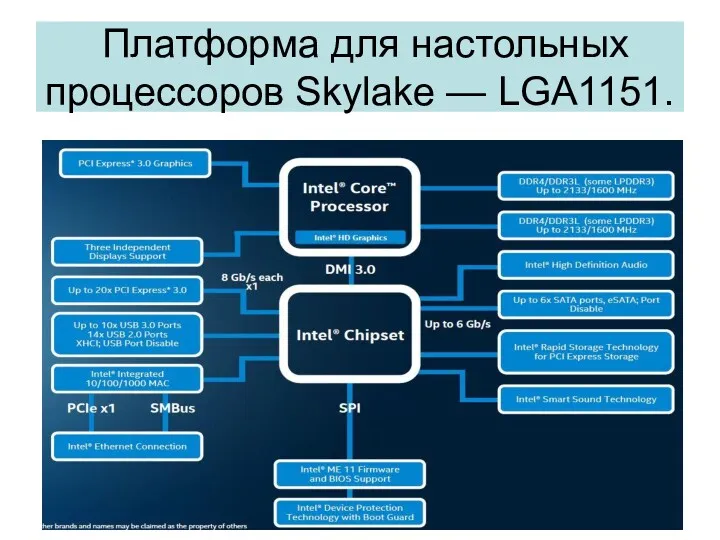

- 13. Платформа для настольных процессоров Skylake — LGA1151.

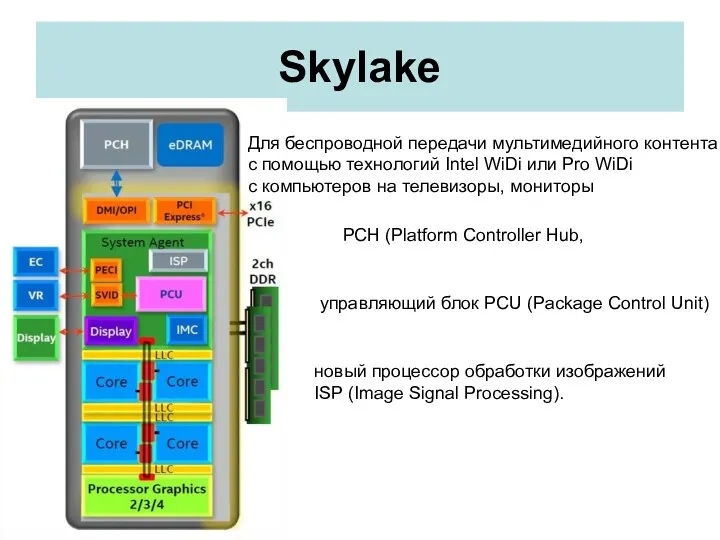

- 14. Skylake Для беспроводной передачи мультимедийного контента с помощью технологий Intel WiDi или Pro WiDi с компьютеров

- 15. Использование кольцевой шины в архитектуре НЕХАЛЕМ

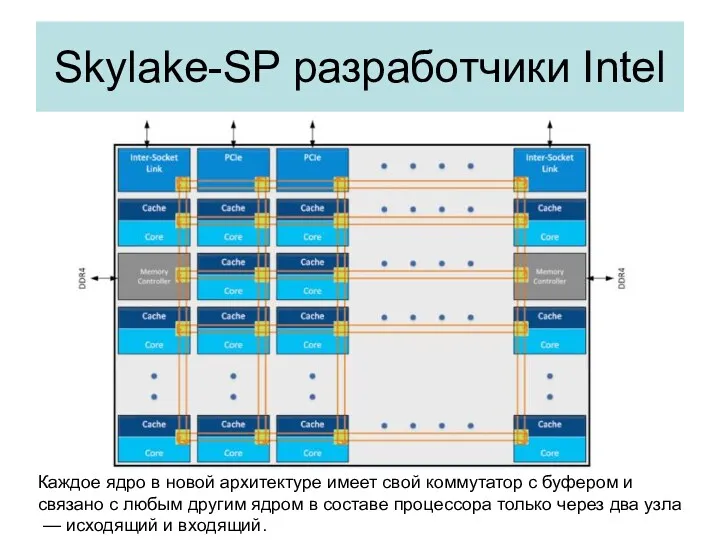

- 16. Skylake-SP разработчики Intel Каждое ядро в новой архитектуре имеет свой коммутатор с буфером и связано с

- 17. Структура многоядерного процессора Intel Nehalem

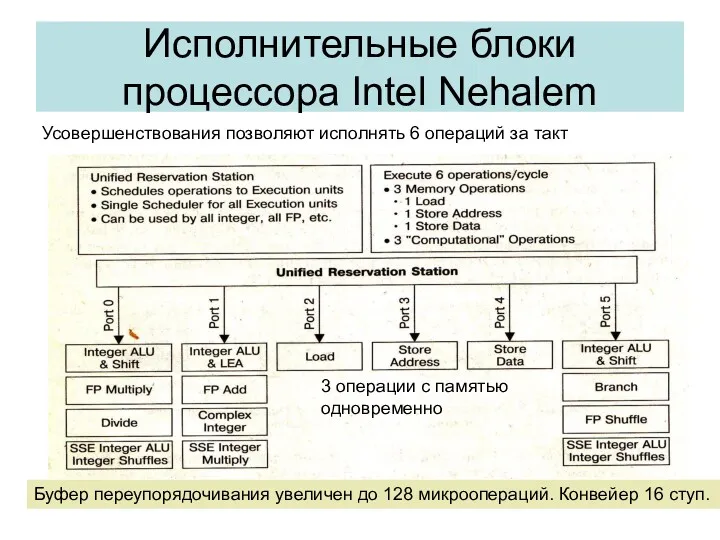

- 18. Исполнительные блоки процессора Intel Nehalem Усовершенствования позволяют исполнять 6 операций за такт 3 операции с памятью

- 19. Ключевые технологии Core и Nehalem Intel Wide Dynamic Execution – исполнение до 5 микроопераций за такт.

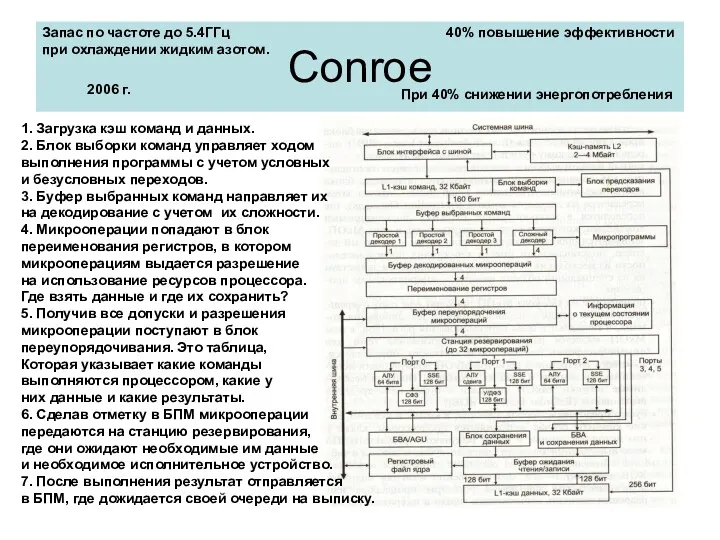

- 20. Conroe 1. Загрузка кэш команд и данных. 2. Блок выборки команд управляет ходом выполнения программы с

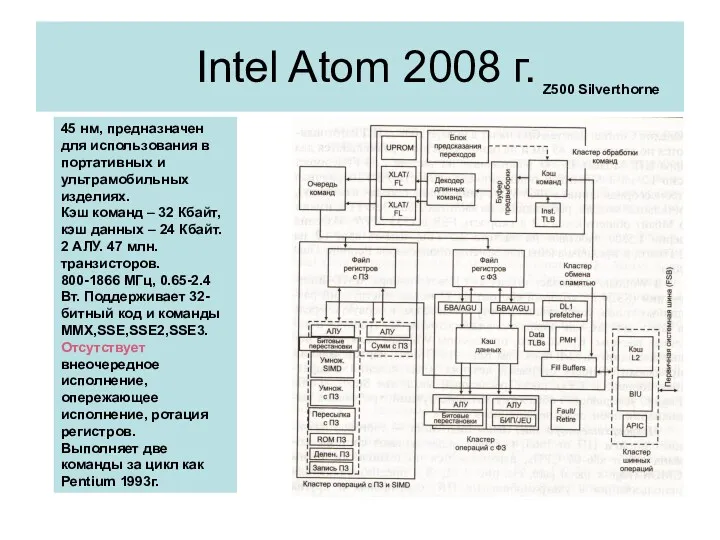

- 21. Intel Atom 2008 г. 45 нм, предназначен для использования в портативных и ультрамобильных изделиях. Кэш команд

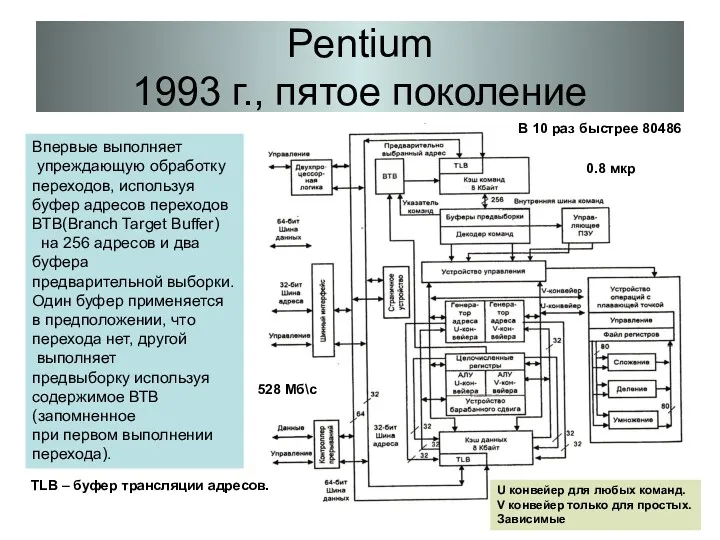

- 22. Pentium 1993 г., пятое поколение Впервые выполняет упреждающую обработку переходов, используя буфер адресов переходов ВТВ(Branch Target

- 23. Процессоры от AMD Положительные стороны: - начиная с 2008 года, большинство процессоров AMD могут выжимать прирост

- 24. Потребляемая мощность Сравнение интел и амд по потребляемой мощности

- 26. Процессоры AMD

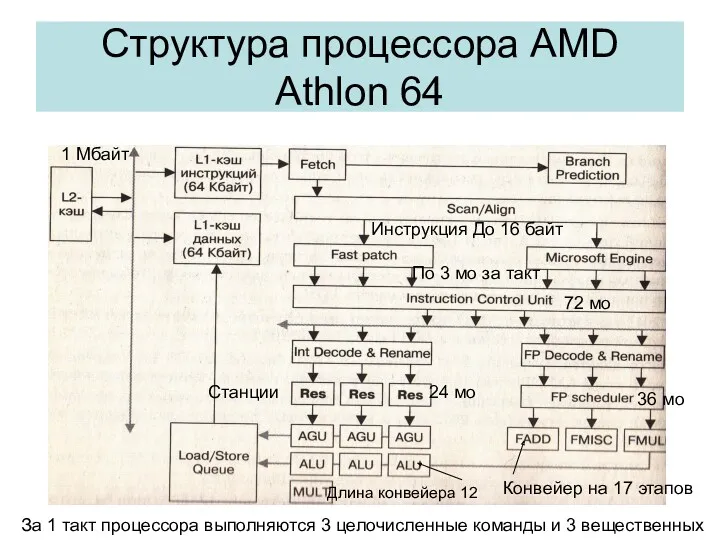

- 27. Структура процессора AMD Athlon 64 1 Мбайт Инструкция До 16 байт По 3 мо за такт

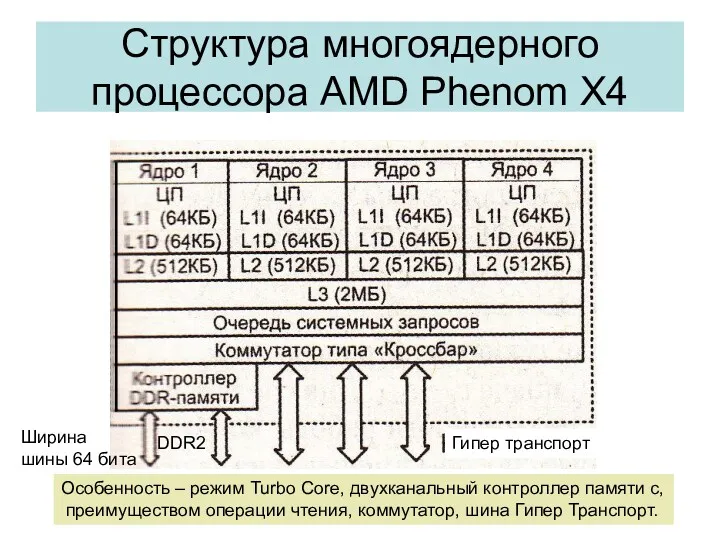

- 28. Структура многоядерного процессора AMD Phenom X4 DDR2 Ширина шины 64 бита Гипер транспорт Особенность – режим

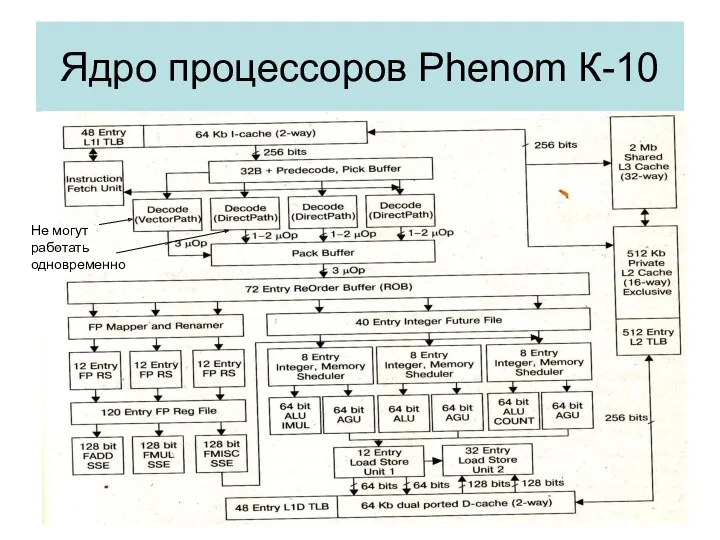

- 29. Ядро процессоров Phenom К-10 Не могут работать одновременно

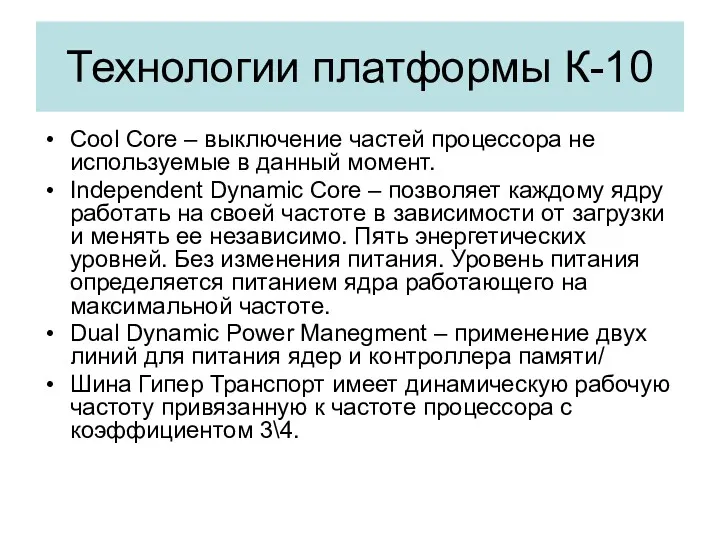

- 30. Технологии платформы К-10 Cool Core – выключение частей процессора не используемые в данный момент. Independent Dynamic

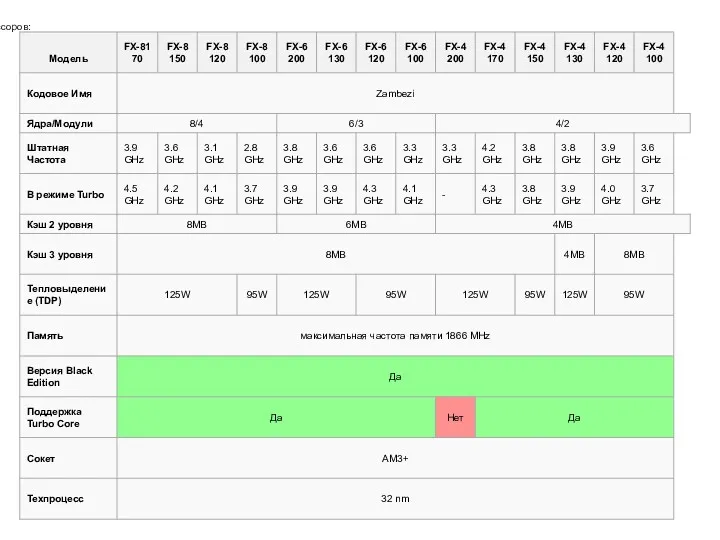

- 31. Таблица процессоров:

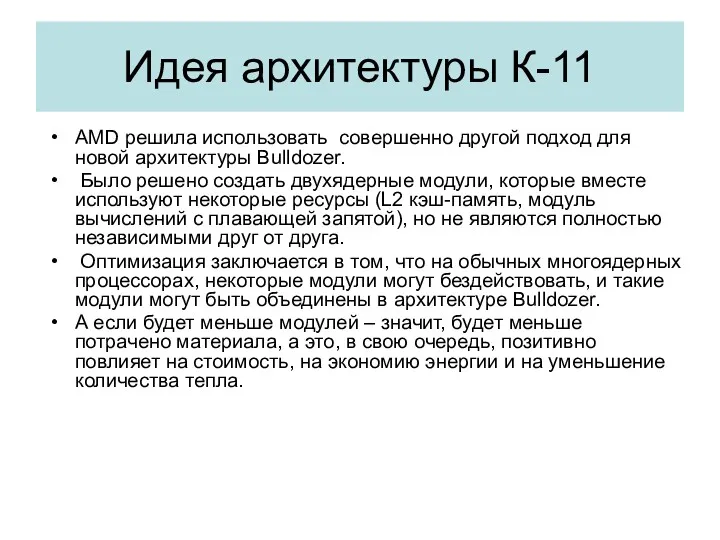

- 32. Идея архитектуры К-11 AMD решила использовать совершенно другой подход для новой архитектуры Bulldozer. Было решено создать

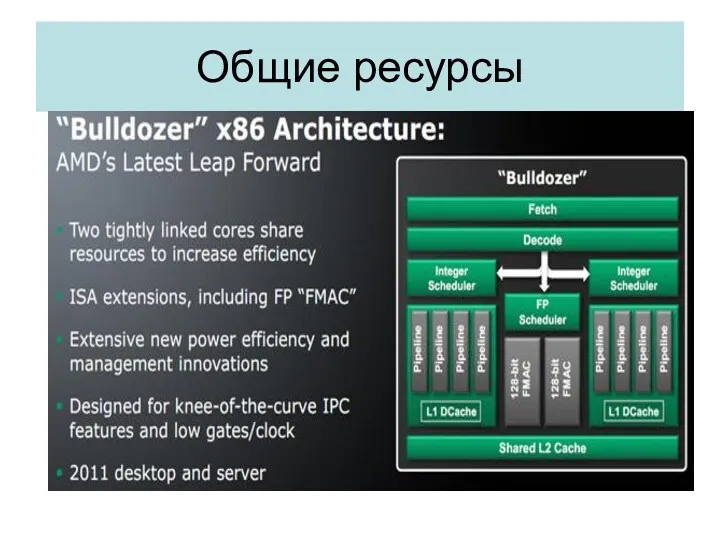

- 33. Общие ресурсы

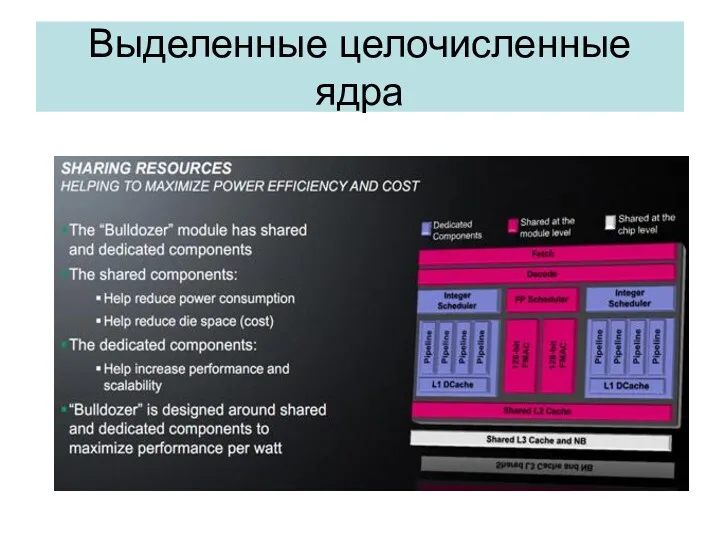

- 34. Выделенные целочисленные ядра

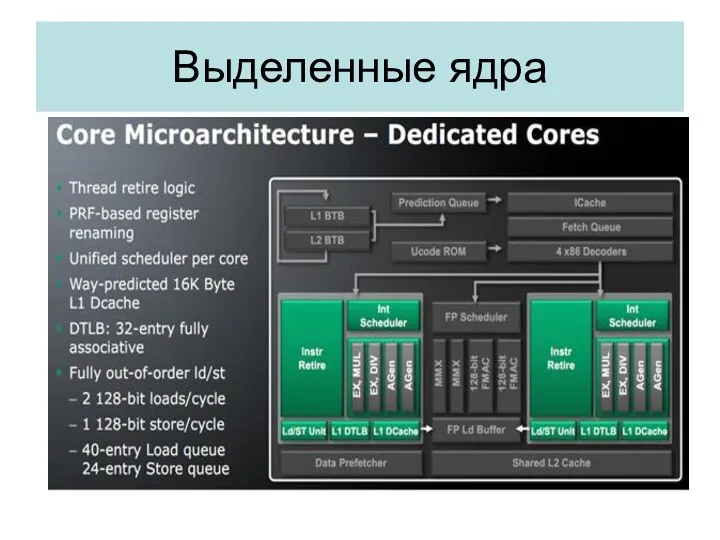

- 35. Выделенные ядра

- 36. Общие ресурсы в совместном использовании потоков оказывается та часть процессора, которая осуществляет предварительную обработку данных. Предсказатель

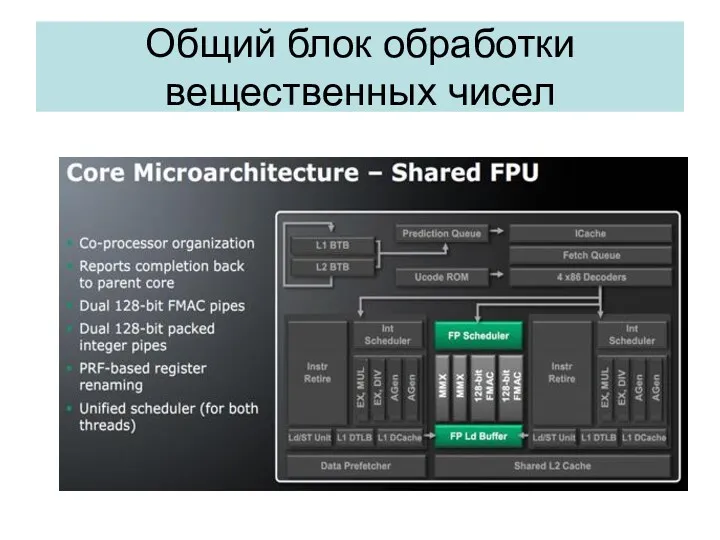

- 37. Общий блок обработки вещественных чисел

- 38. Общий кэш второго уровня

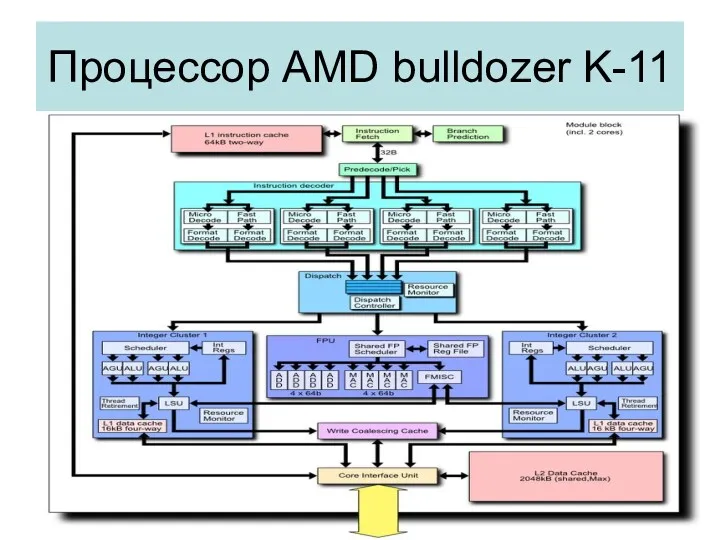

- 39. Процессор AMD bulldozer K-11

- 40. 8 ядерный бульдозер

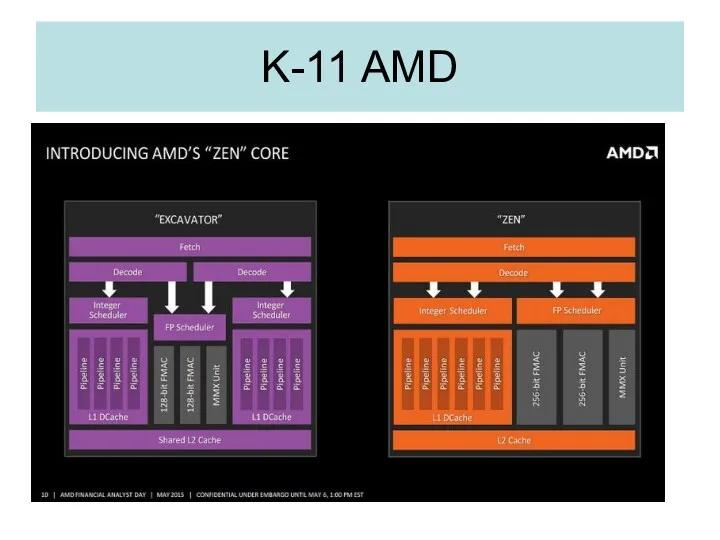

- 41. K-11 AMD

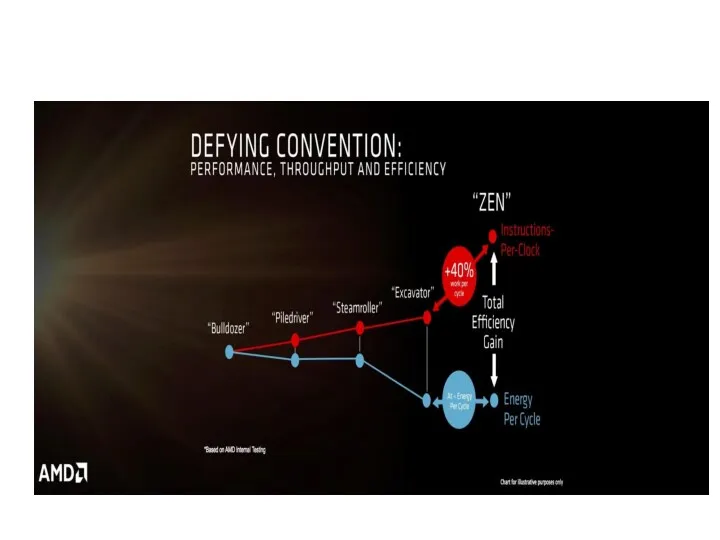

- 42. Особенности ZEN два потока на ядро; кэш декодированных микроопераций; 16 МБ общей кэш-памяти третьего уровня (2

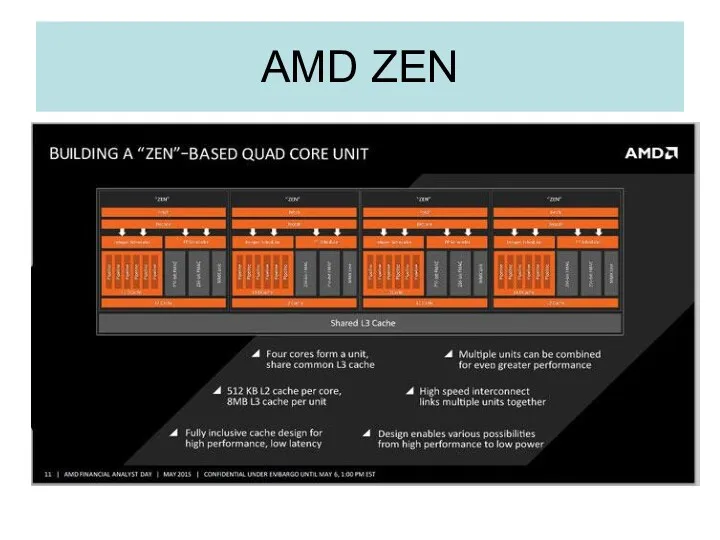

- 43. AMD ZEN

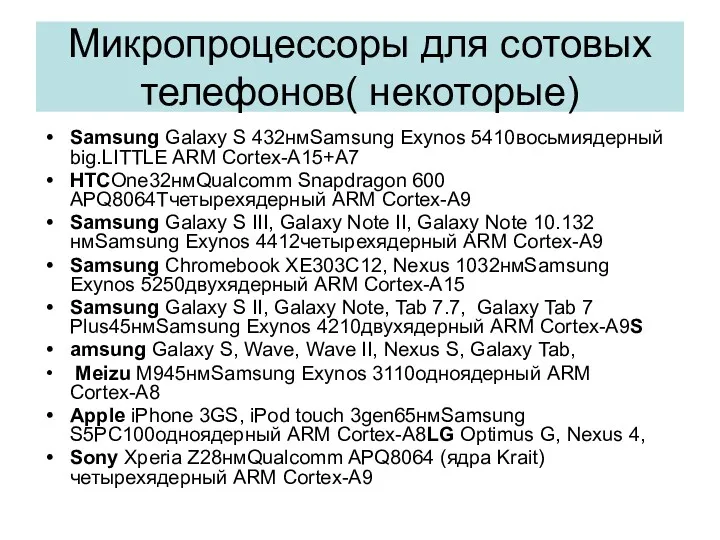

- 44. Микропроцессоры для сотовых телефонов( некоторые) Samsung Galaxy S 432нмSamsung Exynos 5410восьмиядерный big.LITTLE ARM Cortex-A15+A7 HTCOne32нмQualcomm Snapdragon

- 45. Структурная схема GSM телефона

- 46. Приемо-передатчик GSM

- 47. Топ-10 6-ядерный Qualcomm Snapdragon 808 В его архитектуре используется концепция совмещения нескольких разных по частоте ядер

- 48. Топ-10 6-ядерный Qualcomm Snapdragon 650 Структура состоит из четырех ядер Cortex A53 с частотой каждого по

- 49. Топ-10 2-ядерный Apple A8 Чип оснащен двумя ядрами на однокристальной системе с фирменной архитектурой Cyclone. Обе

- 50. Топ-10 8-ядерный Qualcomm Snapdragon Это улучшенная 8-ядерная версия Snapdragon 650, которая получила четыре ядра Cortex-A53 со

- 51. Топ-10 8-ядерный Samsung Exynos 7420 используется 8-ядерна архитектура маленьких-больших ядре big.LITTLE, где четыре производительных Cortex-A57 (2,1

- 52. Топ-10 8-ядерный Huawei Kirin 950 используется система из 8 ядер, где идет тоже распределение на четыре

- 54. Скачать презентацию

Мастер-класс Новогодняя игрушка Лошадка

Мастер-класс Новогодняя игрушка Лошадка Поколения. Взаимоотношение поколений

Поколения. Взаимоотношение поколений Красота природы в картинах русских художников и стихах русских поэтов

Красота природы в картинах русских художников и стихах русских поэтов Банковская система

Банковская система Виготовлення новорічної прикраси

Виготовлення новорічної прикраси Шошқа етін өндірутехнологиясы

Шошқа етін өндірутехнологиясы Нуклеиновые кислоты

Нуклеиновые кислоты Лев Давидович Ландау

Лев Давидович Ландау отк.кл.час.- А.А. БАЛЬЦЕР

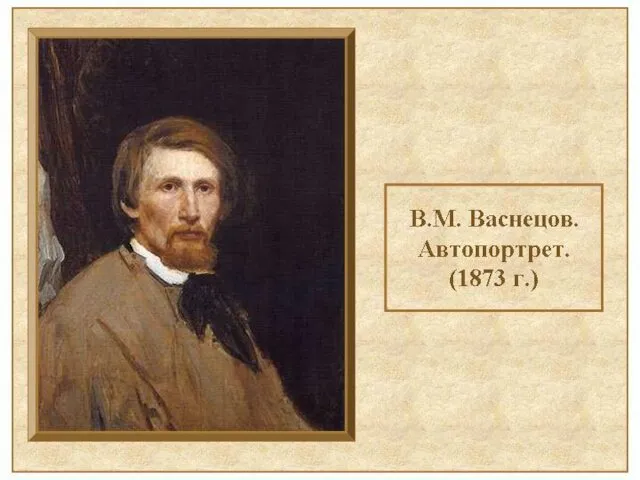

отк.кл.час.- А.А. БАЛЬЦЕР Сочинение-описание. Васнецов. Богатыри

Сочинение-описание. Васнецов. Богатыри Цирроз печени

Цирроз печени Энергетическое хозяйство предприятия

Энергетическое хозяйство предприятия Современное состояние животноводства (перспективы его развития, продовольственная безопасность)

Современное состояние животноводства (перспективы его развития, продовольственная безопасность) Несправності процесорів та їх усунення

Несправності процесорів та їх усунення Уральский добровольческий танковый корпус. Народный подвиг Урала в годы Великой Отечественной войны

Уральский добровольческий танковый корпус. Народный подвиг Урала в годы Великой Отечественной войны Казахское ханство в XV-XVIII веках

Казахское ханство в XV-XVIII веках Текстильная промышленность

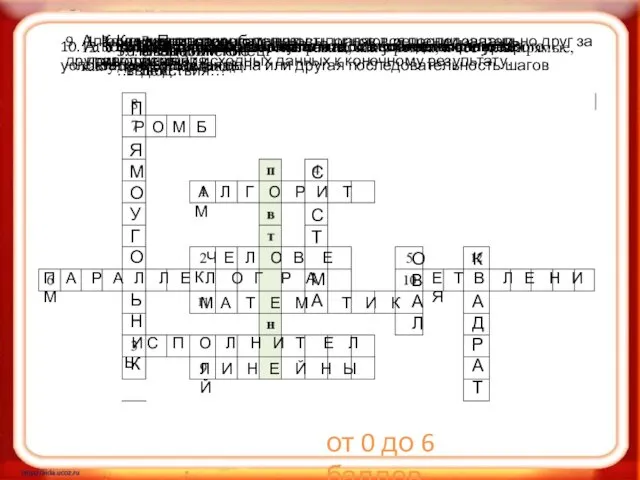

Текстильная промышленность Алгоритм с повторением

Алгоритм с повторением Решение задач экономического содержания

Решение задач экономического содержания Перпендикуляр и наклонная. Угол между прямой и плоскостью

Перпендикуляр и наклонная. Угол между прямой и плоскостью Питательные среды. Методы культивирования микробов и аппаратура. Учет результатов анализа воздуха

Питательные среды. Методы культивирования микробов и аппаратура. Учет результатов анализа воздуха Технология получения кисломолочных продуктов

Технология получения кисломолочных продуктов Презентация Города миллионеры России

Презентация Города миллионеры России Политическая культура

Политическая культура Презентация проекта Логопедические технологии формирования связной речи дошкольников с ОНР с использованием методов мнемотехники

Презентация проекта Логопедические технологии формирования связной речи дошкольников с ОНР с использованием методов мнемотехники Светский, рациональный характер культуры: литература и искусство

Светский, рациональный характер культуры: литература и искусство Теоретические основы конструирования швейных изделий

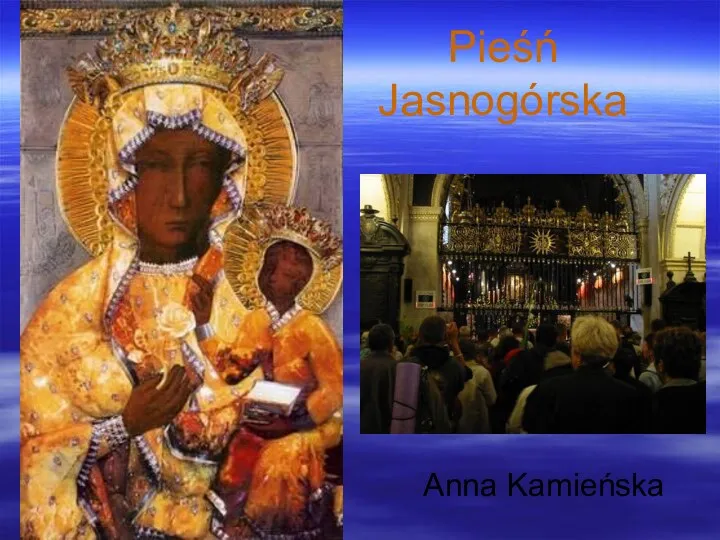

Теоретические основы конструирования швейных изделий Pieśń Jasnogórska

Pieśń Jasnogórska