Содержание

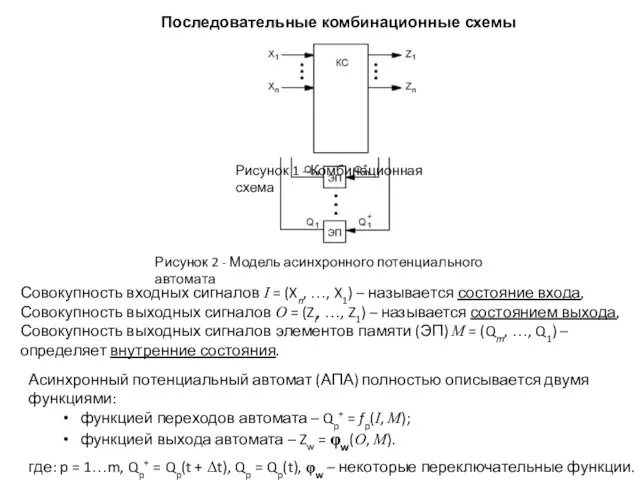

- 2. Рисунок 2 - Модель асинхронного потенциального автомата Последовательные комбинационные схемы Совокупность входных сигналов I = (Xn,

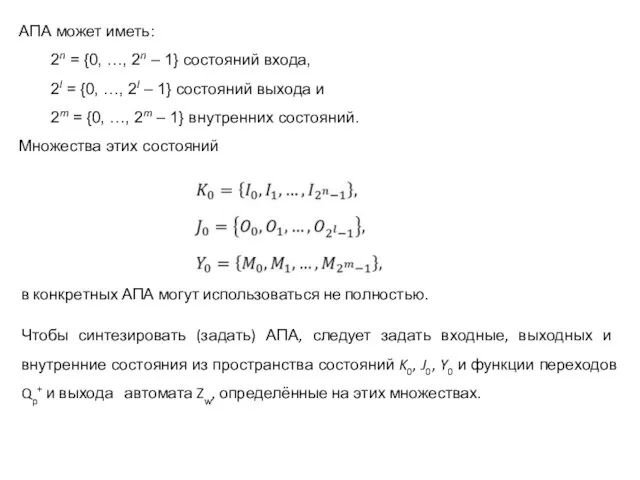

- 3. АПА может иметь: 2n = {0, …, 2n – 1} состояний входа, 2l = {0, …,

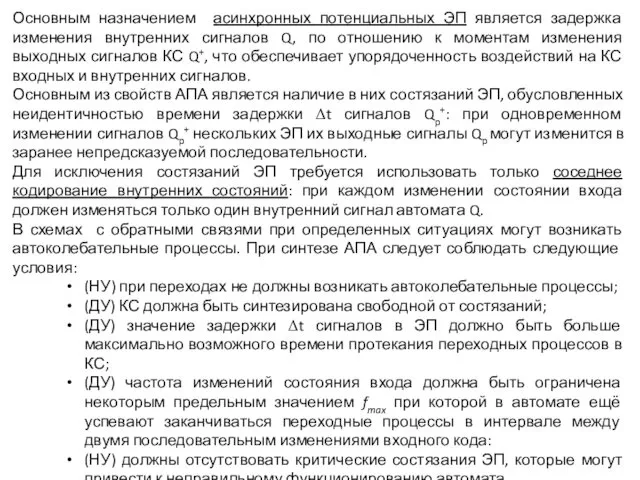

- 4. Основным назначением асинхронных потенциальных ЭП является задержка изменения внутренних сигналов Q, по отношению к моментам изменения

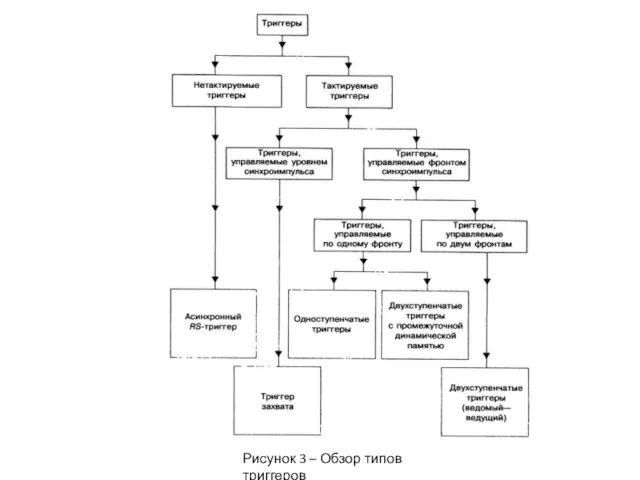

- 5. Рисунок 3 – Обзор типов триггеров

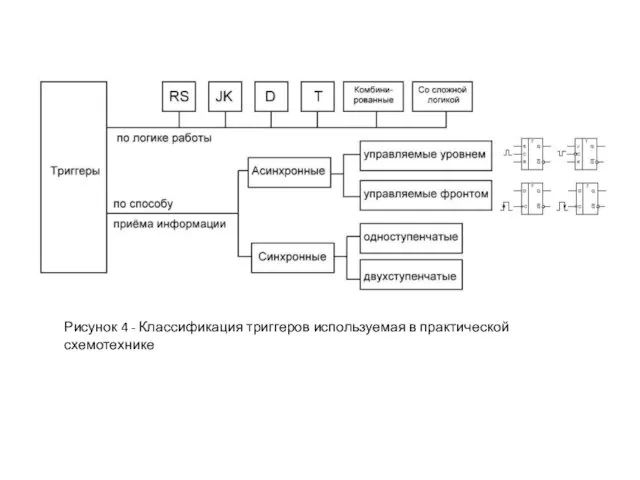

- 6. Рисунок 4 - Классификация триггеров используемая в практической схемотехнике

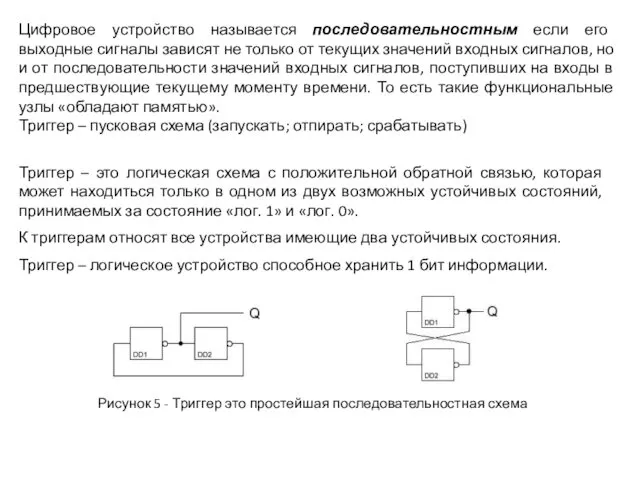

- 7. Цифровое устройство называется последовательностным если его выходные сигналы зависят не только от текущих значений входных сигналов,

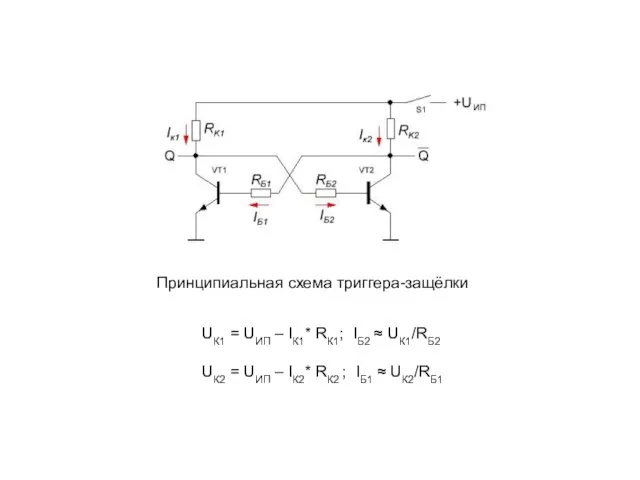

- 8. Принципиальная схема триггера-защёлки UК1 = UИП – IК1* RК1; IБ2 ≈ UК1/RБ2 UК2 = UИП –

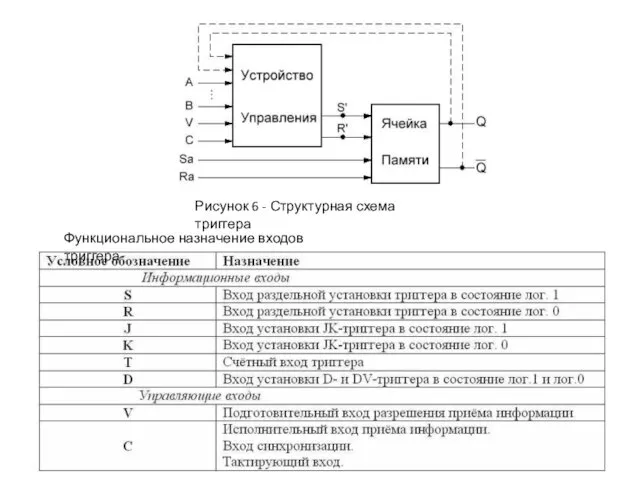

- 9. Рисунок 6 - Структурная схема триггера Функциональное назначение входов триггера

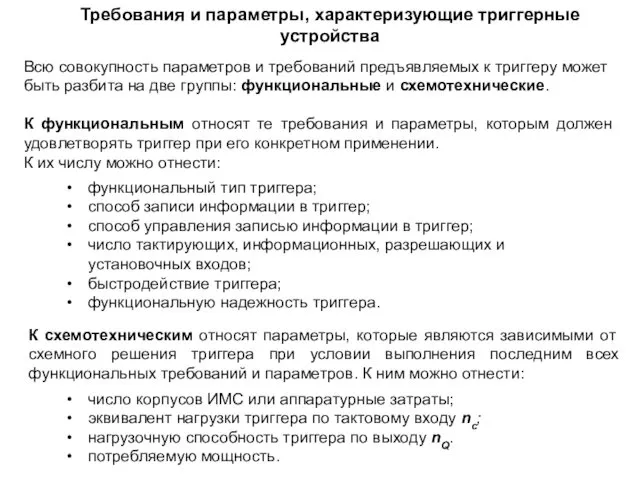

- 10. Требования и параметры, характеризующие триггерные устройства Всю совокупность параметров и требований предъявляемых к триггеру может быть

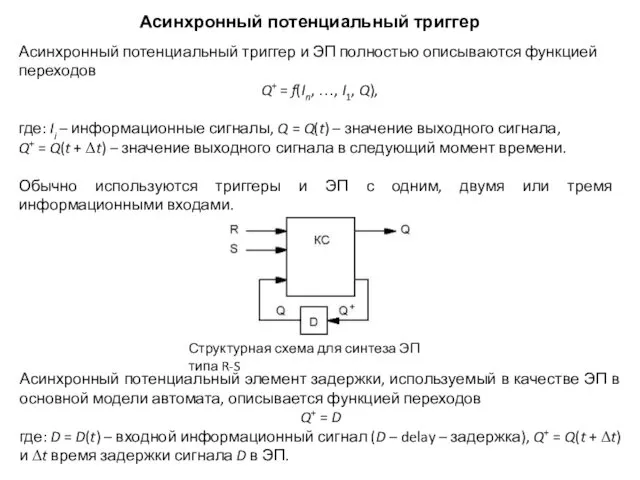

- 11. Асинхронный потенциальный триггер Асинхронный потенциальный триггер и ЭП полностью описываются функцией переходов Q+ = f(In, …,

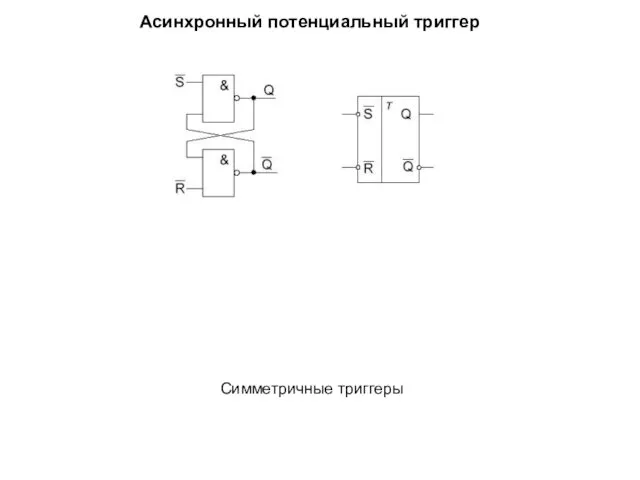

- 12. Асинхронный потенциальный триггер Симметричные триггеры

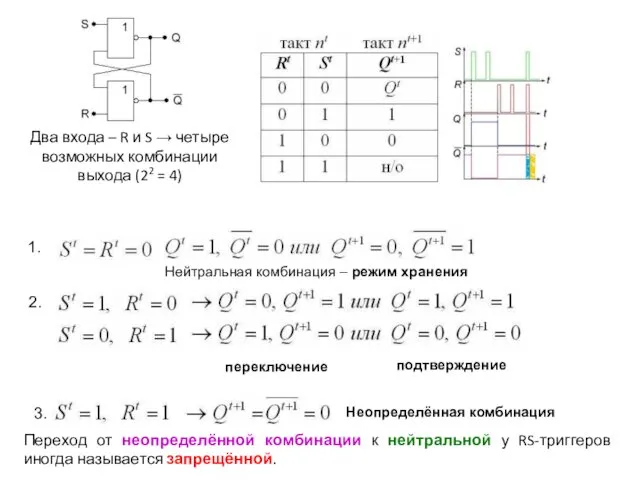

- 13. Два входа – R и S → четыре возможных комбинации выхода (22 = 4) 1. Нейтральная

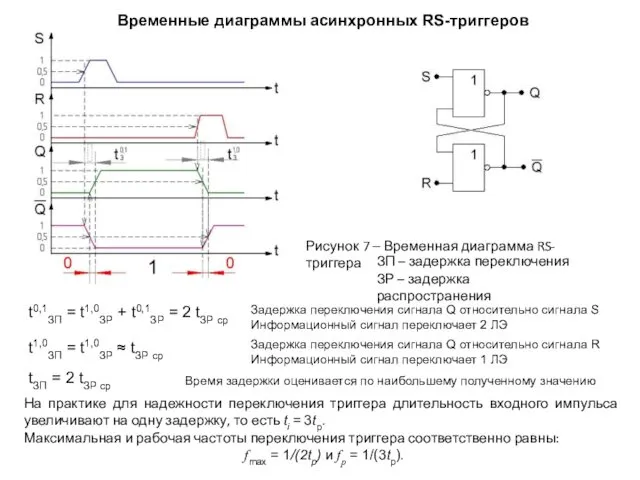

- 14. Временные диаграммы асинхронных RS-триггеров t0,1ЗП = t1,0ЗР + t0,1ЗР = 2 tЗР ср t1,0ЗП = t1,0ЗР

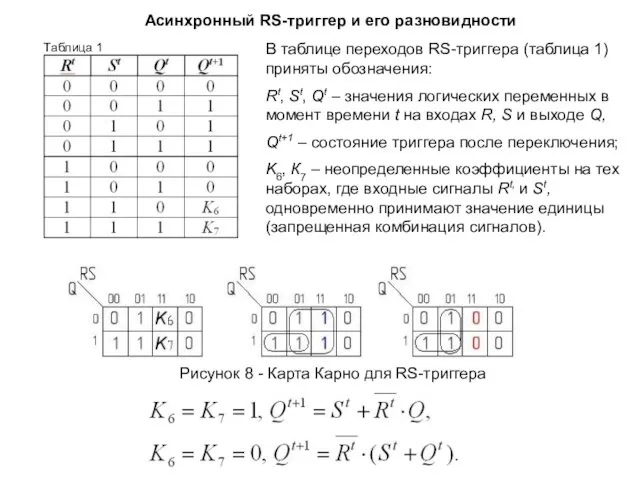

- 15. В таблице переходов RS-триггера (таблица 1) приняты обозначения: Rt, St, Qt – значения логических переменных в

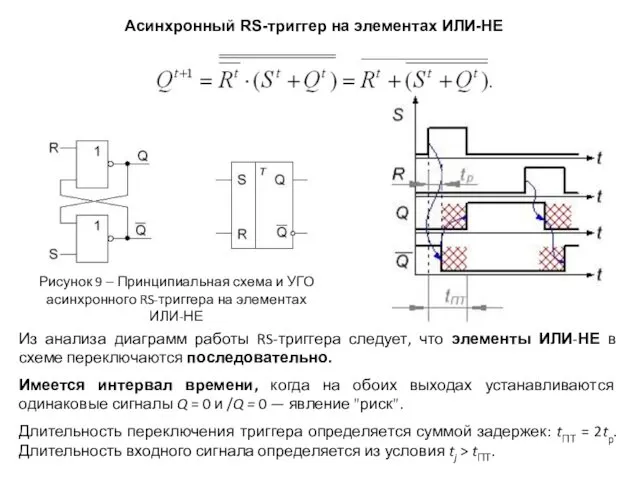

- 16. Асинхронный RS-триггер на элементах ИЛИ-НЕ Из анализа диаграмм работы RS-триггера следует, что элементы ИЛИ-НЕ в схеме

- 17. Асинхронный RS-триггер на элементах И-НЕ Из анализа диаграмм работы RS-триггера следует, что элементы И-НЕ в схеме

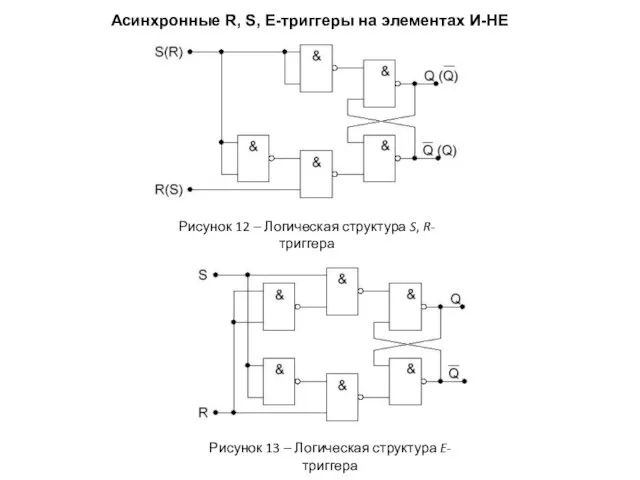

- 18. Разновидности RS-триггеров S-триггер – при одновременной подаче двух активных сигналов на управляющих входах на выходе Q

- 19. Рисунок 12 ‒ Логическая структура S, R-триггера Рисунок 13 ‒ Логическая структура E-триггера Асинхронныe R, S,

- 20. Т-триггер Асинхронный Т-триггер имеет один вход Т и два выхода – основной и инверсный. Входной импульс

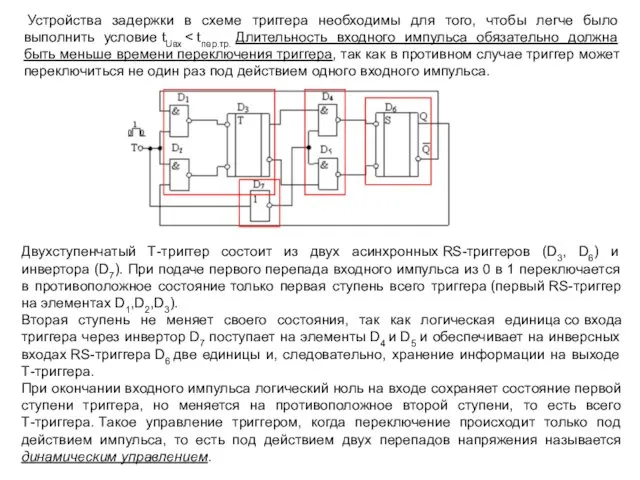

- 21. Устройства задержки в схеме триггера необходимы для того, чтобы легче было выполнить условие tUвх Двухступенчатый Т-триггер

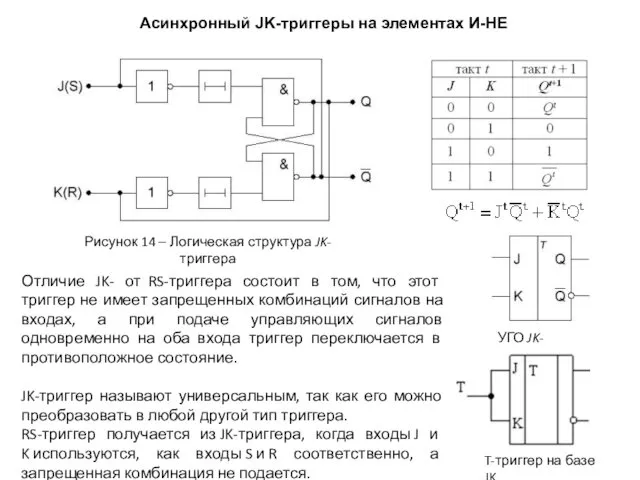

- 22. Рисунок 14 ‒ Логическая структура JK-триггера Асинхронный JK-триггеры на элементах И-НЕ УГО JK-триггера Отличие JK- от

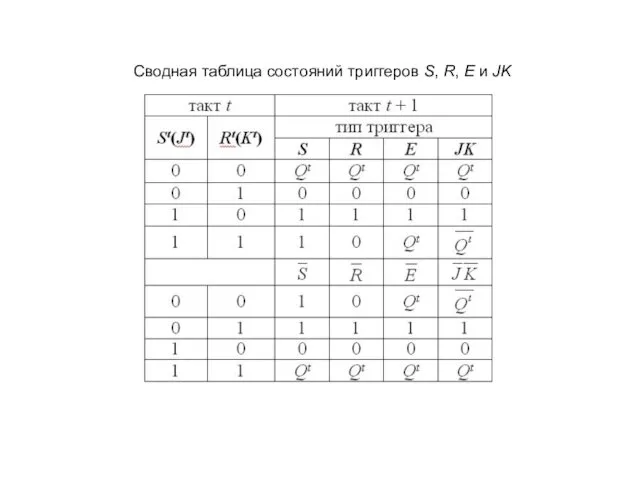

- 23. Сводная таблица состояний триггеров S, R, E и JK

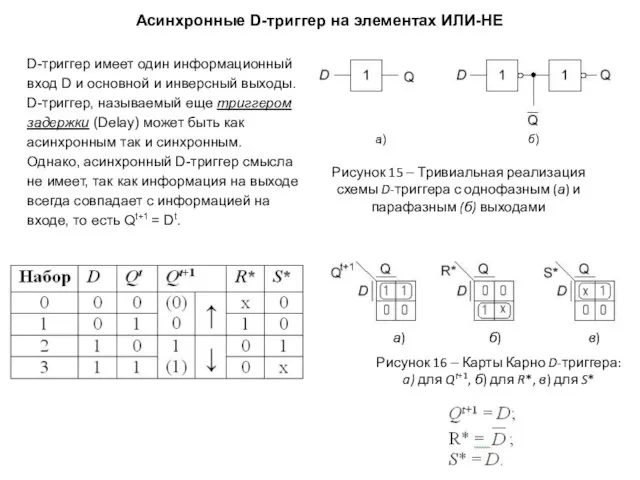

- 24. Рисунок 15 ‒ Тривиальная реализация схемы D-триггера с однофазным (а) и парафазным (б) выходами а) б)

- 26. Скачать презентацию

РУССКИЙ ДЕЕПРИЧАСТИЕ

РУССКИЙ ДЕЕПРИЧАСТИЕ Food idioms

Food idioms Bino va inshootlar zilzilabardoshligi

Bino va inshootlar zilzilabardoshligi Учимся создавать электронное портфолио

Учимся создавать электронное портфолио Гальванические покрытия

Гальванические покрытия Сети связи с подвижными объектами

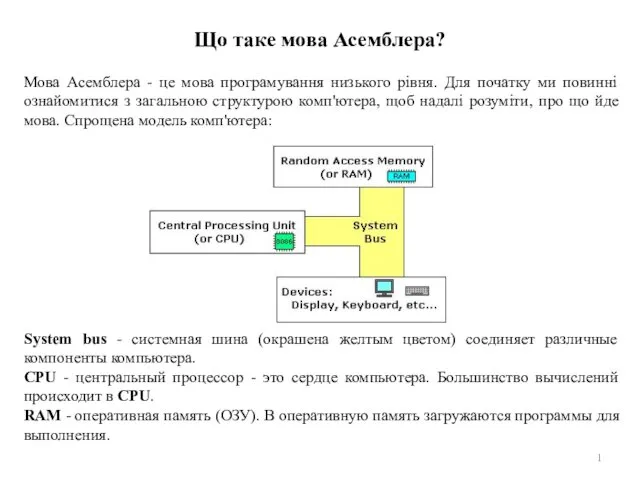

Сети связи с подвижными объектами Цифрові технології. Мова Асемблера. (Тема 6-7)

Цифрові технології. Мова Асемблера. (Тема 6-7) Проектная деятельность в начальной школе

Проектная деятельность в начальной школе Транзисторы. (Лекция 6)

Транзисторы. (Лекция 6) Комплексные методы управления качеством

Комплексные методы управления качеством Итальянский костюм Возрождения

Итальянский костюм Возрождения Контрольная уборка и выпуск шасси

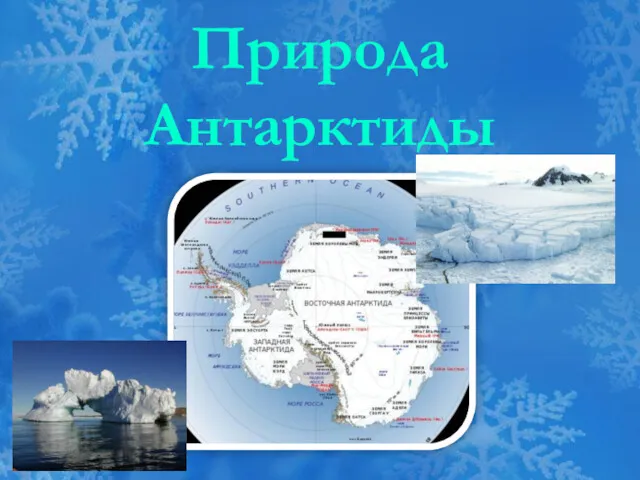

Контрольная уборка и выпуск шасси Антарктида.2

Антарктида.2 Презентация Серная кислота

Презентация Серная кислота Объекты Range и Selection

Объекты Range и Selection Игры в Европе и как их готовить

Игры в Европе и как их готовить Я то, что я ем

Я то, что я ем Способы очистки газов от пыли

Способы очистки газов от пыли Обобщение опыта воспитательной работы

Обобщение опыта воспитательной работы Организации как субъекты административного права

Организации как субъекты административного права Роль игры в развитие ребенка

Роль игры в развитие ребенка День Святого Валентина

День Святого Валентина Совет молодежи АО ТЯЖМАШ. Отчет о результатах работы за 2018 год

Совет молодежи АО ТЯЖМАШ. Отчет о результатах работы за 2018 год Волшебство из бисера

Волшебство из бисера Лексико-грамматические разряды существительных

Лексико-грамматические разряды существительных Различение звуков П-Т.

Различение звуков П-Т. Атлант-Ю. Бюджетные комплекты техники Tessa

Атлант-Ю. Бюджетные комплекты техники Tessa Природные зоны Республики Татарстан (часть 2)

Природные зоны Республики Татарстан (часть 2)