Содержание

- 2. Единая архитектура всех микроконтроллеров серии Motor Control Блок-схема микроконтроллера Блок схема ядра центрального процессора Многошинная модифицированная

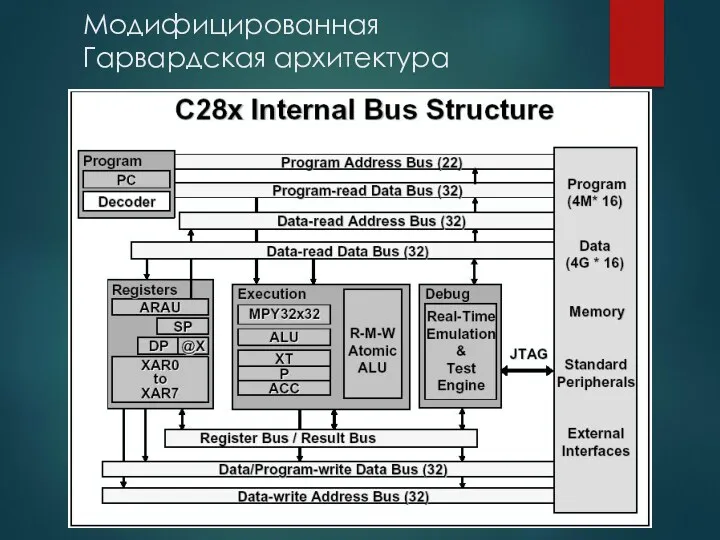

- 3. Модифицированная Гарвардская архитектура

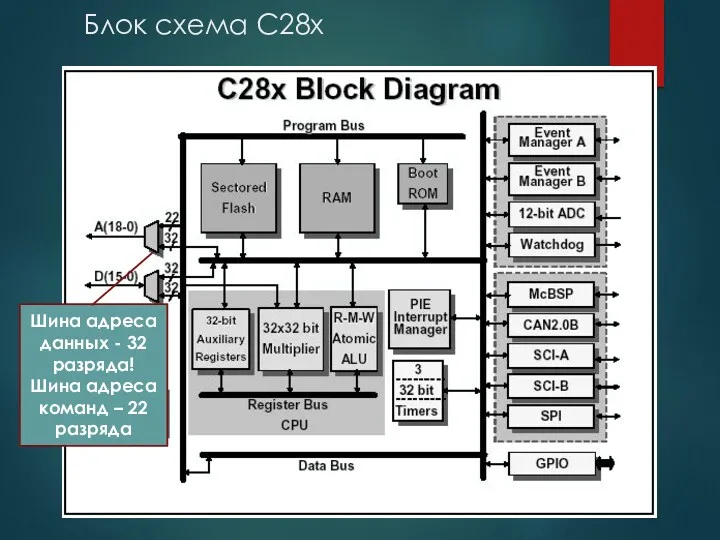

- 4. Блок схема С28х Шина адреса данных - 32 разряда! Шина адреса команд – 22 разряда

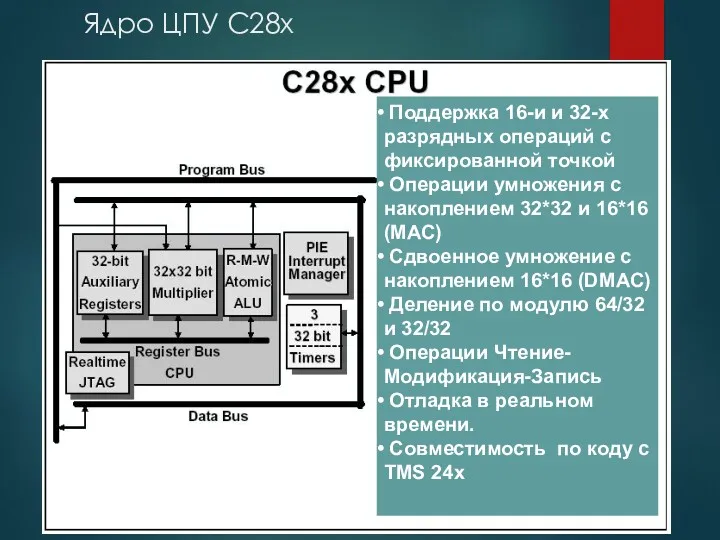

- 5. Ядро ЦПУ С28х Поддержка 16-и и 32-х разрядных операций с фиксированной точкой Операции умножения с накоплением

- 6. Атомарные операции чтения/модификации/записи Преимущества: Упрощение программирования Уменьшение размера программного кода Непрерываемость команды (атомарность) Более эффективное компилирование

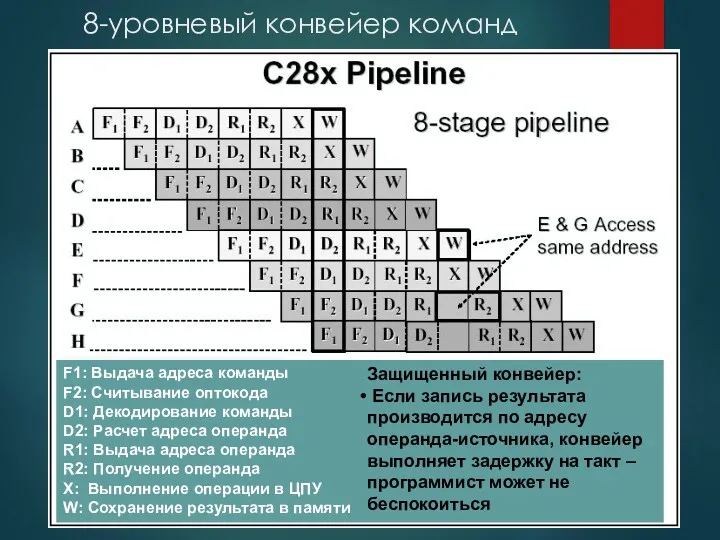

- 7. 8-уровневый конвейер команд F1: Выдача адреса команды F2: Считывание оптокода D1: Декодирование команды D2: Расчет адреса

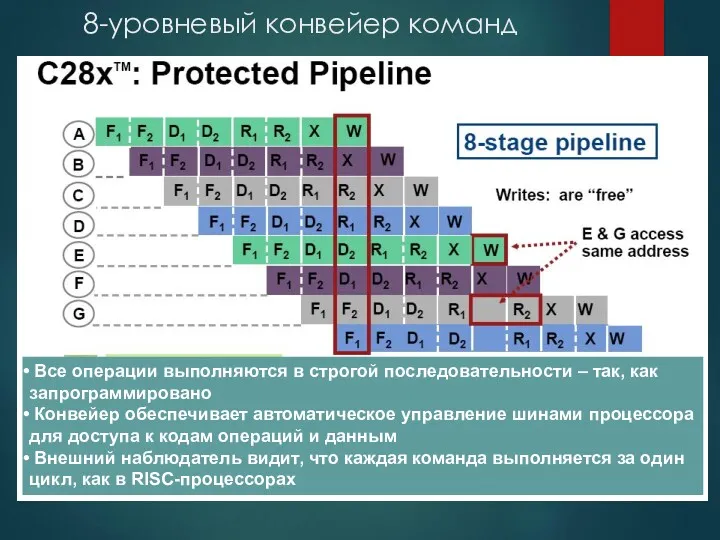

- 8. Все операции выполняются в строгой последовательности – так, как запрограммировано Конвейер обеспечивает автоматическое управление шинами процессора

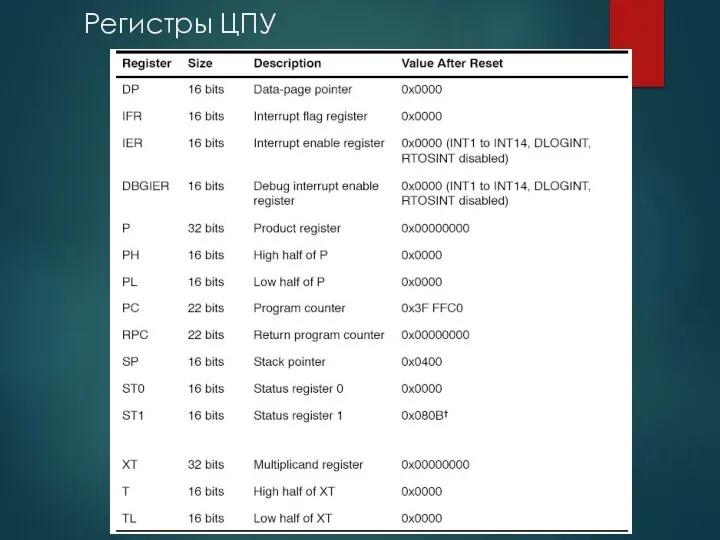

- 9. Регистры ЦПУ

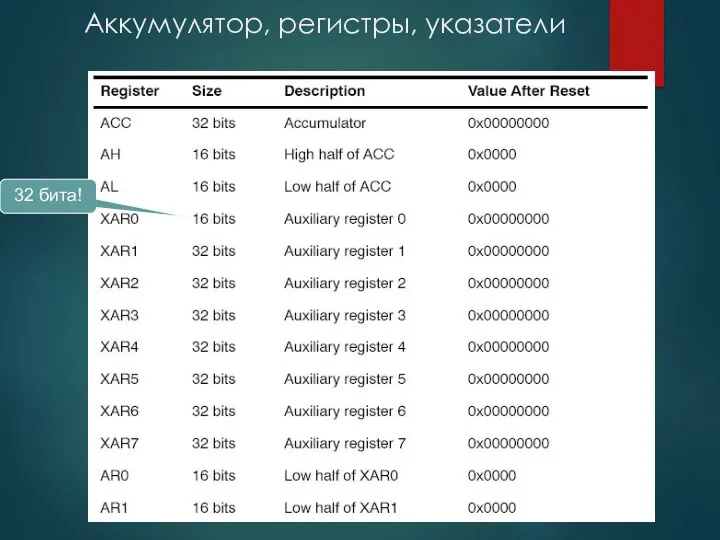

- 10. Аккумулятор, регистры, указатели 32 бита!

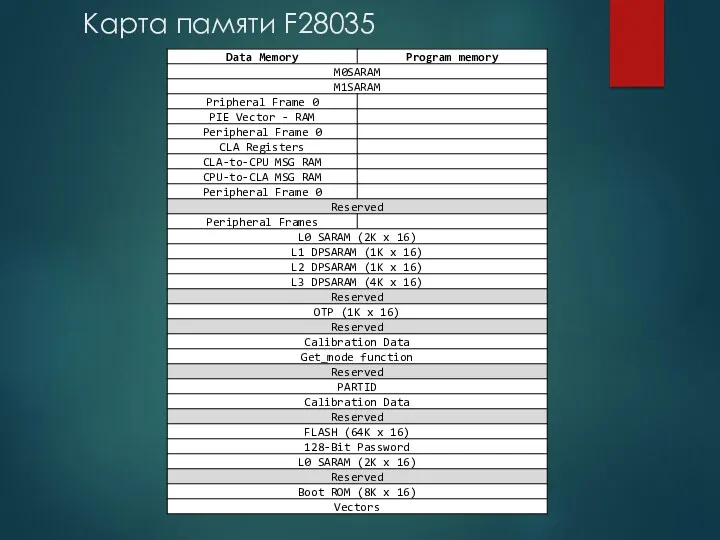

- 11. Карта памяти F28035

- 12. Основные способы адресации 28хх Режим прямой адресации – Direct Addressing Mode Режим стековой адресации – Stack

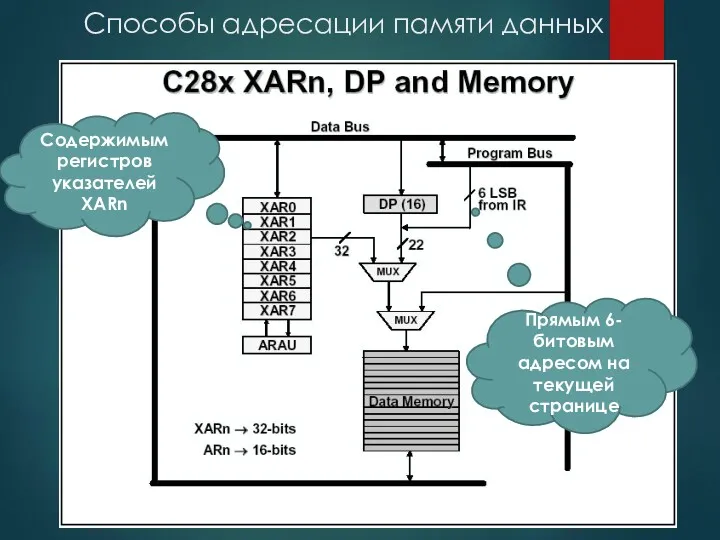

- 13. Способы адресации памяти данных Содержимым регистров указателей XARn Прямым 6-битовым адресом на текущей странице

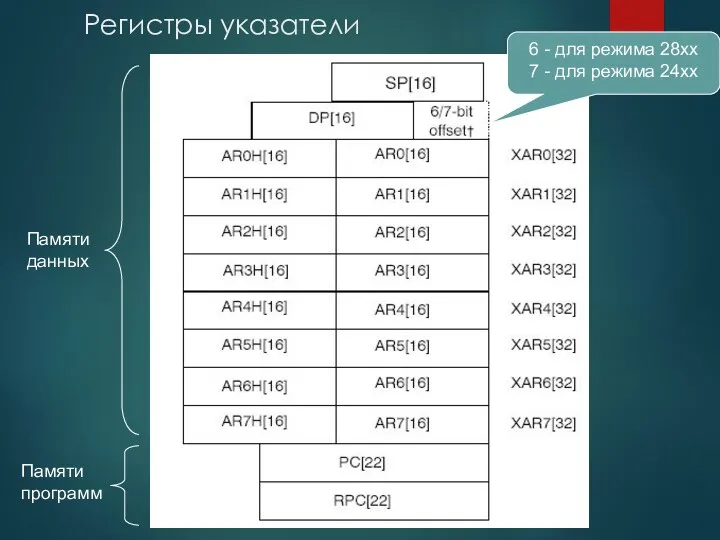

- 14. Регистры указатели Памяти данных Памяти программ 6 - для режима 28хх 7 - для режима 24хх

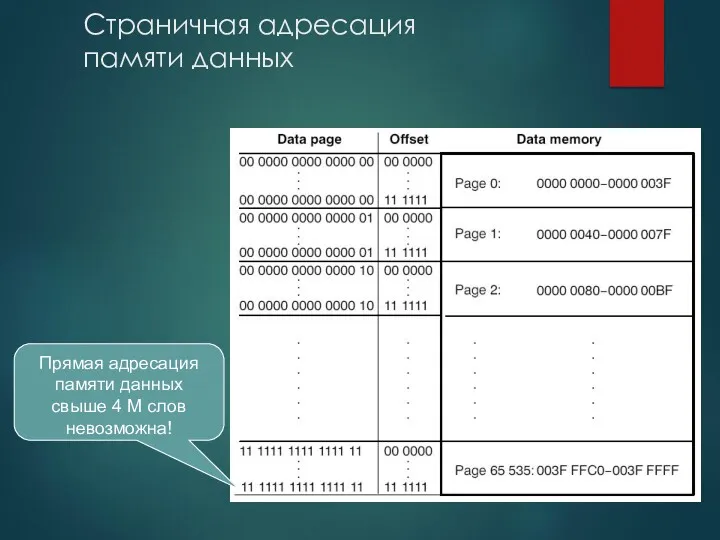

- 15. Страничная адресация памяти данных Прямая адресация памяти данных свыше 4 М слов невозможна!

- 16. Область памяти данных, доступная с помощью стековой адресации

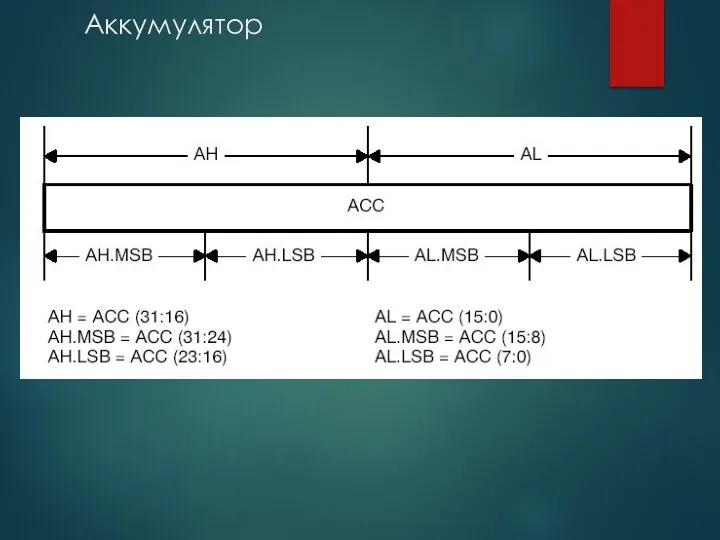

- 17. Аккумулятор

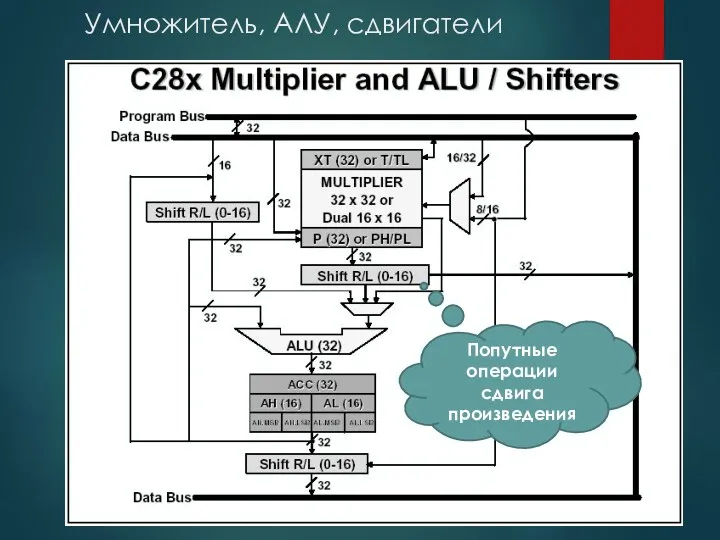

- 18. Умножитель, АЛУ, cдвигатели Попутные операции сдвига произведения

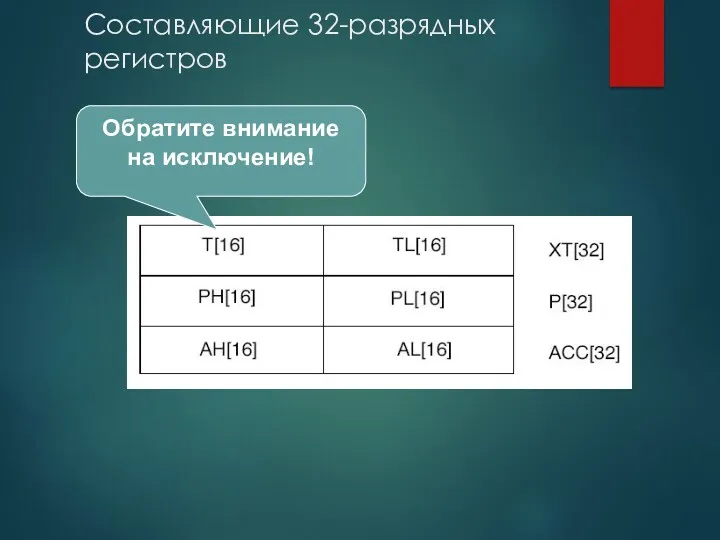

- 19. Составляющие 32-разрядных регистров Обратите внимание на исключение!

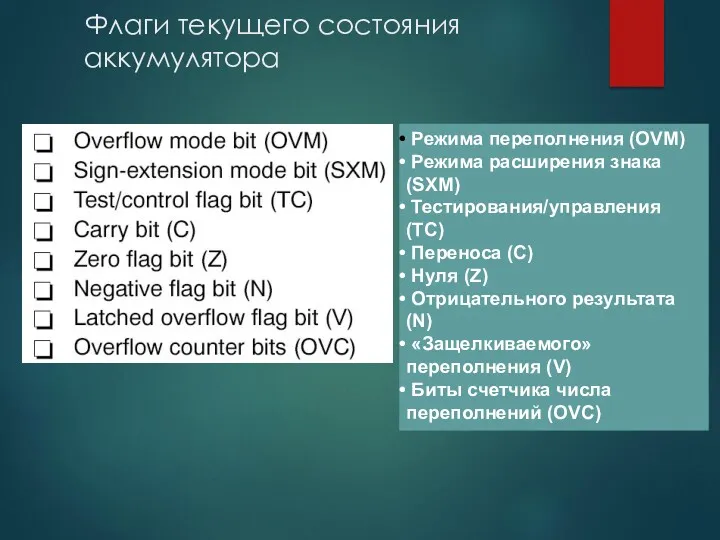

- 20. Флаги текущего состояния аккумулятора Режима переполнения (ОVM) Режима расширения знака (SXM) Тестирования/управления (TC) Переноса (C) Нуля

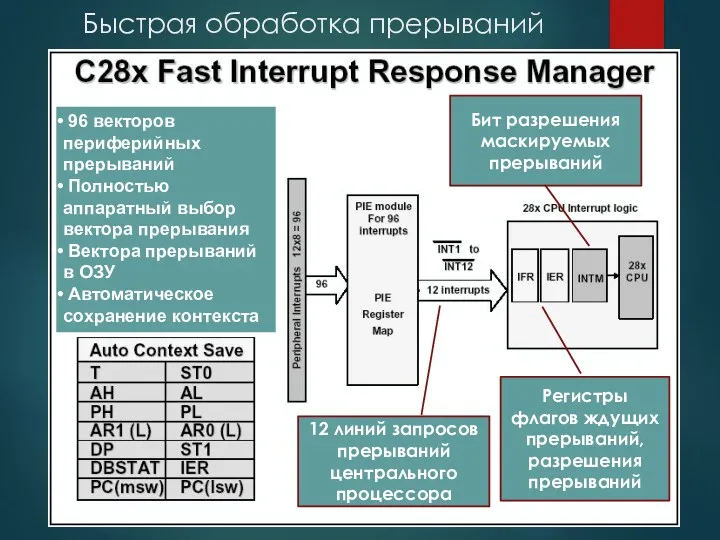

- 21. Быстрая обработка прерываний 96 векторов периферийных прерываний Полностью аппаратный выбор вектора прерывания Вектора прерываний в ОЗУ

- 23. Скачать презентацию

Антиоксидантный комплекс витаминов Новомин. Сибирское здоровье

Антиоксидантный комплекс витаминов Новомин. Сибирское здоровье День летних и осенних именинников

День летних и осенних именинников Полы промышленных зданий

Полы промышленных зданий Жил человек... христианские притчи.

Жил человек... христианские притчи. Проблемы ИТВ. Кратко о плагиатах телеканалов и о плохих каналах

Проблемы ИТВ. Кратко о плагиатах телеканалов и о плохих каналах Оценка уровня обслуживания в магазинах Колеса даром

Оценка уровня обслуживания в магазинах Колеса даром Развитие страхования жизни в ООО Альянс жизнь

Развитие страхования жизни в ООО Альянс жизнь Обзор распространенных причин, препятствующих осуществлению государственного кадастрового учета

Обзор распространенных причин, препятствующих осуществлению государственного кадастрового учета Диагностика метапредметных результатов обучения

Диагностика метапредметных результатов обучения Кофе и кофейные напитки

Кофе и кофейные напитки Гипотиреоз

Гипотиреоз Неорганические (минеральные) воздушные вяжущие вещества

Неорганические (минеральные) воздушные вяжущие вещества Жизнь и творчество Ван Гога

Жизнь и творчество Ван Гога Физические и механические свойства древесины. 6 класс

Физические и механические свойства древесины. 6 класс Теория + пратика = ? Размышления, рассуждения, выводы

Теория + пратика = ? Размышления, рассуждения, выводы Проблемное обучение на уроке математики

Проблемное обучение на уроке математики Проект бурения скважины на Верхне-Ветлянском месторождении с выбором мероприятий по борьбе с поглощениями бурового раствора

Проект бурения скважины на Верхне-Ветлянском месторождении с выбором мероприятий по борьбе с поглощениями бурового раствора Сестринский уход при различных заболеваниях и состояниях

Сестринский уход при различных заболеваниях и состояниях Учебный тренажёр и проверочный тест по теме: Члены предложения

Учебный тренажёр и проверочный тест по теме: Члены предложения Презентация урока-исследования Байкал-уникальное творение природы

Презентация урока-исследования Байкал-уникальное творение природы Презентация1 апреля

Презентация1 апреля Толерантность - путь к культуре мира.

Толерантность - путь к культуре мира. Введение в предмет Алгебра логики

Введение в предмет Алгебра логики Презентация к классному часу в 7 классе по теме Кижи

Презентация к классному часу в 7 классе по теме Кижи Тіс-жақ аймағының аурулары, асқазан ішек жолдарында эррозиялы ойық-жаралы зақымдануға алып келетін факторлар

Тіс-жақ аймағының аурулары, асқазан ішек жолдарында эррозиялы ойық-жаралы зақымдануға алып келетін факторлар Регистрирующее устройство

Регистрирующее устройство Единый всекубанский классный час Год культуры - история Кубани в лицах, 4 класс

Единый всекубанский классный час Год культуры - история Кубани в лицах, 4 класс Отчёт-презентация на тему:Социально-личностное развитие дошкольников

Отчёт-презентация на тему:Социально-личностное развитие дошкольников