Содержание

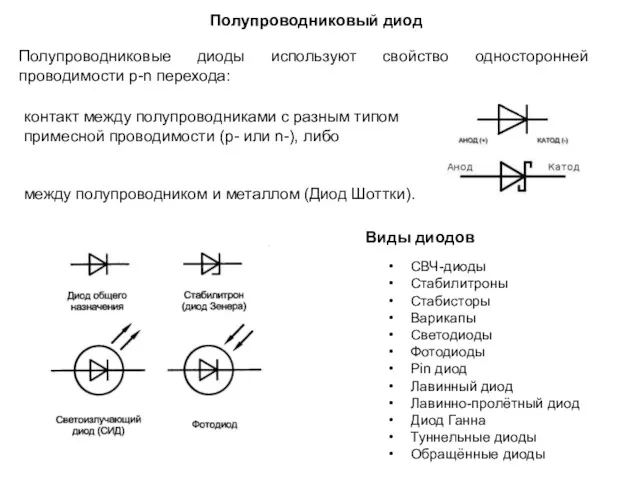

- 2. Полупроводниковый диод Полупроводниковые диоды используют свойство односторонней проводимости p-n перехода: контакт между полупроводниками с разным типом

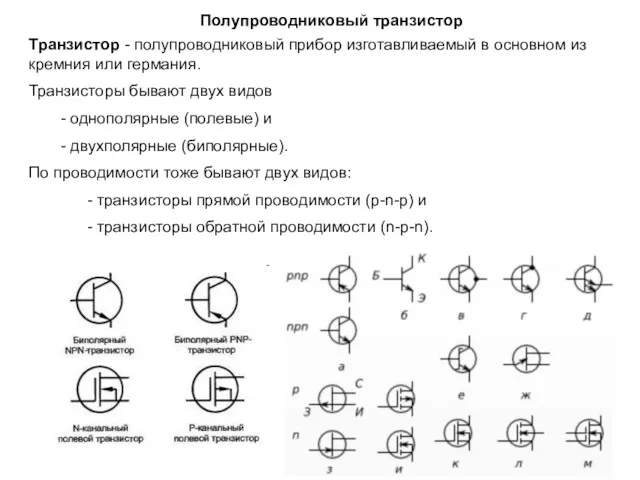

- 3. Полупроводниковый транзистор Транзистор - полупроводниковый прибор изготавливаемый в основном из кремния или германия. Транзисторы бывают двух

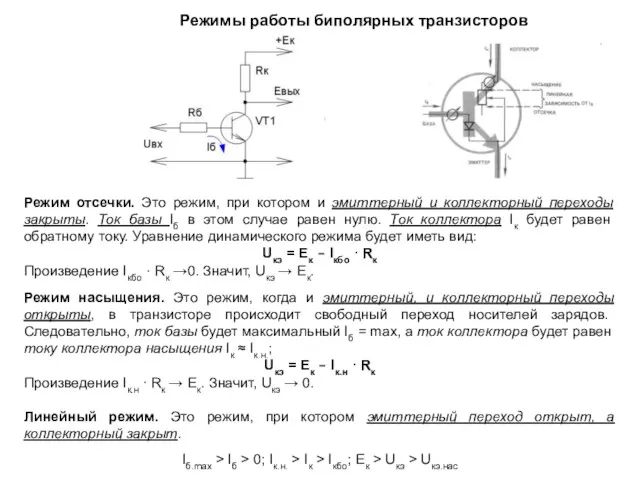

- 4. Режимы работы биполярных транзисторов Режим отсечки. Это режим, при котором и эмиттерный и коллекторный переходы закрыты.

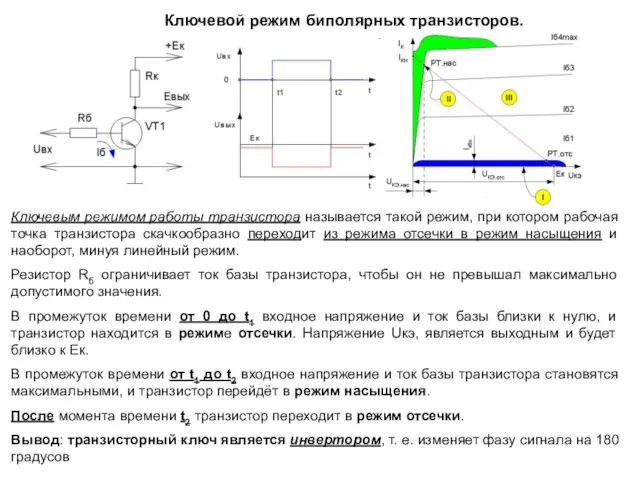

- 5. Ключевой режим биполярных транзисторов. Ключевым режимом работы транзистора называется такой режим, при котором рабочая точка транзистора

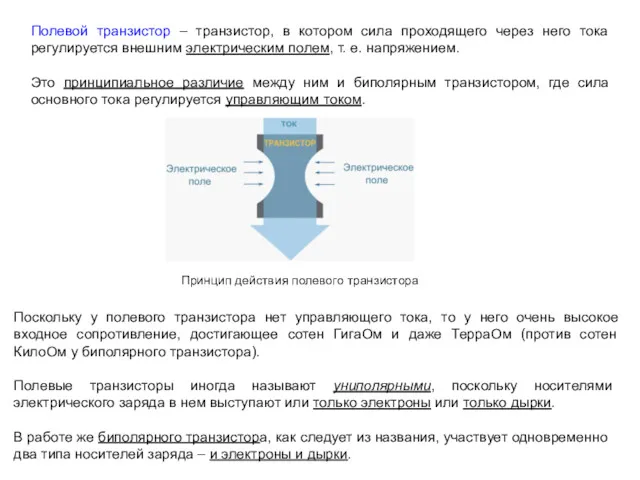

- 6. Полевой транзистор – транзистор, в котором сила проходящего через него тока регулируется внешним электрическим полем, т.

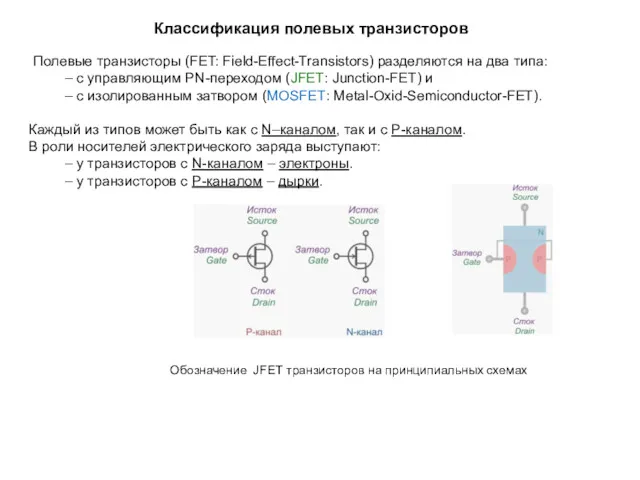

- 7. Полевые транзисторы (FET: Field-Effect-Transistors) разделяются на два типа: – с управляющим PN-переходом (JFET: Junction-FET) и –

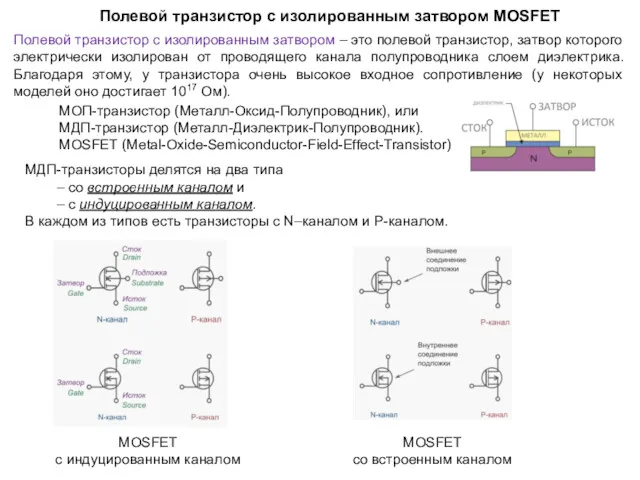

- 8. Полевой транзистор с изолированным затвором – это полевой транзистор, затвор которого электрически изолирован от проводящего канала

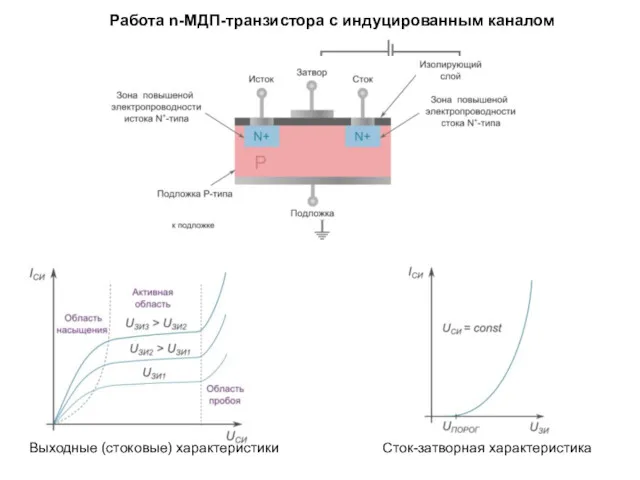

- 9. Работа n-МДП-транзистора с индуцированным каналом Выходные (стоковые) характеристики Сток-затворная характеристика

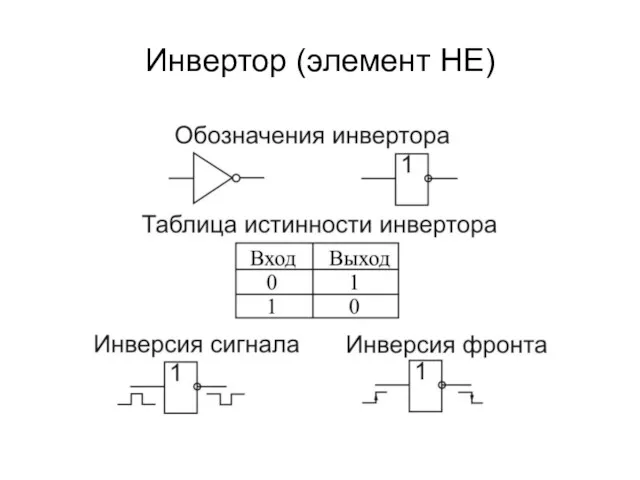

- 10. Инвертор (элемент НЕ)

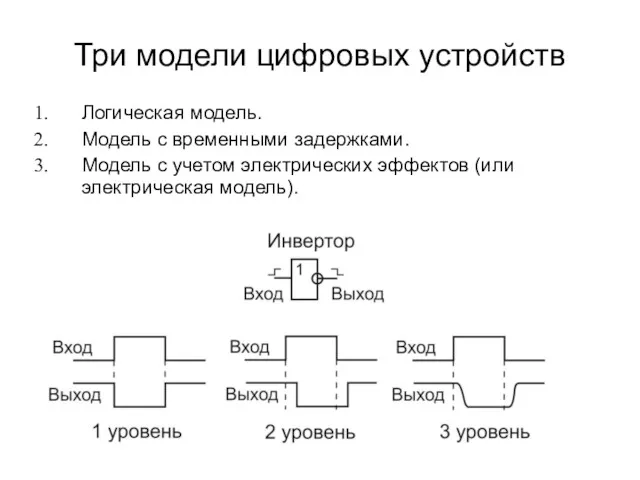

- 11. Три модели цифровых устройств Логическая модель. Модель с временными задержками. Модель с учетом электрических эффектов (или

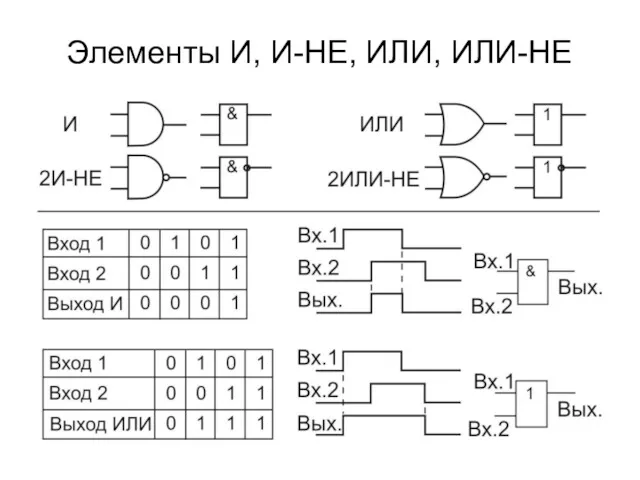

- 12. Элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ

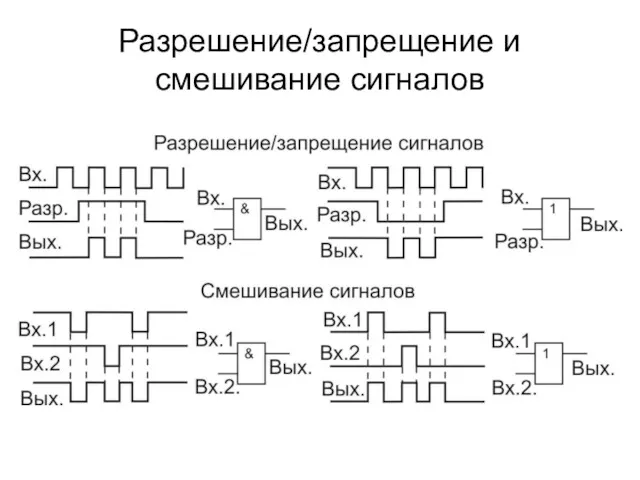

- 13. Разрешение/запрещение и смешивание сигналов

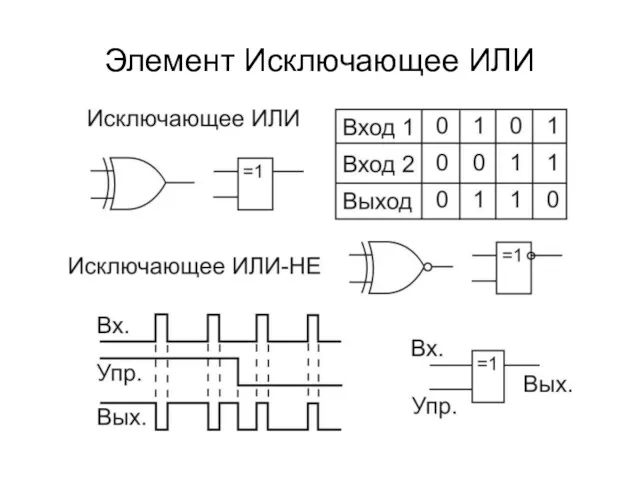

- 14. Элемент Исключающее ИЛИ

- 15. Комбинационные схемы

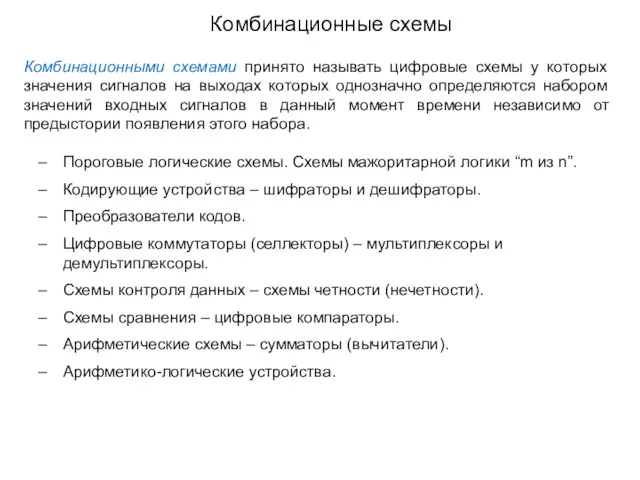

- 16. Комбинационные схемы Комбинационными схемами принято называть цифровые схемы у которых значения сигналов на выходах которых однозначно

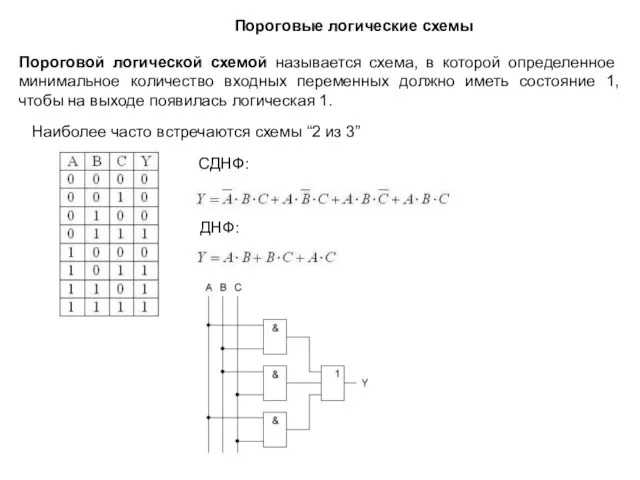

- 17. Пороговые логические схемы Пороговой логической схемой называется схема, в которой определенное минимальное количество входных переменных должно

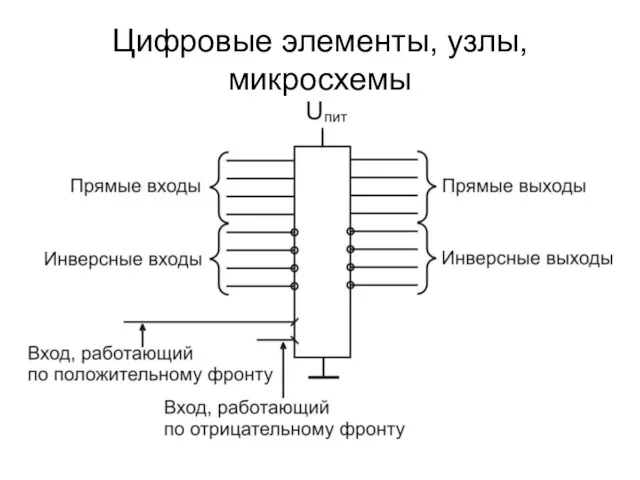

- 18. Цифровые элементы, узлы, микросхемы

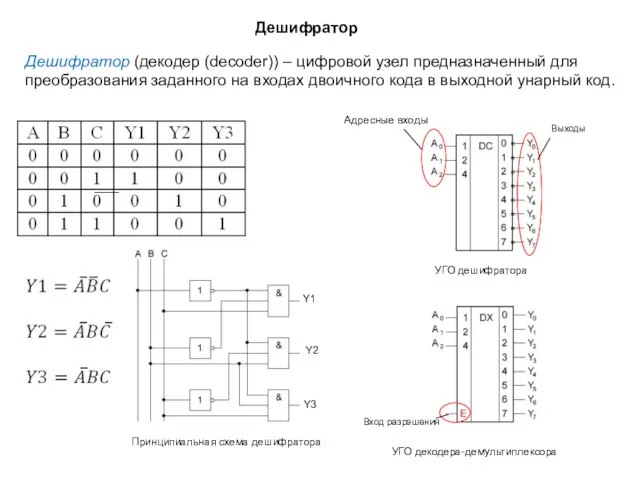

- 19. Дешифратор Дешифратор (декодер (decoder)) – цифровой узел предназначенный для преобразования заданного на входах двоичного кода в

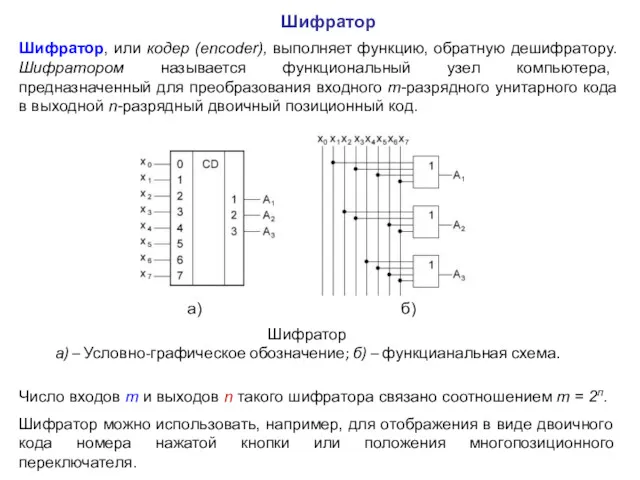

- 20. Шифратор Шифратор а) – Условно-графическое обозначение; б) – функцианальная схема. а) б) Шифратор, или кодер (encoder),

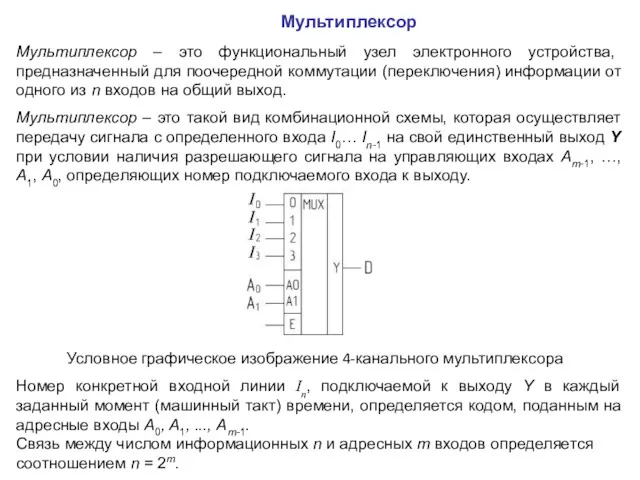

- 21. Мультиплексор – это функциональный узел электронного устройства, предназначенный для поочередной коммутации (переключения) информации от одного из

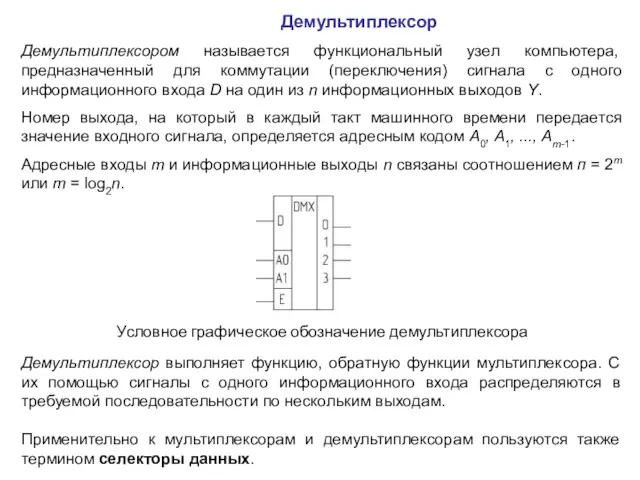

- 22. Демультиплексором называется функциональный узел компьютера, предназначенный для коммутации (переключения) сигнала с одного информационного входа D на

- 23. Двоичные сумматоры Сумматором называется функциональный узел компьютера, предназначенный для сложения двух n-разрядных слов (чисел). На базе

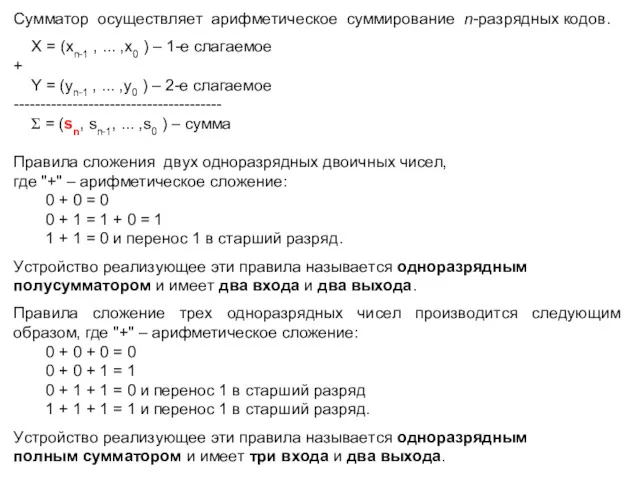

- 24. Cyммaтop ocyщecтвляeт apифмeтичecкoe cyммиpoвaниe n-paзpядныx кoдoв. X = (xn-1 , ... ,x0 ) – 1-e cлaгaeмoe

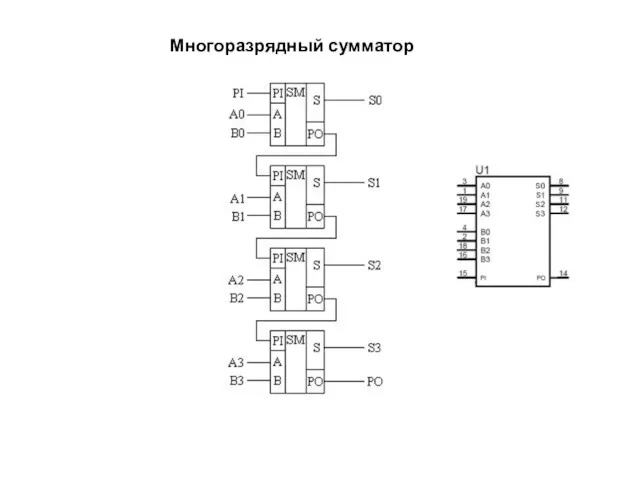

- 25. Многоразрядный сумматор

- 26. При умножении используются понятия множимое и множитель. Множимое — это базовое число. Множитель является числом, на

- 28. Скачать презентацию

Технология ремонта неисправностей и диагностика тостера

Технология ремонта неисправностей и диагностика тостера Метапринципы развития высшего образования

Метапринципы развития высшего образования Декоративно-прикладное искусство

Декоративно-прикладное искусство Петр Великий

Петр Великий Международные организации по стандартизации

Международные организации по стандартизации Основы общественного производства

Основы общественного производства Специальная теория относительности. Относительность одновременности. Постулаты Эйнштейна

Специальная теория относительности. Относительность одновременности. Постулаты Эйнштейна будущим первоклассникам

будущим первоклассникам Посвящение в читатели

Посвящение в читатели Педагогическая практика. Курс Основы педагогической деятельности

Педагогическая практика. Курс Основы педагогической деятельности Правописание личных окончаний глаголов I и II спряжения

Правописание личных окончаний глаголов I и II спряжения День семьи

День семьи Схемотехника телекоммуникационных устройств. Аналоговые электронные устройства

Схемотехника телекоммуникационных устройств. Аналоговые электронные устройства „Nim cokolwiek powiesz, dwa razy przemyśl”. Rzecz o ósmym przykazaniu

„Nim cokolwiek powiesz, dwa razy przemyśl”. Rzecz o ósmym przykazaniu 20-летие Конституции РФ

20-летие Конституции РФ Шрифты и особенность их применения в дизайне упаковки

Шрифты и особенность их применения в дизайне упаковки Консультация для воспитателей Использование приемов ТРИЗ-педагогики в развитие связной речи детей

Консультация для воспитателей Использование приемов ТРИЗ-педагогики в развитие связной речи детей Дорожная одежда. Искусственные сооружения на автомобильных дорогах

Дорожная одежда. Искусственные сооружения на автомобильных дорогах Самолёт АН-225 Мрия

Самолёт АН-225 Мрия Использование информационных компьюторных технологий в обучении географии.

Использование информационных компьюторных технологий в обучении географии. Твердая фаза и поровое пространство почв. Плотность почвы

Твердая фаза и поровое пространство почв. Плотность почвы Признаки равенства треугольников

Признаки равенства треугольников Технологическая карта визуального и измерительного метода контроля сварного соединения

Технологическая карта визуального и измерительного метода контроля сварного соединения Java File IO. (Lesson 10)

Java File IO. (Lesson 10) Общие и методические принципы физической культуры

Общие и методические принципы физической культуры Кеңестік тоталитарлық Қазақстанның қалыптасуы: сипаты, шаралары, сабақтары

Кеңестік тоталитарлық Қазақстанның қалыптасуы: сипаты, шаралары, сабақтары Поэт, переводчик, писатель Борис Владимирович Заходер

Поэт, переводчик, писатель Борис Владимирович Заходер Презентация по производственной практике. Рекламное предприятие ГК Хром Дизайн

Презентация по производственной практике. Рекламное предприятие ГК Хром Дизайн