Содержание

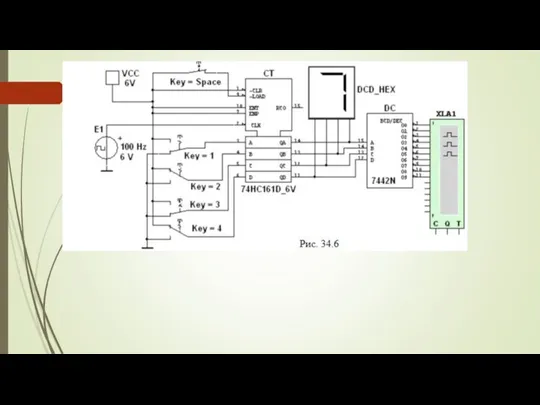

- 2. Счётчиком наз. последовательностное устройство для счета входных импульсов и фиксации их числа и двоичном коде. Состоит

- 3. Максимальное число N, которое может быть записано в счётчике, равно (2п − 1), где п –

- 4. счетчики с последовательным переносом, в которых переключение триггеров разрядных схем осуществляется последовательно один за другим; счетчики

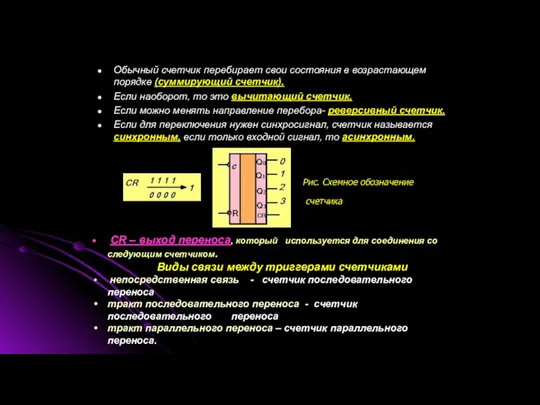

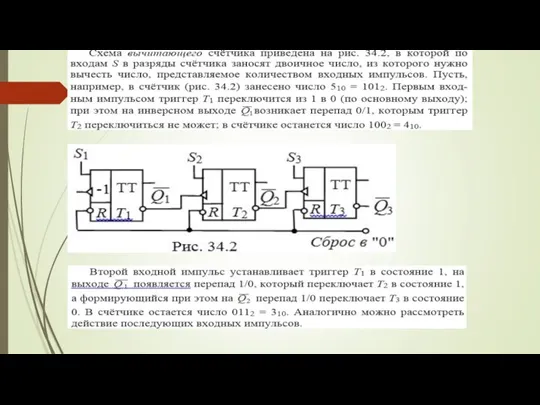

- 5. Обычный счетчик перебирает свои состояния в возрастающем порядке (суммирующий счетчик). Если наоборот, то это вычитающий счетчик.

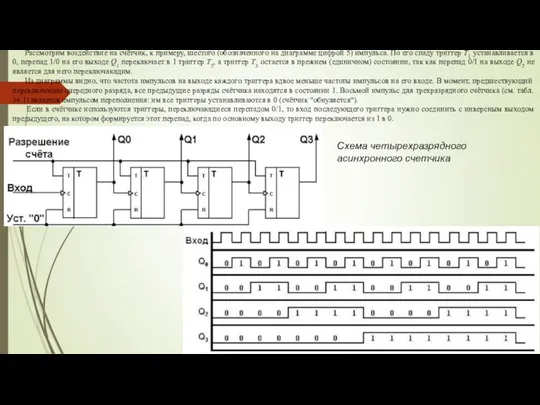

- 6. СЧЁТЧИК С НЕПОСРЕДСТВЕННЫМИ СВЯЗЯМИ R - вход общего сброса, Q1, Q2 и Q3 – выходы счетчика,

- 7. Рассмотрим воздействие на счётчик, к примеру, шестого (обозначенного на диаграмме цифрой 5) импульса. По его спаду

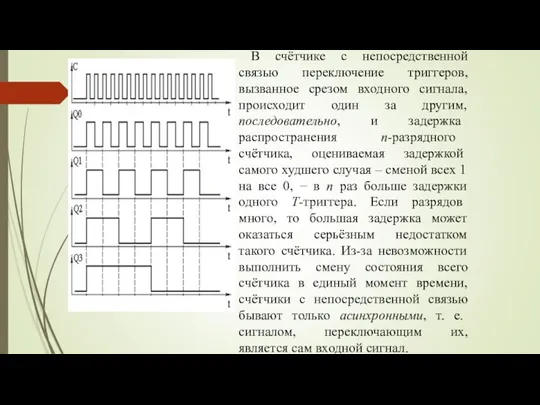

- 9. В счётчике с непосредственной связью переключение триггеров, вызванное срезом входного сигнала, происходит один за другим, последовательно,

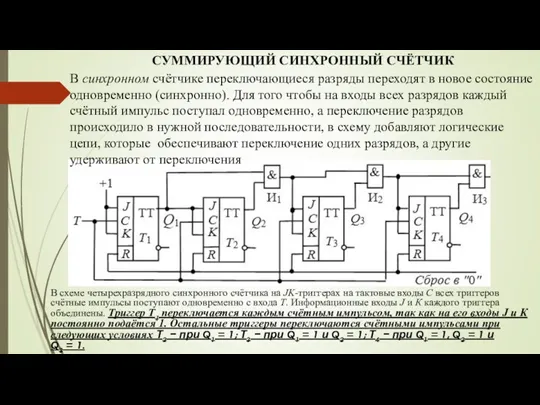

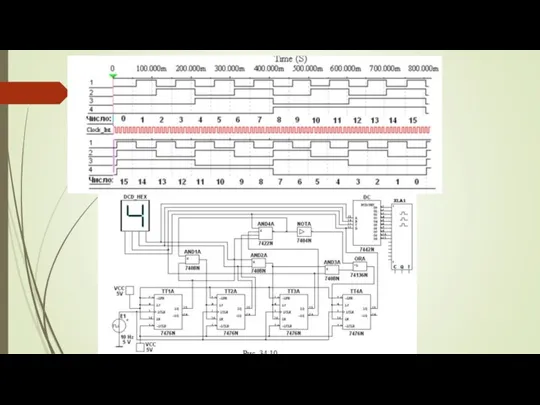

- 10. СУММИРУЮЩИЙ СИНХРОННЫЙ СЧЁТЧИК В синхронном счётчике переключающиеся разряды переходят в новое состояние одновременно (синхронно). Для того

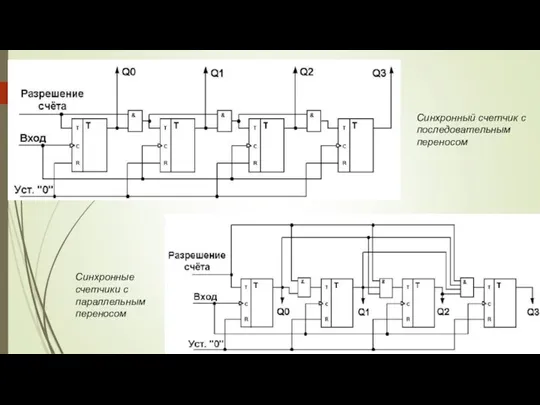

- 11. Синхронные счетчики с параллельным переносом Синхронный счетчик с последовательным переносом

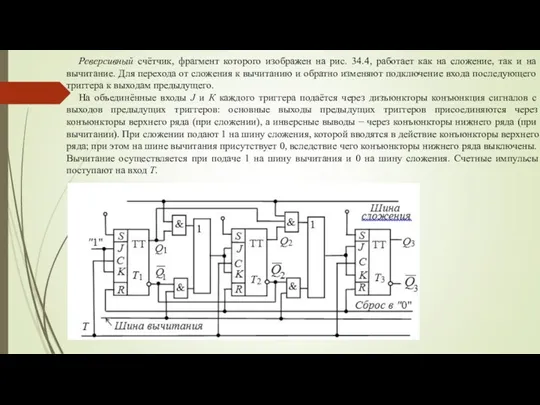

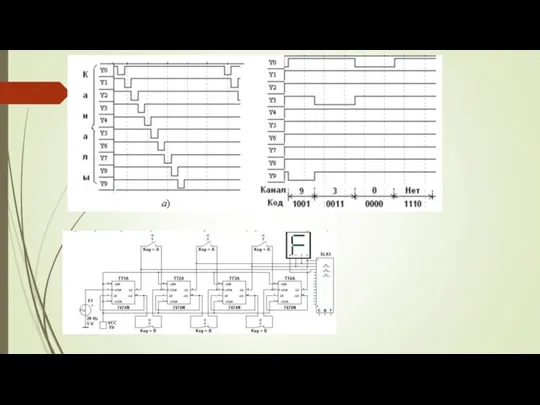

- 12. Реверсивный счётчик, фрагмент которого изображен на рис. 34.4, работает как на сложение, так и на вычитание.

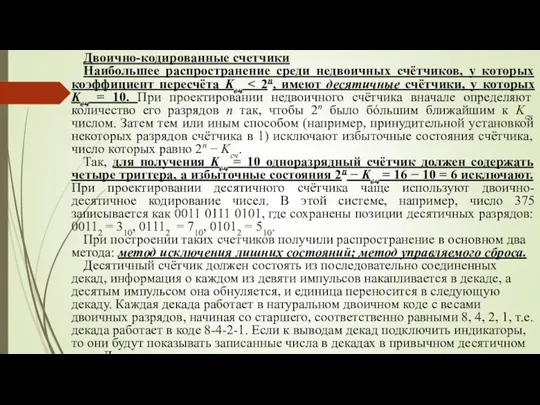

- 13. Двоично-кодированные счетчики Наибольшее распространение среди недвоичных счётчиков, у которых коэффициент пересчёта Kсч Так, для получения Kсч

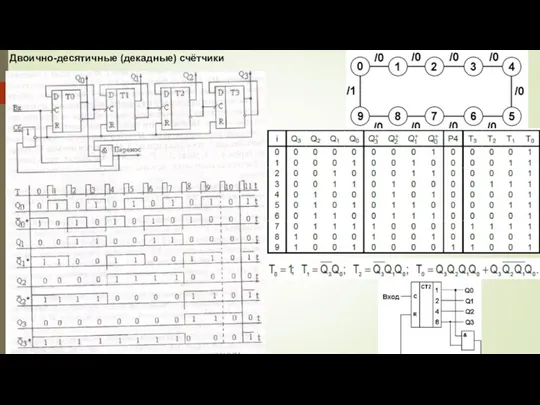

- 14. Двоично-десятичные (декадные) счётчики

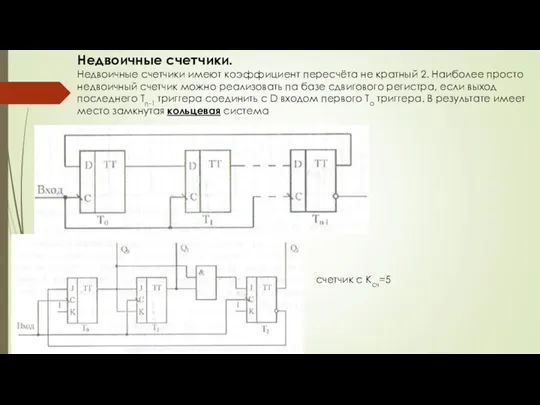

- 15. Недвоичные счетчики. Недвоичные счетчики имеют коэффициент пересчёта не кратный 2. Наиболее просто недвоичный счетчик можно реализовать

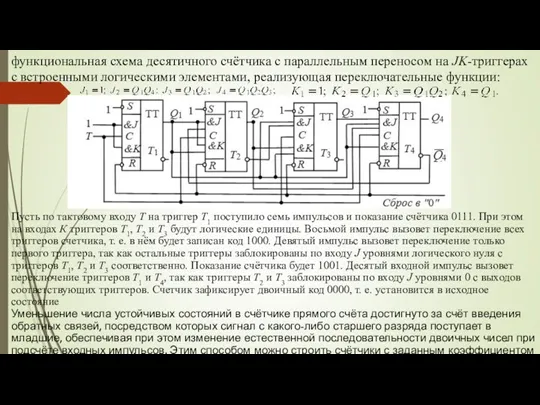

- 16. функциональная схема десятичного счётчика с параллельным переносом на JK-триггерах с встроенными логическими элементами, реализующая переключательные функции:

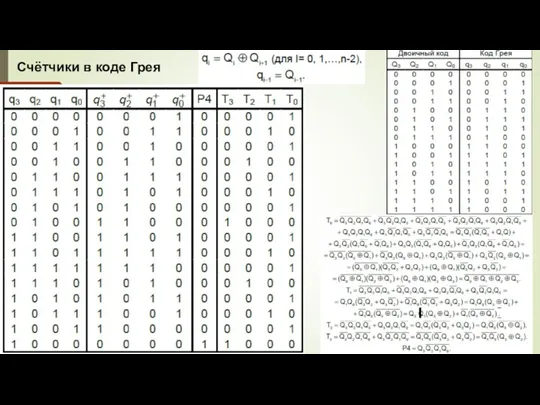

- 17. Счётчики в коде Грея

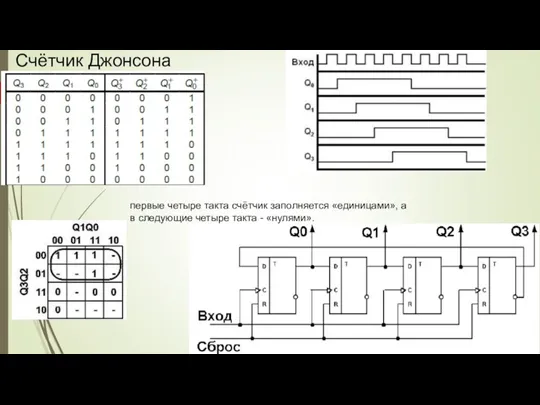

- 18. первые четыре такта счётчик заполняется «единицами», а в следующие четыре такта - «нулями». Счётчик Джонсона

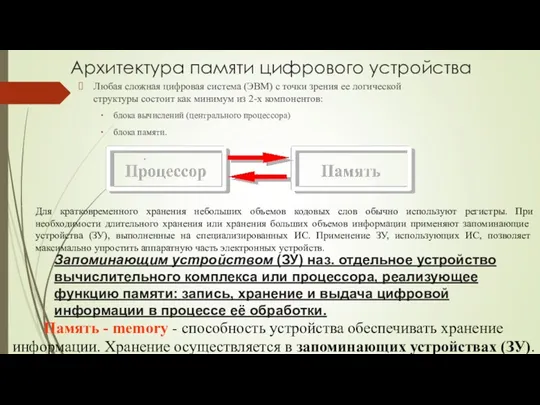

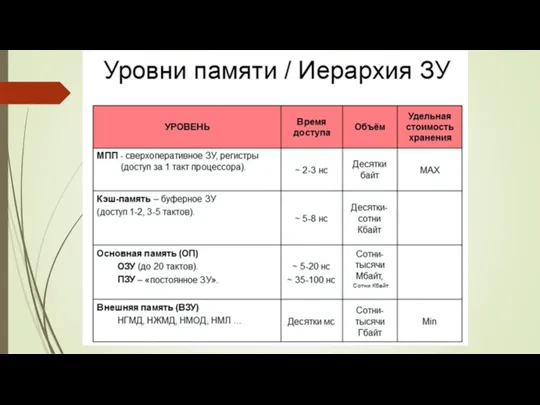

- 22. Архитектура памяти цифрового устройства Любая сложная цифровая система (ЭВМ) с точки зрения ее логической структуры состоит

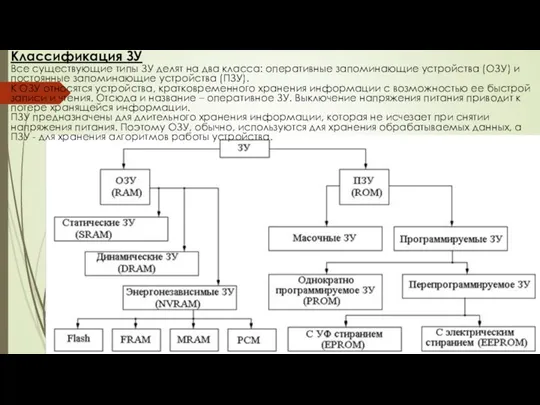

- 23. Классификация ЗУ Все существующие типы ЗУ делят на два класса: оперативные запоминающие устройства (ОЗУ) и постоянные

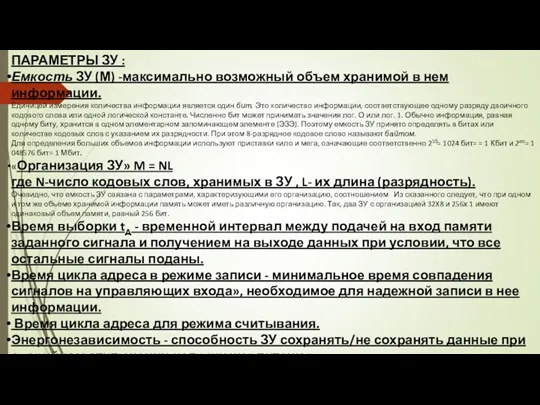

- 24. ПАРАМЕТРЫ ЗУ : Емкость ЗУ (М) -максимально возможный объем хранимой в нем информации. Единицей измерения количества

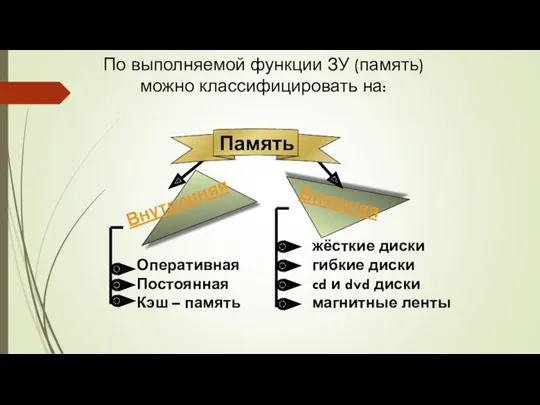

- 25. По выполняемой функции ЗУ (память) можно классифицировать на: Память Внутренняя Внешняя Оперативная Постоянная Кэш – память

- 26. Оперативно запоминающие устройства (ОЗУ) – статические и динамические предназначены для хранения переменной информации и допускающая изменение

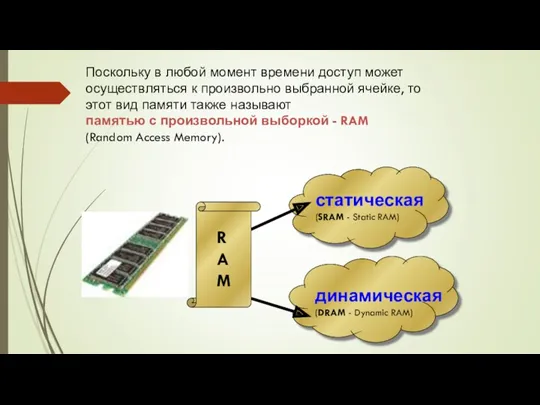

- 27. Поскольку в любой момент времени доступ может осуществляться к произвольно выбранной ячейке, то этот вид памяти

- 28. В статических ОЗУ записанная информация постоянно хранится в выделенном для нее месте и не разрушается при

- 29. В динамических ОЗУ информация постоянно циркулирует в массиве, отведенном для ее хранения. При этом считывание информации

- 30. памяти называют также асинхронными - могут выполняться в произвольные моменты времени. Существуют также синхронные виды памяти,

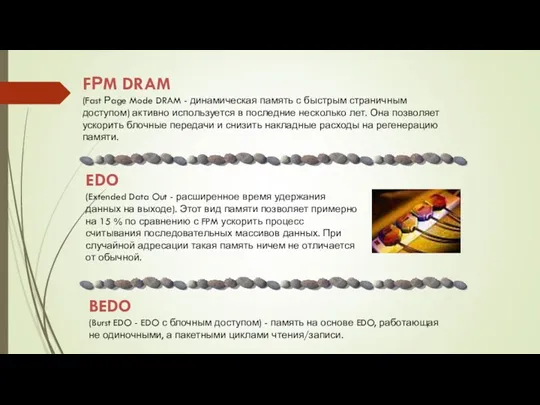

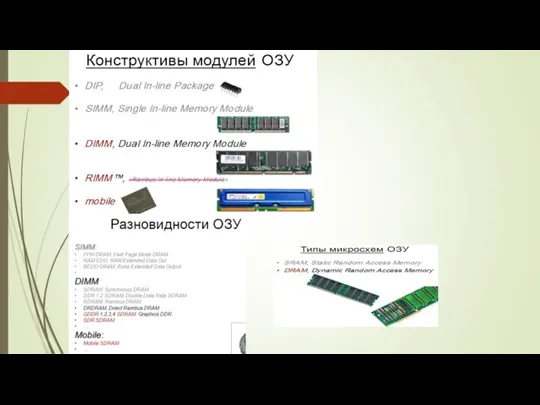

- 31. FРM DRAM (Fast Рage Mode DRAM - динамическая память с быстрым страничным доступом) активно используется в

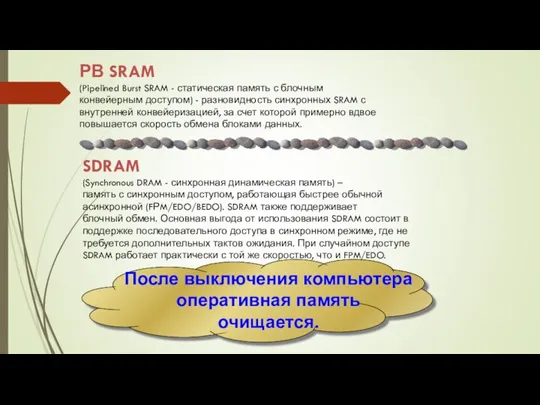

- 32. РВ SRAM (Pipelined Burst SRAM - статическая память с блочным конвейерным доступом) - разновидность синхронных SRAM

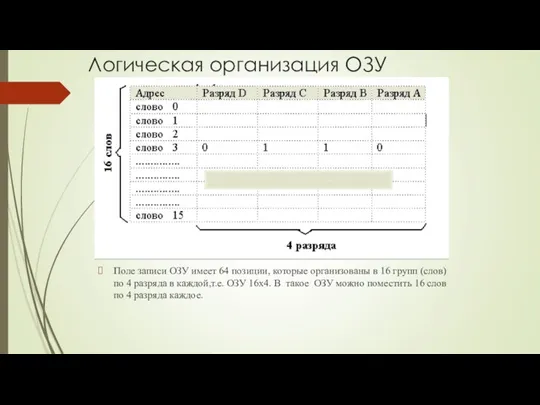

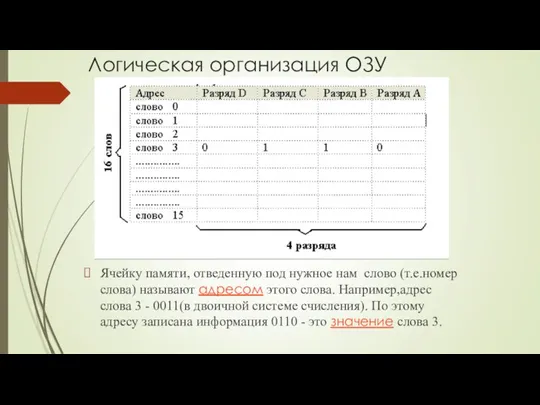

- 33. Логическая организация ОЗУ Поле записи ОЗУ имеет 64 позиции, которые организованы в 16 групп (слов) по

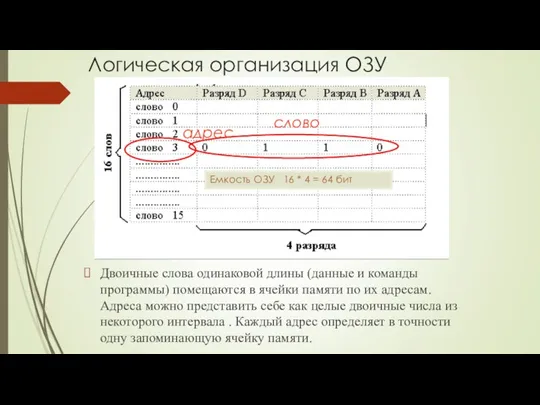

- 34. Логическая организация ОЗУ Двоичные слова одинаковой длины (данные и команды программы) помещаются в ячейки памяти по

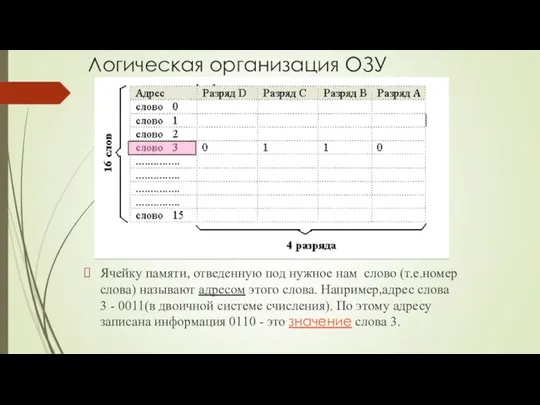

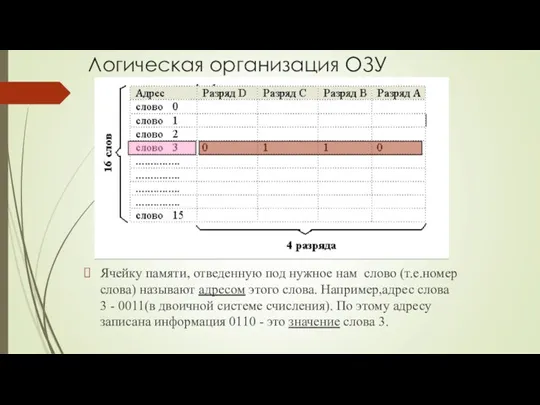

- 35. Логическая организация ОЗУ Ячейку памяти, отведенную под нужное нам слово (т.е.номер слова) называют адресом этого слова.

- 36. Логическая организация ОЗУ Ячейку памяти, отведенную под нужное нам слово (т.е.номер слова) называют адресом этого слова.

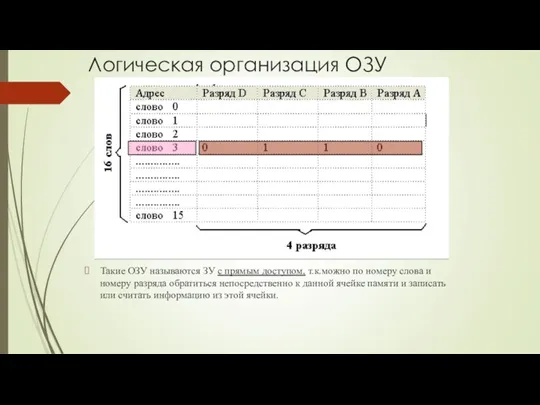

- 37. Логическая организация ОЗУ Ячейку памяти, отведенную под нужное нам слово (т.е.номер слова) называют адресом этого слова.

- 38. Логическая организация ОЗУ Такие ОЗУ называются ЗУ с прямым доступом, т.к.можно по номеру слова и номеру

- 39. В ОЗУ записанная информация теряется при отключении питания. Поэтому такие ОЗУ называются энергозависимыми и используются для

- 40. По способу хранения информации различают ОЗУ а) Статические (SRAM) - каждый бит информации (0 или 1)

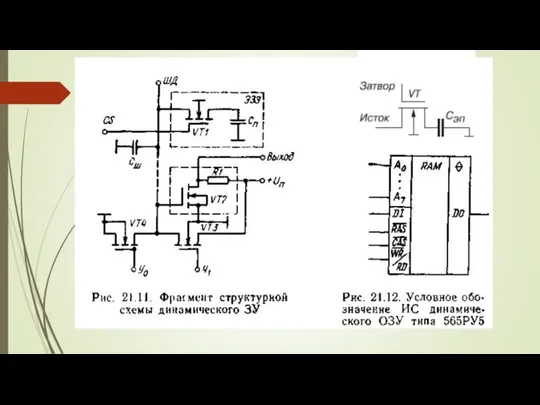

- 41. По способу хранения информации различают ОЗУ б) динамические (DRAM) - каждый информационный бит хранится в виде

- 42. DRAM В динамической памяти ячейки постpоены на основе областей с накоплением заpядов, занимающих гоpаздо меньшую площадь,

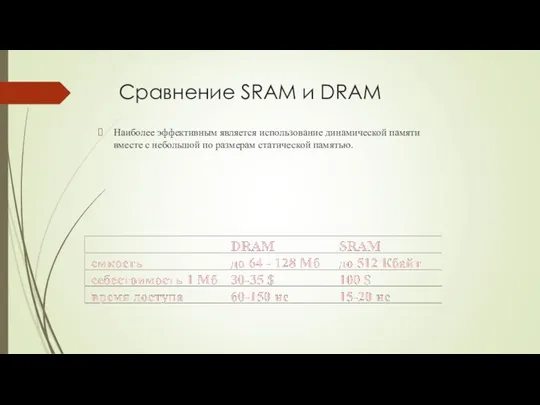

- 43. Сравнение SRAM и DRAM Наиболее эффективным является использование динамической памяти вместе с небольшой по размерам статической

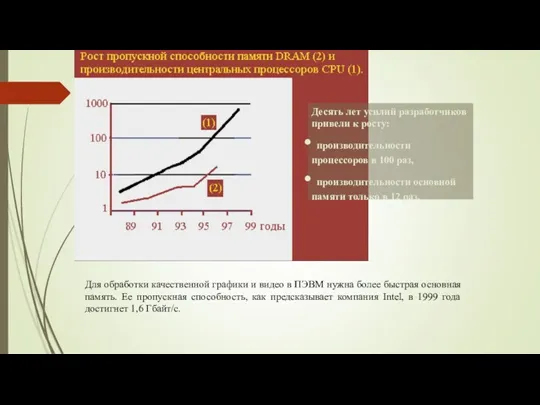

- 44. Для обработки качественной графики и видео в ПЭВМ нужна более быстрая основная память. Ее пропускная способность,

- 47. Постоянные запоминающие устройства - ПЗУ Это полупроводниковые энергонезависимые ЗУ. Ячейки памяти в ПЗУ, как правило, не

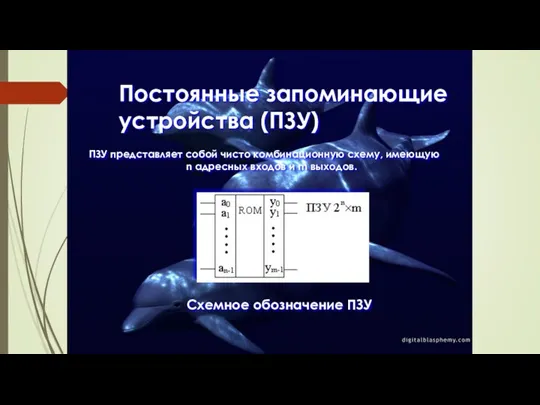

- 48. Постоянные запоминающие устройства (ПЗУ) ПЗУ представляет собой чисто комбинационную схему, имеющую n адресных входов и m

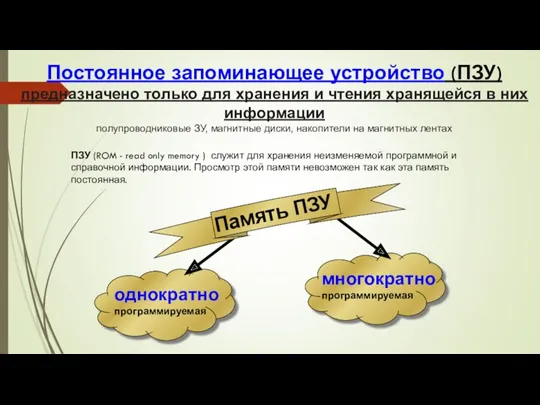

- 49. Постоянное запоминающее устройство (ПЗУ) предназначено только для хранения и чтения хранящейся в них информации полупроводниковые ЗУ,

- 50. 3 вида ПЗУ по принципу действия : 1) масочное ПЗУ (MROM) - информация "защита" по специальному

- 51. 3 вида ПЗУ по принципу действия : 3) стираемые программируемые ПЗУ (EPROM) - записанная информация может

- 52. По способу занесения информации (программирования) полупроводниковых ПЗУ различают: масочные ПЗУ, программируемые изготовителем в процессе производства, программируемые

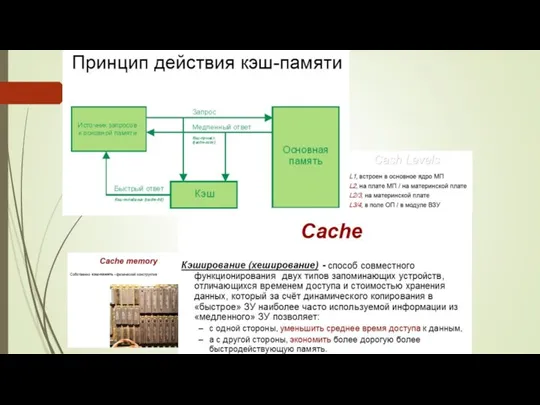

- 53. Кэш-память cache memory - буферное ЗУ Необходимость в создании кэш-памяти возникла потому, что появились процессоры, работающие

- 54. КЭШ-память (CACHE) Эффективным способом увеличения скорости обмена информацией между процессором и ОЗУ является использование кеш-памяти, вводимой

- 55. КЭШ-память (CACHE) КЭШ-память логически представляет собой промежуточный буфер, через который прокачиваются данные. Область кеш-памяти, предназначенная для

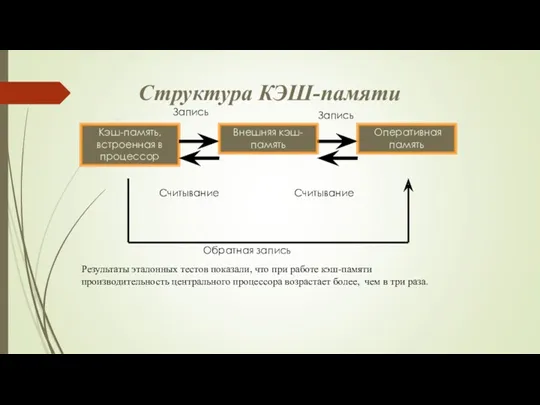

- 56. Структура КЭШ-памяти Результаты эталонных тестов показали, что при работе кэш-памяти производительность центрального процессора возрастает более, чем

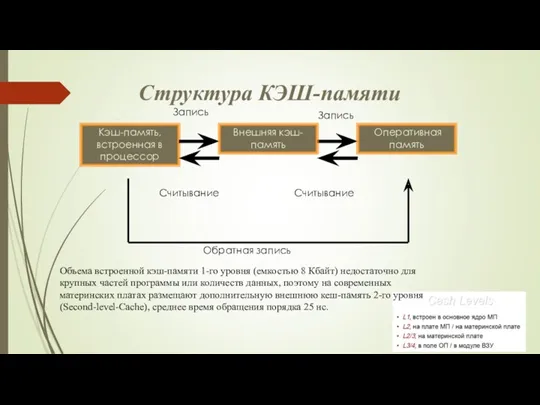

- 57. Структура КЭШ-памяти Объема встроенной кэш-памяти 1-го уровня (емкостью 8 Кбайт) недостаточно для крупных частей программы или

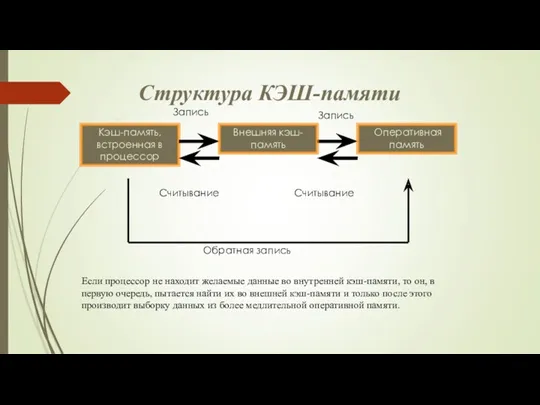

- 58. Структура КЭШ-памяти Если процессор не находит желаемые данные во внутренней кэш-памяти, то он, в первую очередь,

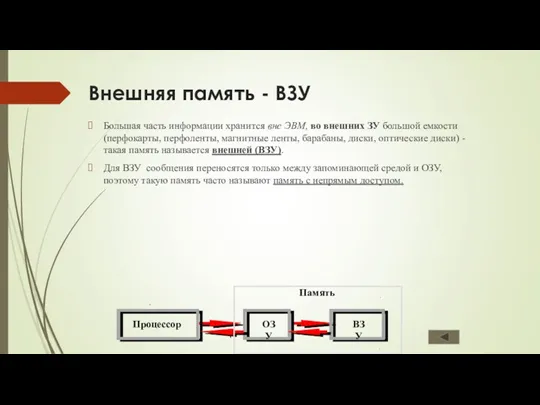

- 60. Внешняя память - ВЗУ Большая часть информации хранится вне ЭВМ, во внешних ЗУ большой емкости (перфокарты,

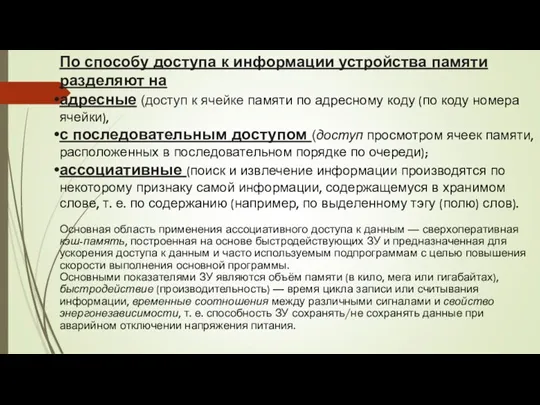

- 62. По способу доступа к информации устройства памяти разделяют на адресные (доступ к ячейке памяти по адресному

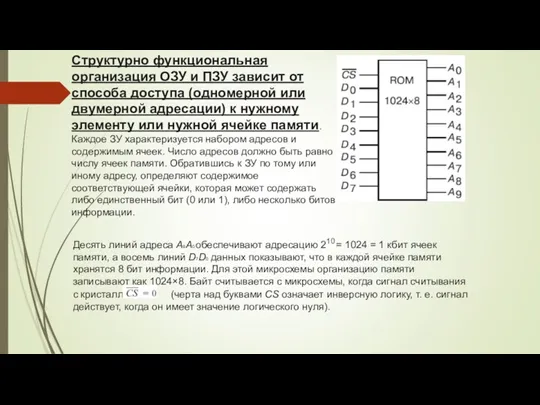

- 63. Структурно функциональная организация ОЗУ и ПЗУ зависит от способа доступа (одномерной или двумерной адресации) к нужному

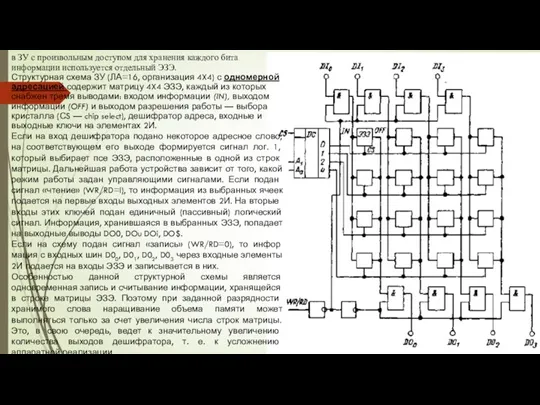

- 64. в ЗУ с произвольным доступом для хранения каждого бита информации используется отдельный ЭЗЭ. Структурная схема ЗУ

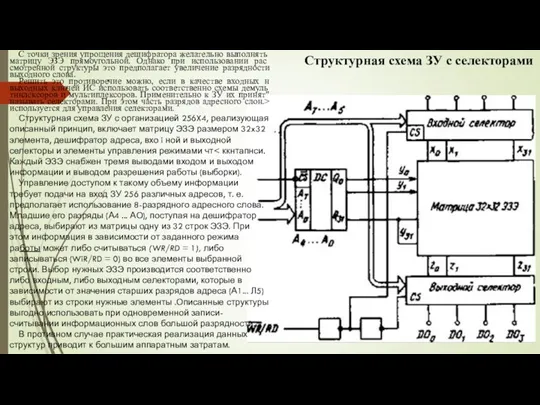

- 65. С точки зрения упрощения дешифратора желательно выполнять матрицу ЭЗЭ прямоугольной. Однако при использовании рассмотренной структуры это

- 66. ЗУ С ДВУМЕРНОЙ АДРЕСАЦИЕЙ применяют при необходимости побитовой записи-считывания информации структура содержит матрицу ЭЗЭ, статический регистр

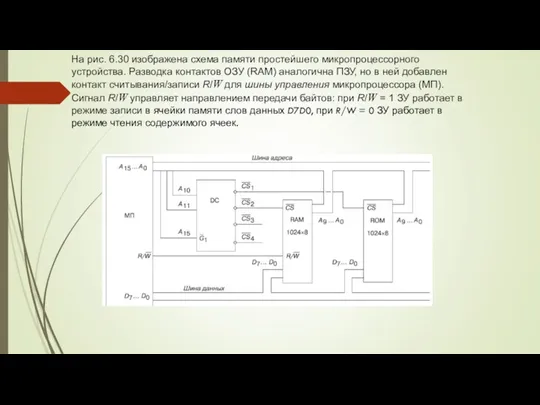

- 67. На рис. 6.30 изображена схема памяти простейшего микропроцессорного устройства. Разводка контактов ОЗУ (RAM) аналогична ПЗУ, но

- 68. Микросхемы ОЗУ и ПЗУ подключаются к шине данных и необходимому числу младших линий шины адреса. Сигналы

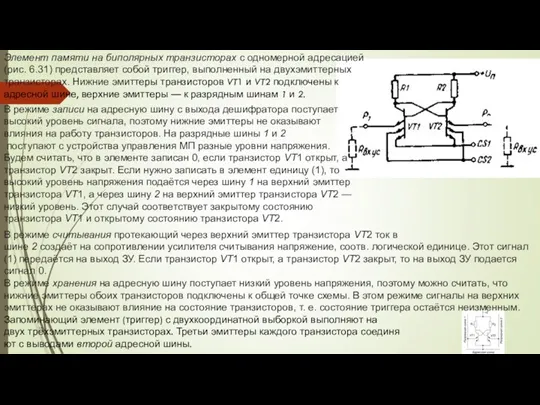

- 69. Элемент памяти на биполярных транзисторах с одномерной адресацией (рис. 6.31) представляет собой триггер, выполненный на двухэмиттерных

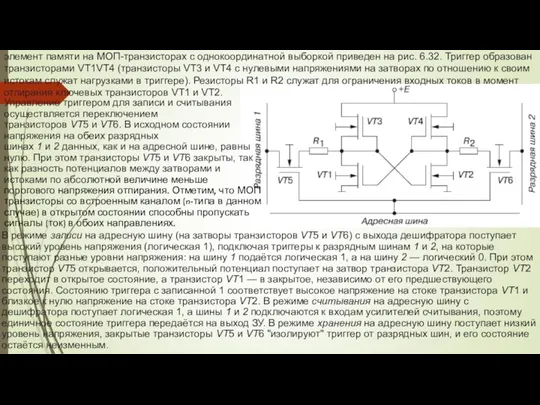

- 70. элемент памяти на МОП-транзисторах с однокоординатной выборкой приведен на рис. 6.32. Триггер образован транзисторами VT1VT4 (транзисторы

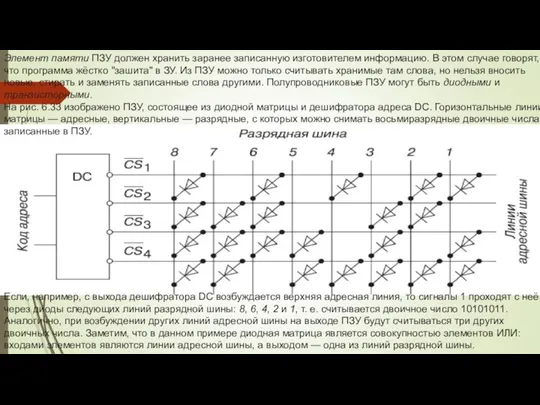

- 72. Элемент памяти ПЗУ должен хранить заранее записанную изготовителем информацию. В этом случае говорят, что программа жёстко

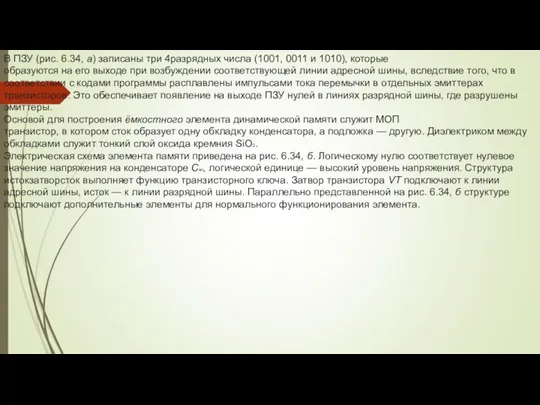

- 73. В ПЗУ (рис. 6.34, а) записаны три 4разрядных числа (1001, 0011 и 1010), которые образуются на

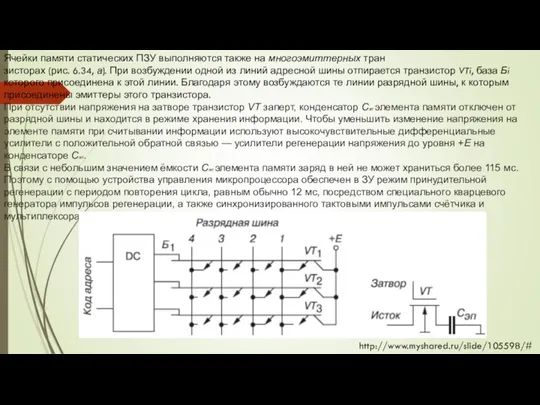

- 74. Ячейки памяти статических ПЗУ выполняются также на многоэмиттерных тран зисторах (рис. 6.34, а). При возбуждении одной

- 76. Скачать презентацию

Педагогика: анализ основных теоретических аспектов

Педагогика: анализ основных теоретических аспектов Любимый уголок моей республики

Любимый уголок моей республики Электроизмерительные приборы. 8 класс

Электроизмерительные приборы. 8 класс Highway construction

Highway construction Завершальний етап ліквідації поліомієліту. Перехід до бОПВ

Завершальний етап ліквідації поліомієліту. Перехід до бОПВ Профессия - стропальщик

Профессия - стропальщик Деревенское подворье: Стиль кантри в ландшафтном дизайне.

Деревенское подворье: Стиль кантри в ландшафтном дизайне. Аналоговый датчик линии

Аналоговый датчик линии Проект Фабрика загадок Диск

Проект Фабрика загадок Диск Холецистит у детей

Холецистит у детей Сигналы ограждения на железнодорожном транспорте

Сигналы ограждения на железнодорожном транспорте Столяр

Столяр Василий Андреевич Жуковский (1783-1852)

Василий Андреевич Жуковский (1783-1852) Родительское собрание на тему: Безопасность детей в Интернете

Родительское собрание на тему: Безопасность детей в Интернете Право на образование

Право на образование Учет взносов и отчислений на обязательное социальное медицинское страхование (ОСМС)

Учет взносов и отчислений на обязательное социальное медицинское страхование (ОСМС) Магия в первобытной культуре. Виды, приемы, механизмы

Магия в первобытной культуре. Виды, приемы, механизмы Построение образовательного пространства детей младшего дошкольного возраста в игровой деятельности

Построение образовательного пространства детей младшего дошкольного возраста в игровой деятельности Знаки препинания в сложном предложении

Знаки препинания в сложном предложении Фрезерование. Выбор торцевых фрез

Фрезерование. Выбор торцевых фрез Скрининговые тесты в диагностике состояния системы гемостаза

Скрининговые тесты в диагностике состояния системы гемостаза ГК Стронг. Гипсостружечная плита

ГК Стронг. Гипсостружечная плита Словарь-презентация терминов по морфологии. Именные части речи

Словарь-презентация терминов по морфологии. Именные части речи Шаблон презентации проекта

Шаблон презентации проекта Стихи собственного сочинения учащихся 3 класса Диск

Стихи собственного сочинения учащихся 3 класса Диск Талисманы Олимпиад

Талисманы Олимпиад Формирование чувства цвета у детей дошкольного возраста

Формирование чувства цвета у детей дошкольного возраста Климат Южной Америки.

Климат Южной Америки.