Содержание

- 2. Суперскалярность – архитектура вычислительного ядра, при которой наиболее нагруженные блоки могут входить в нескольких экземплярах. Скажем,

- 3. Процессоры x86 имеет 5-ти ступенчатый конвейер. Соответствующие этапы включают: выборку команд из кэш-памяти или оперативной памяти;

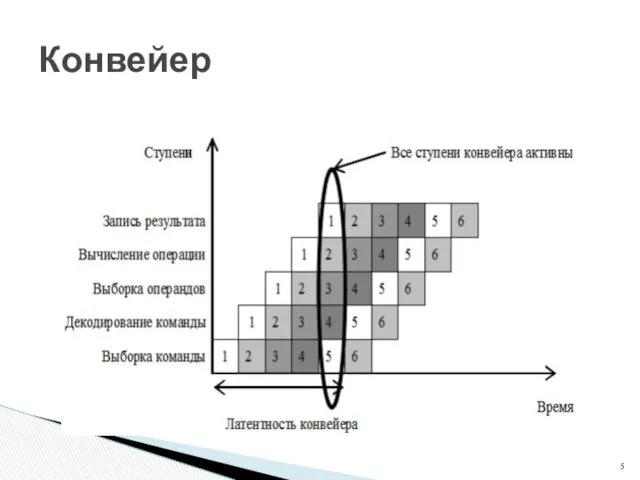

- 4. Конвейер

- 5. Конвейер

- 6. Обработка команды, или цикл процессора, может быть разделена на несколько основных этапов, которые можно назвать микрокомандами.

- 7. Таким образом, на выходе конвейера на каждом такте процессора появляется результат обработки одной команды (одна команда

- 8. Несмотря на все технологии и уловки разработчиков, производительность процессора все-таки напрямую зависит от скорости выборки команд

- 9. КЭШ-память строится на базе дорогой SRAM-памяти (static random access memory), обеспечивающей доступ к ячейкам памяти гораздо

- 10. КЭШ-память более высокого уровня всегда больше по размеру и медленнее КЭШ-памяти более низкого уровня. Самая быстрая

- 11. КЭШ-память второго уровня – более медленная (время доступа, в среднем, 8-20 тактов процессора), но зато имеет

- 12. Процессор считывает из основной оперативной памяти данные и заносит их в КЭШ-память всех уровней, замещая данные,

- 13. Однако, чем больше уровней КЭШ-памяти, тем сложнее алгоритм замещения устаревших данных и тем больше времени тратится

- 14. Эксперименты свидетельствуют, что в среднестатистическом "домашнем" процессоре влияние размера кэша на производительность находится в пределах 10

- 15. Архитектура ЭВМ - это многоуровневая иерархия аппаратурнопрограммных средств, из которых строится ЭВМ. Каждый из уровней допускает

- 16. На современном этапе развития вычислительной техники существуют две основные архитектуры набора команд. используемые компьютерной промышленностью. -

- 17. При проектировании супер-миникомпьютеров на базе последних достижений СБИС-технологии оказалось невозможным полностью перенести в нее архитектуру удачного

- 18. каждая команда независимо от ее типа выполняется за один машинный цикл, длительность которого должна быть максимально

- 19. Фиксированная длина машинных инструкций (например, 32 бита) и простой формат команды. Специализированные команды для операций с

- 20. Отсутствие поддержки операций вида «изменить» над укороченными типами данных — байт, 16-разрядное слово. Так, например, система

- 21. Отсутствие микропрограмм внутри самого процессора. То, что в CISC-процессоре исполняется микропрограммами, в RISC-процессоре исполняется как обыкновенный

- 22. RISC - Набор команд в процессорах построенных на данной архитектуре упрощенный. Что позволяет поднять частоту, снизить

- 23. В результате, хотя RISC-процессоры и требуют выполнения большего количества инструкций для решения одной и той же

- 24. Однако, несмотря на явное преимущество RISC, процессоры не получили столь серьезного распространения, как CISC. Правда, связано

- 25. В результате, экономически крайне невыгодно переписывать все программы, которые уже разработаны, отлажены и используются огромным количеством

- 26. На сегодняшний день CISC- процессоры почти монопольно занимают на компьютерном рынке сектор персональных компьютеров. RISC-процессорам нет

- 27. ARM (от англ. Advanced RISC Machine — усовершенствованная RISC-машина; иногда — Acorn RISC Machine) — семейство

- 28. В 2007 году около 98 % из более чем миллиарда мобильных телефонов, продаваемых ежегодно, были оснащены,

- 29. В основном процессоры семейства завоевали сегмент массовых мобильных продуктов (сотовые телефоны, карманные компьютеры) и встраиваемых систем

- 30. MISC (Minimal Instruction Set Computer) – дальнейшее развитие архитектуры RISС, основанное на еще большем упрощении инструкций

- 31. VLIW (Very long instruction word) – архитектура процессоров, использующая инструкции большой длины, содержащие сразу несколько операций,

- 32. Подход VLIW сильно упрощает архитектуру процессора, перекладывая задачу распределения вычислительных устройств на компилятор. Поскольку отсутствуют большие

- 34. Скачать презентацию

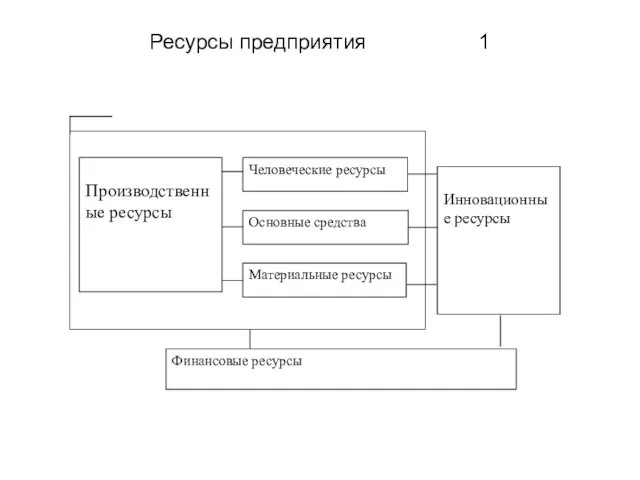

Ресурсы предприятия

Ресурсы предприятия 8 Июля - День семьи, любви и верности

8 Июля - День семьи, любви и верности Познавательное развитие дошкольников с задержкой психического развития

Познавательное развитие дошкольников с задержкой психического развития Применение игровой технологии при обобщении учебного материала на уроках географии.

Применение игровой технологии при обобщении учебного материала на уроках географии. Детско-юношеский клуб Мечтатели

Детско-юношеский клуб Мечтатели Древнейший период развития края. Старая Ладога

Древнейший период развития края. Старая Ладога Свет и цвет в фотографии

Свет и цвет в фотографии презентация Озеленения школьных помещений

презентация Озеленения школьных помещений Ишемическая болезнь сердца. Часть 1. Атеросклероз. Стенокардия

Ишемическая болезнь сердца. Часть 1. Атеросклероз. Стенокардия Юрий Трифонов. Жизнь и творчество

Юрий Трифонов. Жизнь и творчество Аттестация испытательного оборудования. (Лекция 21)

Аттестация испытательного оборудования. (Лекция 21) Цветы в технике квиллинга

Цветы в технике квиллинга Новое слово в маркетинге. Маркетинг. План. Системы

Новое слово в маркетинге. Маркетинг. План. Системы Энергетические показатели ТЭС. Лекция 2

Энергетические показатели ТЭС. Лекция 2 Неопределенная форма глагола. 3 класс

Неопределенная форма глагола. 3 класс В помощь психологу ДОУ

В помощь психологу ДОУ Родительское собрание в подготовительной группе

Родительское собрание в подготовительной группе ПРЕЗЕНТАЦИЯ ВИКТОРИНА ПО ПОЖАРНОЙ БЕЗОПАСНОСТИ

ПРЕЗЕНТАЦИЯ ВИКТОРИНА ПО ПОЖАРНОЙ БЕЗОПАСНОСТИ Үгінді печенье

Үгінді печенье Что такое программирование

Что такое программирование Происхождение жизни на Земле. Космические и планетарные условия. Физико-химические условия

Происхождение жизни на Земле. Космические и планетарные условия. Физико-химические условия Движение. Виды движений

Движение. Виды движений Внутрикостный инъектор

Внутрикостный инъектор Прихват бурильной колонны и методы борьбы с ним. Семинар 12

Прихват бурильной колонны и методы борьбы с ним. Семинар 12 интерактивная презентация к уроку Массовая доля элемента в молекуле

интерактивная презентация к уроку Массовая доля элемента в молекуле The Grounds For Judicial Review

The Grounds For Judicial Review Женщины в жизни Александра Сергеевича Пушкина

Женщины в жизни Александра Сергеевича Пушкина Волшебные слова

Волшебные слова