Содержание

- 2. Комбинационные схемы Комбинационными схемами принято называть цифровые схемы у которых значения сигналов на выходах однозначно определяются

- 3. Пороговые логические схемы Пороговой логической схемой называется схема, в которой определенное минимальное количество входных переменных должно

- 4. Дешифратор Дешифратор (декодер (decoder)) – цифровой узел предназначенный для преобразования заданного на входах двоичного кода в

- 5. УГО дешифратора УГО декодера-демультиплексора Вход разрешения выхода Адресные входы Выходы Условно-графические обозначения дешифраторов

- 6. Линейный дешифратор 3→8 Буферные усилители

- 7. Расширение числа выходов дешифратора. Каскадирование Дешифратор 4→16. Пирамидальное соединение Дешифратор 4→10. Каскадное соединение Дешифратор 4→16. Параллельное

- 8. Двухкаскадный дешифратор 4→16. Матричный (прямоугольный) дешифратор

- 9. Шифратор Рис. 1. Шифратор 8 → 3 а) – Условно-графическое обозначение; б) – функцианальная схема. а)

- 10. Рис. 2. Блок выделения старшей единицы Схема выделения старшей единицы преобразует m-разрядное слово следующим образом: все

- 11. Рис. 3. Наращивание разрядности микросхем приоритетных шифраторов: а) до шестнадцати входов. Шифратор 16→4; б) до десяти

- 12. Синтез кодовых преобразователей Рис. 4. Кодовый преобразователь, синтезированный как система булевых функций.

- 13. Рис. 5. Кодовый преобразователь, построенный как структура декодер→кодер.

- 14. Рис. 6. Функциональные узлы криптографической защиты информации: а) – перестановки и б) – подстановки. Узел перестановки

- 15. Мультиплексором называется функциональный узел электронного устройства, предназначенный для поочередной коммутации (переключения) информации от одного из n

- 16. Таблица истинности мультиплексора Рис. 8. Принципиальная схема мультиплексора 4→1

- 17. Каскадирование мультиплексоров Каскадирование позволяет реализовать коммутацию произвольного числа входных линий на базе серийных микросхем мультиплексоров меньшей

- 18. Старшие разряды адреса А3, A2 подаются на адресные входы мультиплексора второго уровня, на выходе которого формируется

- 19. Демультиплексором называется функциональный узел компьютера, предназначенный для коммутации (переключения) сигнала с одного информационного входа D на

- 20. Таблица истинности демультиплексора Рис. 11. Принципиальная схема демультиплексора 1→4

- 22. Скачать презентацию

Монтаж комплектных трансформаторных подстанций

Монтаж комплектных трансформаторных подстанций Теплом своих рук школу озеленим вокруг!

Теплом своих рук школу озеленим вокруг! Презентация к сказке Снежная королева

Презентация к сказке Снежная королева СССР в 1970-1985 годах

СССР в 1970-1985 годах Эти удивительные металлы

Эти удивительные металлы Элементы дискурс анализа для обучения чтению при подготовке к международным экзаменам по английскому языку

Элементы дискурс анализа для обучения чтению при подготовке к международным экзаменам по английскому языку Виды спорта

Виды спорта CASE-технологии

CASE-технологии Подготовка к математическому тестированию Кенгуру-выпускникам Часть 1

Подготовка к математическому тестированию Кенгуру-выпускникам Часть 1 Квилинг

Квилинг Сочинение по картине Исаака Левитана Весна. Большая вода

Сочинение по картине Исаака Левитана Весна. Большая вода Микропроцессорная система сбора и распределения информации SAU 8800 (Signal Acquisition Units)

Микропроцессорная система сбора и распределения информации SAU 8800 (Signal Acquisition Units) Психические процессы. Структура психики

Психические процессы. Структура психики Классный часБереги здоровье смолоду

Классный часБереги здоровье смолоду Череп человека. Развитие, общая форма, изменчивость

Череп человека. Развитие, общая форма, изменчивость Через знания к звездам. Школьная газета

Через знания к звездам. Школьная газета Электрооборудование пассажирских вагонов в поездах

Электрооборудование пассажирских вагонов в поездах Технология выполнения высококачественной штукатурки

Технология выполнения высококачественной штукатурки Конкурс Самый классный классный

Конкурс Самый классный классный Рельеф Земли. Равнины

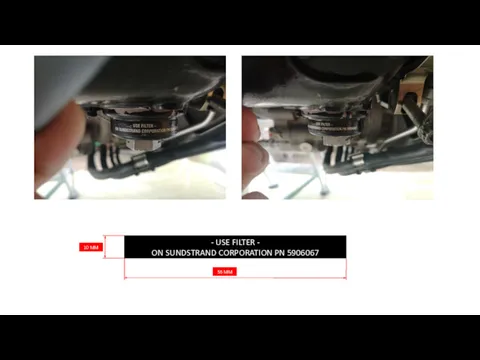

Рельеф Земли. Равнины Use filter on sundstrand corporation pn 5906067 55 mm

Use filter on sundstrand corporation pn 5906067 55 mm Автоматический радиокомпас АРК-15

Автоматический радиокомпас АРК-15 Процесс завершения проекта и мониторинг выгод. (Модуль 6)

Процесс завершения проекта и мониторинг выгод. (Модуль 6) Презентация Новогодние поделки

Презентация Новогодние поделки Курсовая работа здание спортивного комплекса

Курсовая работа здание спортивного комплекса Народная кукла-оберег. Травница.

Народная кукла-оберег. Травница. Путешествие в город Смехоград

Путешествие в город Смехоград Натюрморт

Натюрморт