Содержание

- 2. Цифровая схемотехника существенно отличается от аналоговой. При распространении логических сигналов по цифровой схеме они не затухают.

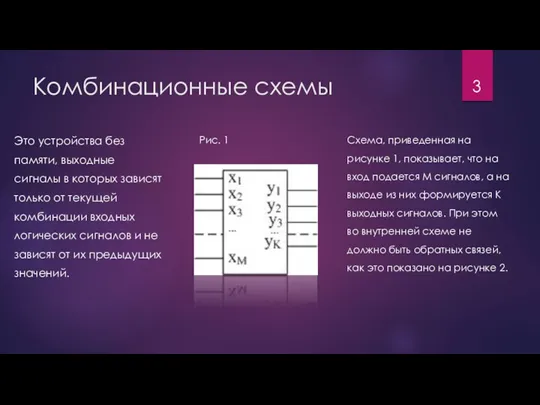

- 3. Комбинационные схемы Это устройства без памяти, выходные сигналы в которых зависят только от текущей комбинации входных

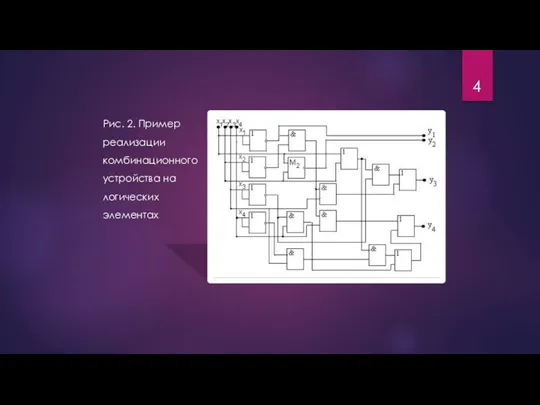

- 4. Рис. 2. Пример реализации комбинационного устройства на логических элементах

- 5. При проектировании цифрового комбинационного устройства исходное задание обычно описывается при помощи таблицы истинности. По ней с

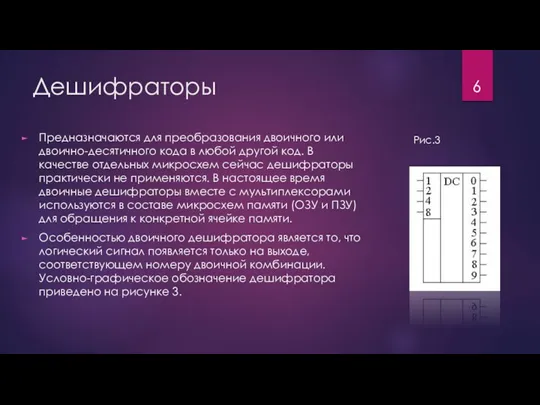

- 6. Дешифраторы Предназначаются для преобразования двоичного или двоично-десятичного кода в любой другой код. В качестве отдельных микросхем

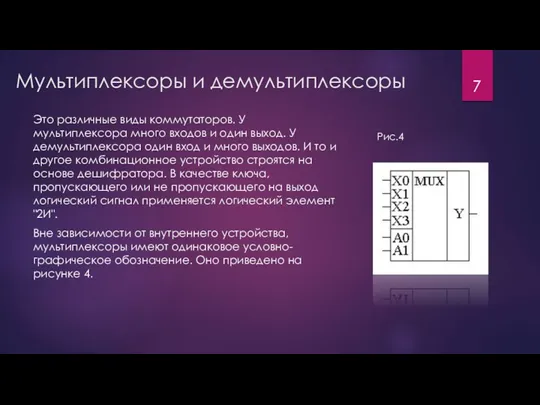

- 7. Мультиплексоры и демультиплексоры Это различные виды коммутаторов. У мультиплексора много входов и один выход. У демультиплексора

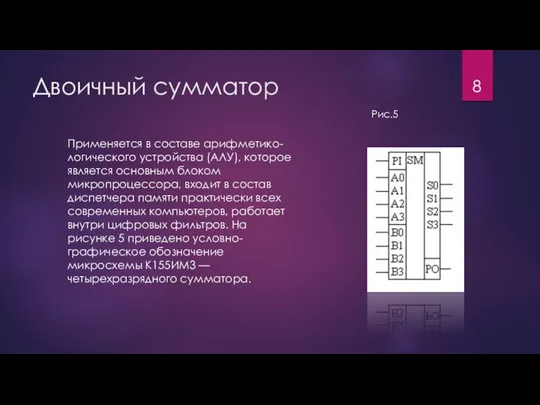

- 8. Двоичный сумматор Применяется в составе арифметико-логического устройства (АЛУ), которое является основным блоком микропроцессора, входит в состав

- 9. Структурно комбинационная схема (КС) может быть представлена как совокупность элементарных логических схем – логических элементов (ЛЭ).

- 10. Анализ комбинационной схемы Задача анализа комбинационной схемы состоит в определении статических и динамических свойств комбинационной схемы.

- 11. Синтез комбинационной схемы Задача синтеза комбинационной схемы заключается в построении из заданного набора логических элементов комбинационной

- 13. Скачать презентацию

Реальное и виртуальное в философии

Реальное и виртуальное в философии cb42fe644f33b9eb

cb42fe644f33b9eb Внутриутробные инфекции

Внутриутробные инфекции Отложенный перенос эмбрионов – новые перспективы

Отложенный перенос эмбрионов – новые перспективы Знакомство дошкольников с дорожными знаками.

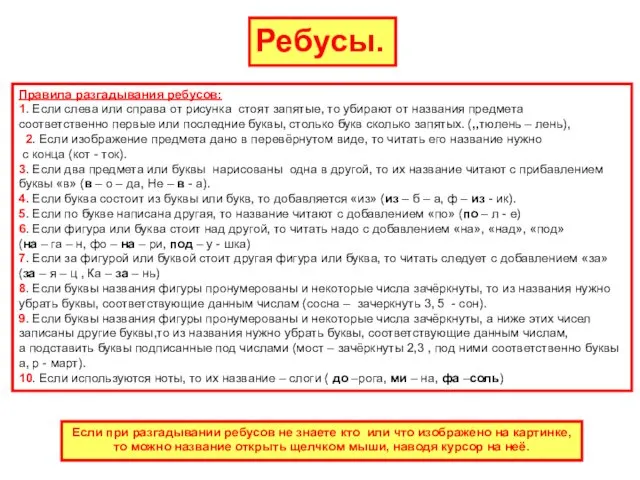

Знакомство дошкольников с дорожными знаками. Ребусы

Ребусы 0e0c7fd201832f92

0e0c7fd201832f92 Организация работы по предупреждению детского дорожно-транспортного травматизма в средней группе

Организация работы по предупреждению детского дорожно-транспортного травматизма в средней группе Презентация Особенности организации внеурочной деятельности при работе с детьми с повышенной мотивацией

Презентация Особенности организации внеурочной деятельности при работе с детьми с повышенной мотивацией Семиотический методологический подход к коммуникации

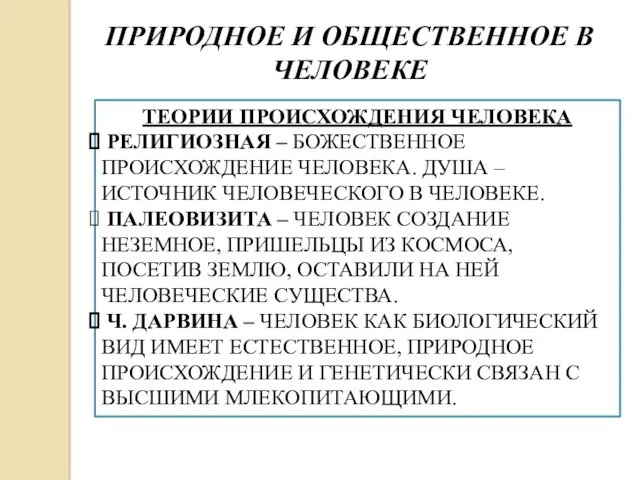

Семиотический методологический подход к коммуникации Природное и общественное в человеке. Теории происхождения человека

Природное и общественное в человеке. Теории происхождения человека дидактическая играМой город

дидактическая играМой город Реализация и мониторинг внеурочной деятельности (презентация)

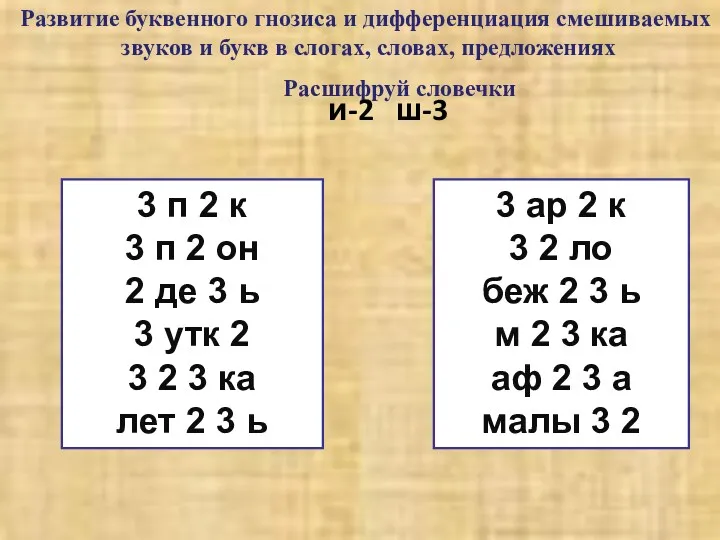

Реализация и мониторинг внеурочной деятельности (презентация) Презентация к ЦОР. Тема:Развитие буквенного гнозиса и дифференциация смешиваемых звуков и букв в слогах, словах.

Презентация к ЦОР. Тема:Развитие буквенного гнозиса и дифференциация смешиваемых звуков и букв в слогах, словах. Тепловые явления. Методы вычисления количества выделенной или поглощенной теплоты

Тепловые явления. Методы вычисления количества выделенной или поглощенной теплоты Правоохранительные органы Российской Федерации

Правоохранительные органы Российской Федерации Приёмы сжатия текста

Приёмы сжатия текста Отын энергетикалық кешен. Кешеннің ерекшелігі мен маңызы. Мұнай және газ өнеркәсібі. Көмір өнеркәсібі. Электр қуаты

Отын энергетикалық кешен. Кешеннің ерекшелігі мен маңызы. Мұнай және газ өнеркәсібі. Көмір өнеркәсібі. Электр қуаты Презентация Периодическая система химических элементов Д.И. Менделеева

Презентация Периодическая система химических элементов Д.И. Менделеева ИМИДЖ УЧИТЕЛЯ. Диск

ИМИДЖ УЧИТЕЛЯ. Диск Что такое световозвращатели. Для школ

Что такое световозвращатели. Для школ Основная документация педагога-психолога ДОУ

Основная документация педагога-психолога ДОУ Екологічне виховання молодших школярів на уроках природознавства та української мови

Екологічне виховання молодших школярів на уроках природознавства та української мови Топонимика и микротопонимика городского округа города Шахунья

Топонимика и микротопонимика городского округа города Шахунья Научные революции в естествознании и формирование научной картины мира

Научные революции в естествознании и формирование научной картины мира Система счисления древней Руси

Система счисления древней Руси Атлас педагогических идей

Атлас педагогических идей Методы решения иррациональных уравнений

Методы решения иррациональных уравнений