Содержание

- 2. ASSEMBLEUR Un système travaillant sur une architecture à CPU peut très souvent être découpé en couche.

- 3. ASSEMBLEUR Observons en quelques chiffres, la répartition des marchés des systèmes d’exploitation sur quelques un des

- 4. ASSEMBLEUR Vous aurez un enseignement dédié aux systèmes d’exploitation en 2A. Cet enseignement sera assuré par

- 5. ASSEMBLEUR Malheureusement, développement bas niveau ne veut pas dire développement simple. Un ingénieur travaillant dans ce

- 6. ASSEMBLEUR Effectuons quelques rappels sur une chaîne de compilation C (C toolChain ou C toolSuite). Les

- 7. ASSEMBLEUR Cet enseignement s’appuie sur les compétences enseignées dans les enseignements ‘’Outils de Développement Logiciel’’ et

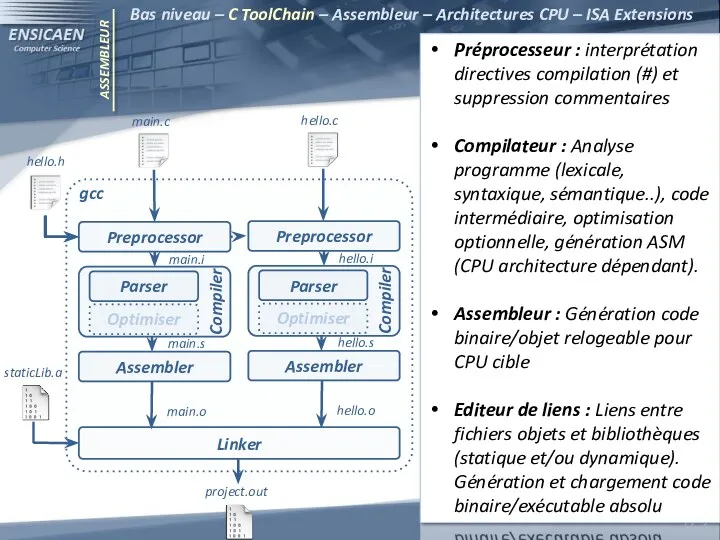

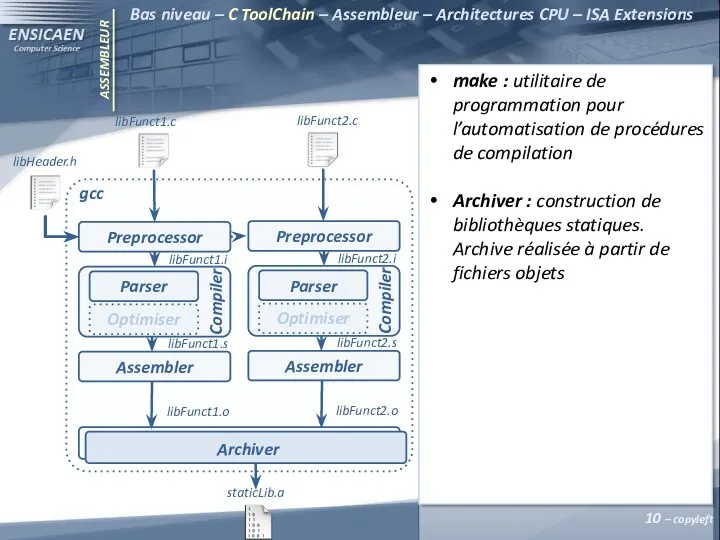

- 8. ASSEMBLEUR Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions – copyleft

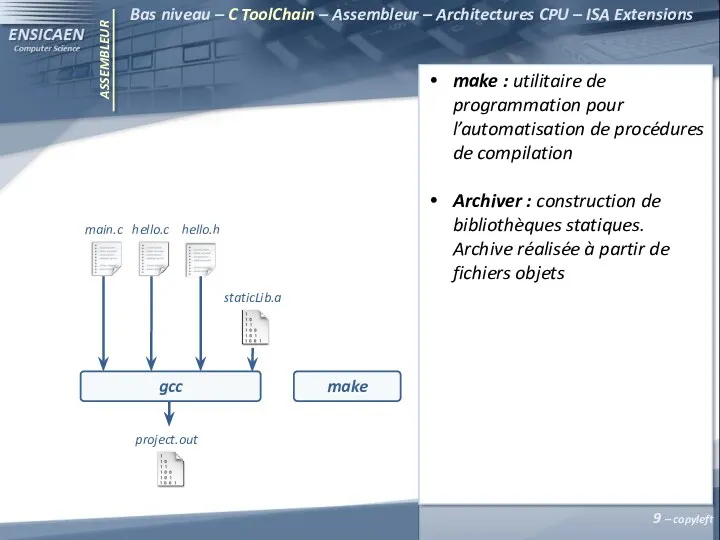

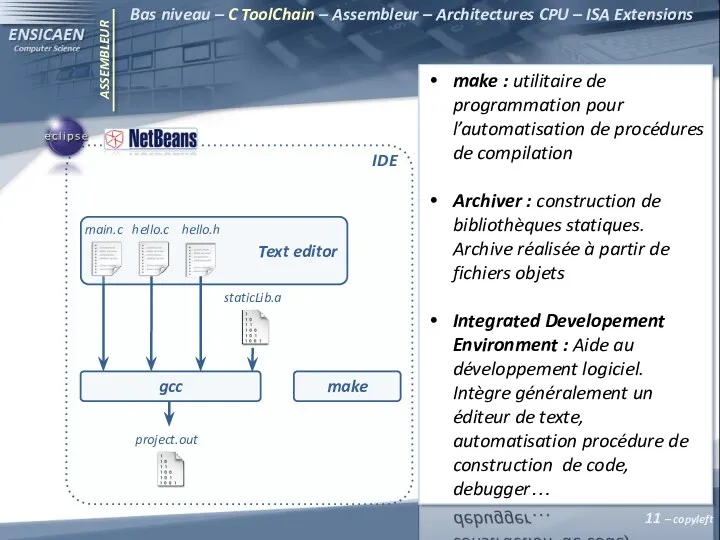

- 9. ASSEMBLEUR Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions – copyleft

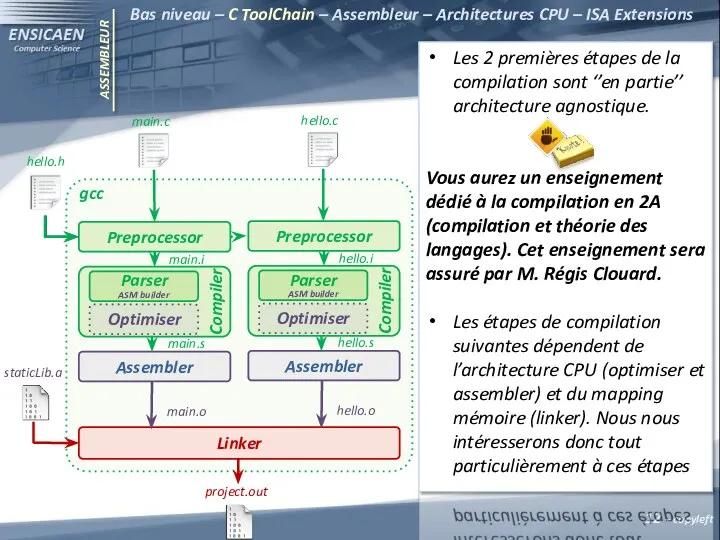

- 10. ASSEMBLEUR Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions – copyleft

- 11. ASSEMBLEUR Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions – copyleft

- 12. ASSEMBLEUR Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions – copyleft

- 13. ASSEMBLEUR Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions – copyleft

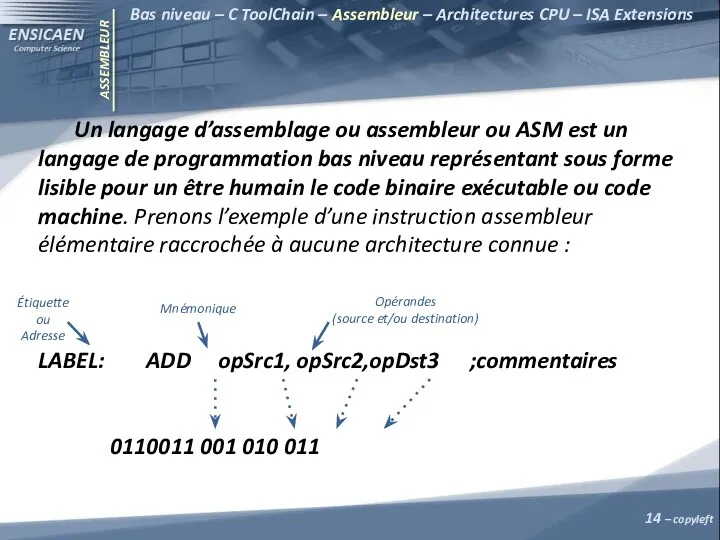

- 14. ASSEMBLEUR Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions Un langage

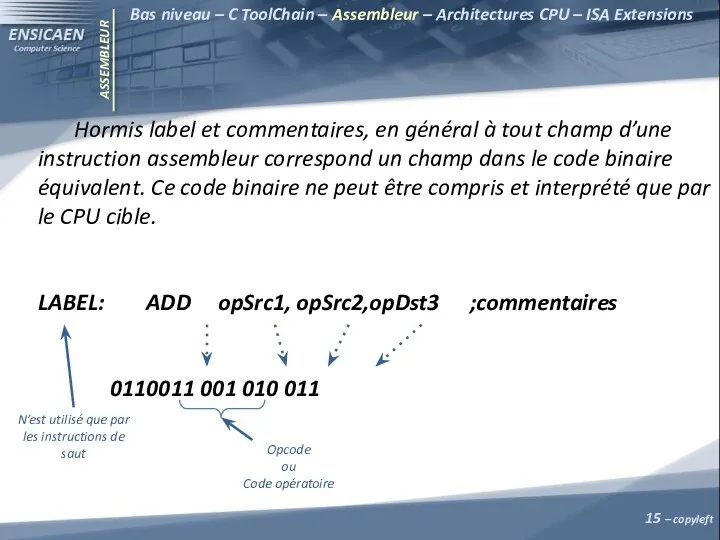

- 15. ASSEMBLEUR Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions Hormis label

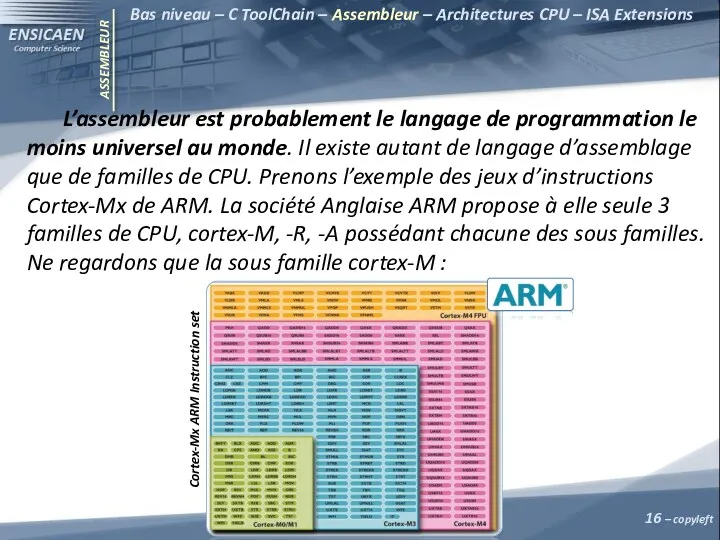

- 16. ASSEMBLEUR Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions L’assembleur est

- 17. ASSEMBLEUR Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions Observons les

- 18. ASSEMBLEUR Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions Tout CPU

- 19. ASSEMBLEUR Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions Contrôle programme

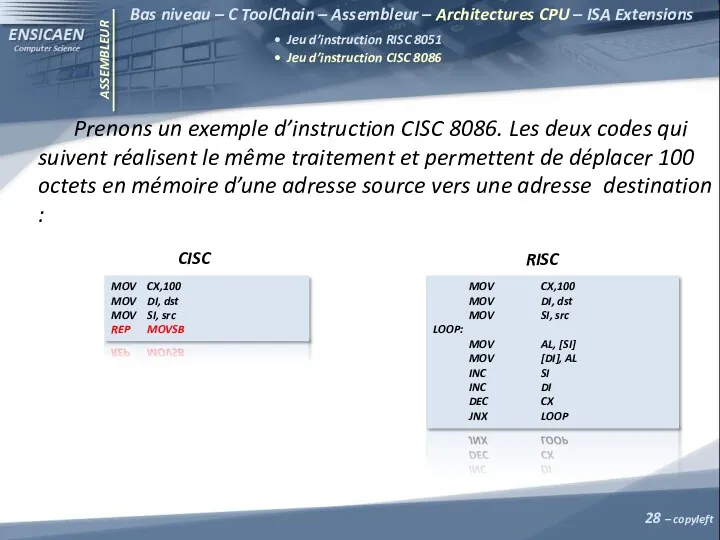

- 20. ASSEMBLEUR Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions • Jeu

- 21. ASSEMBLEUR Avantages architecture CISC : Empreinte mémoire programme faible, donc plus d’instructions contenues en cache. Néanmoins

- 22. ASSEMBLEUR Inconvénients architecture RISC : Empreinte mémoire programme élevée, donc moins d’instructions contenues en cache et

- 23. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

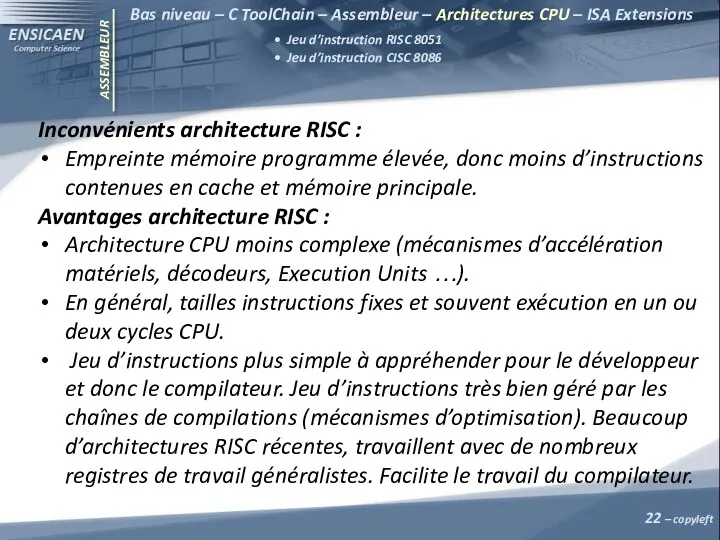

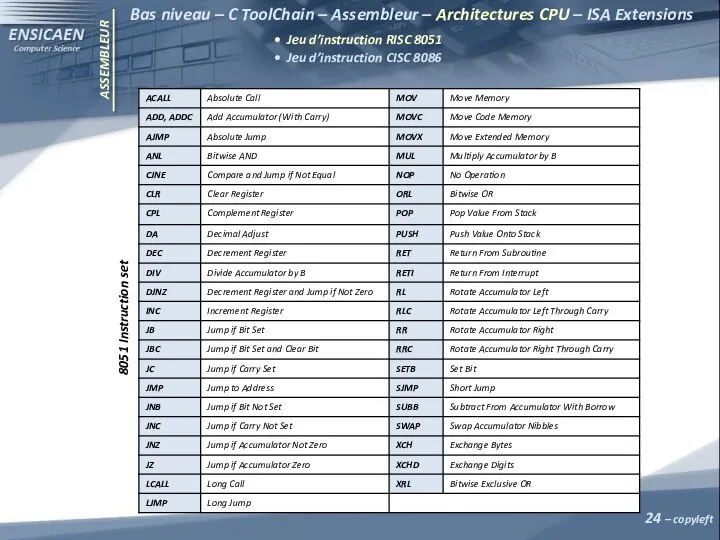

- 24. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

- 25. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

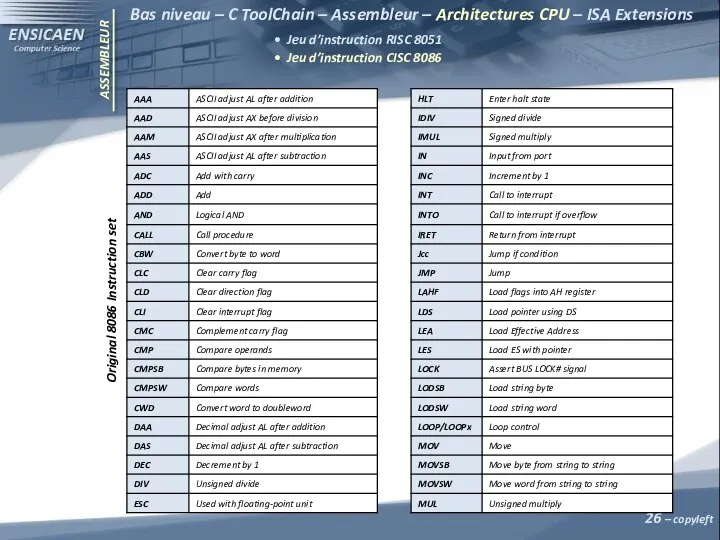

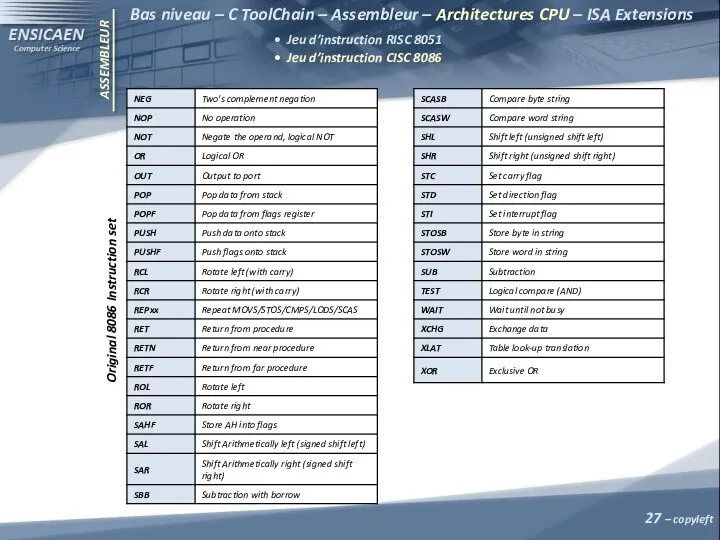

- 26. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

- 27. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

- 28. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

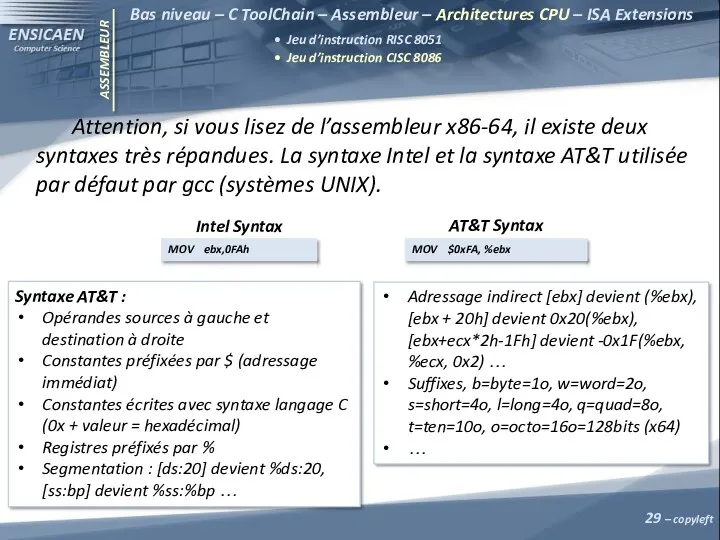

- 29. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

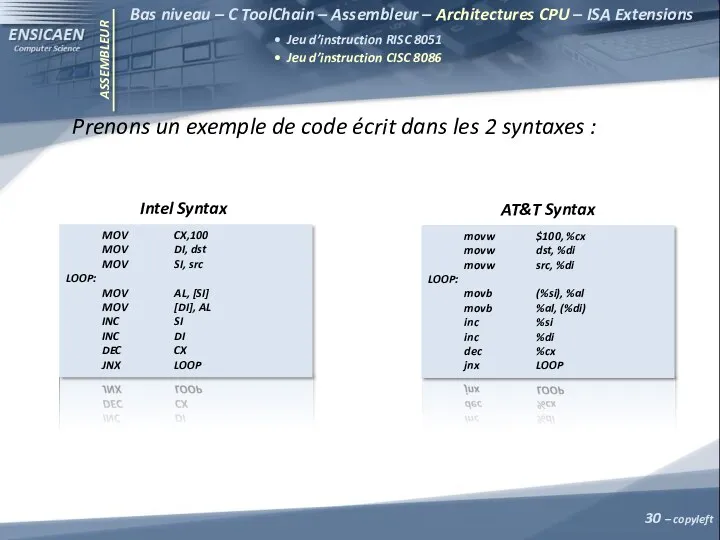

- 30. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

- 31. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

- 32. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

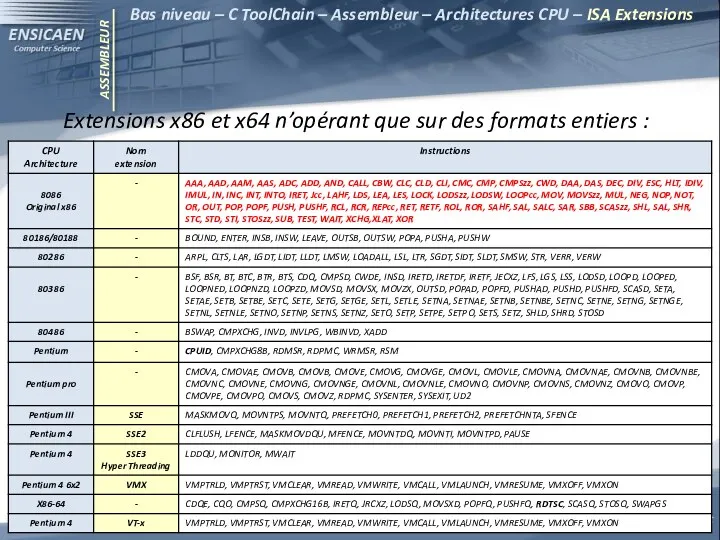

- 33. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

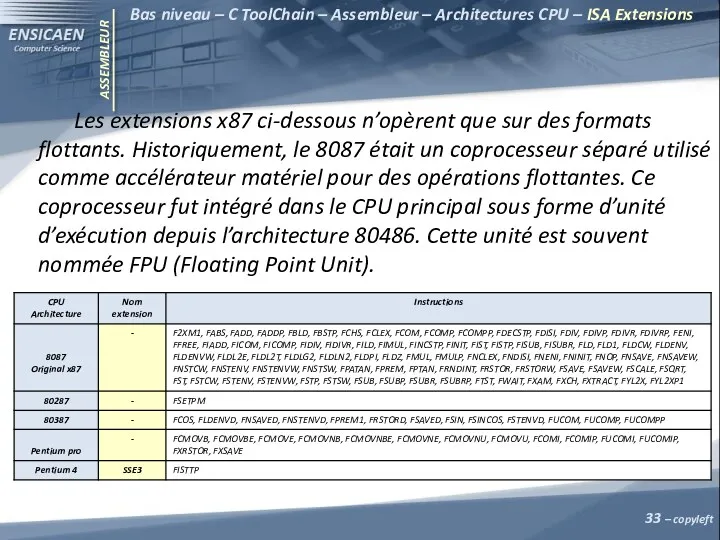

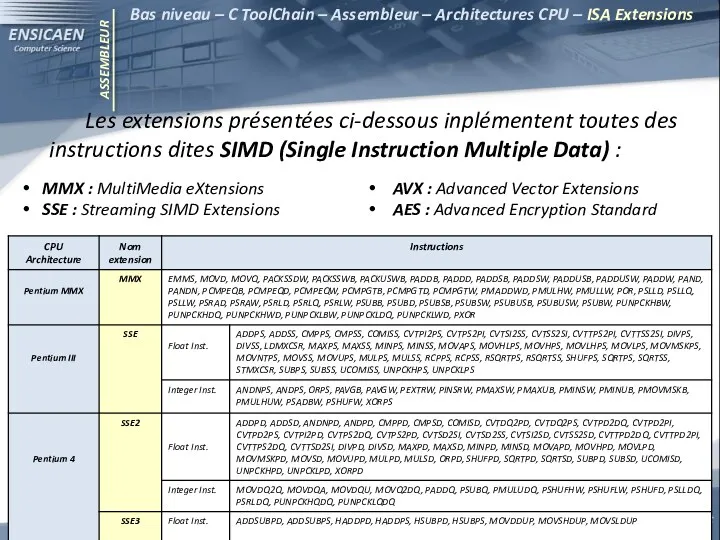

- 34. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

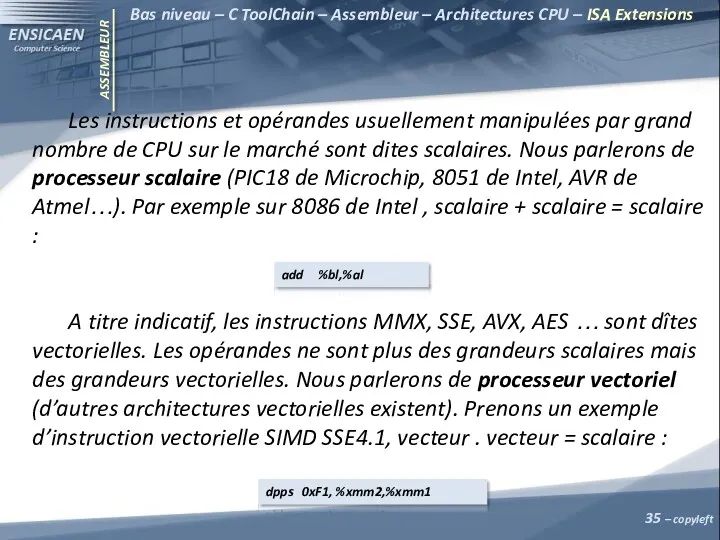

- 35. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

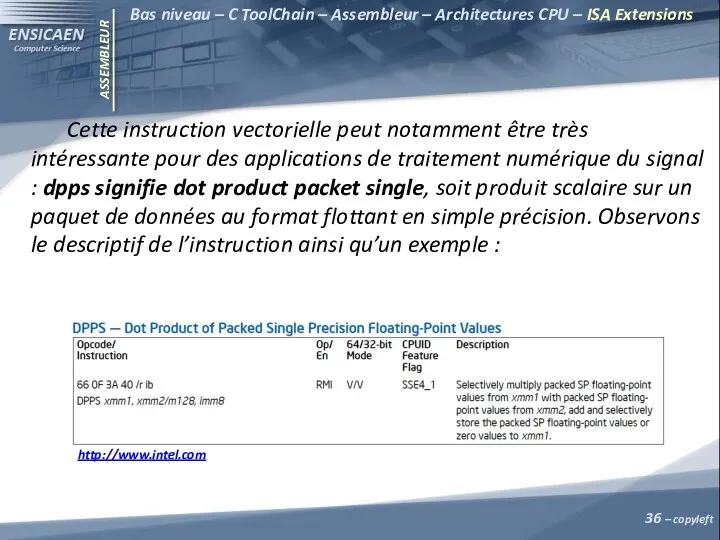

- 36. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

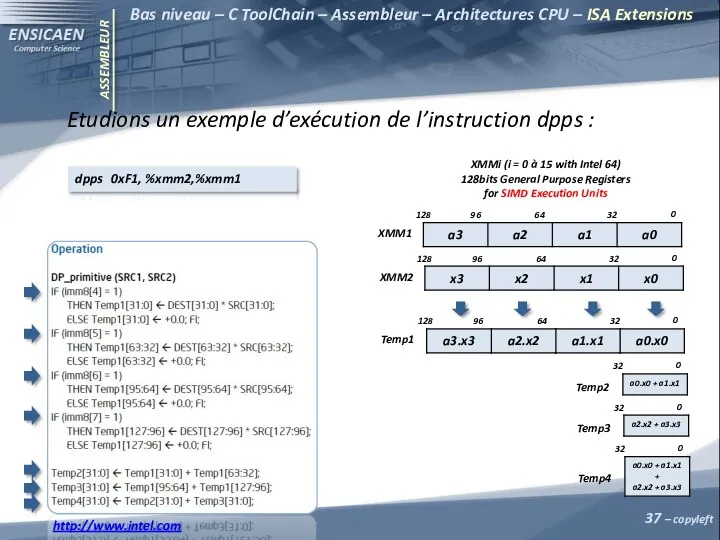

- 37. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

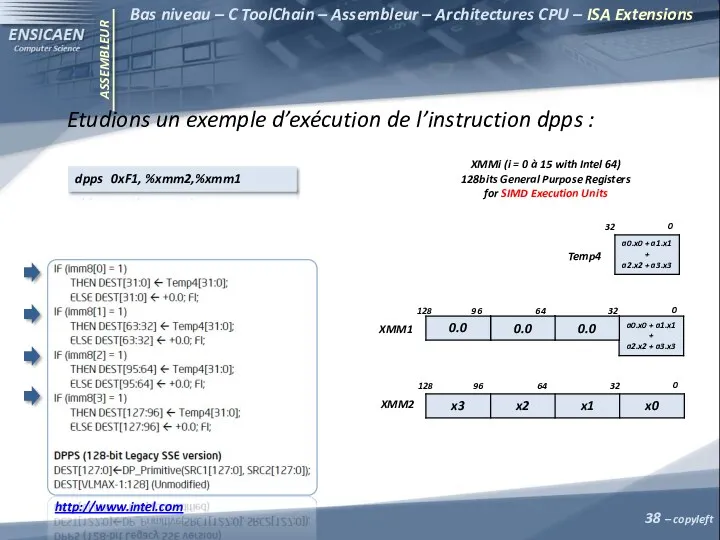

- 38. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

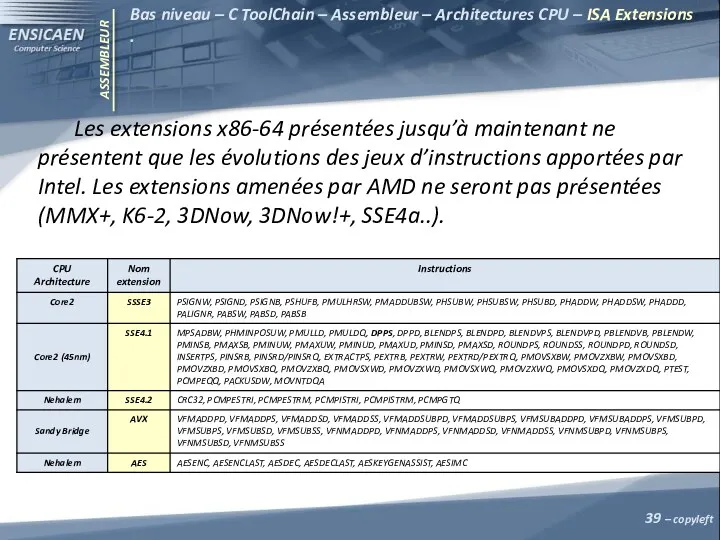

- 39. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

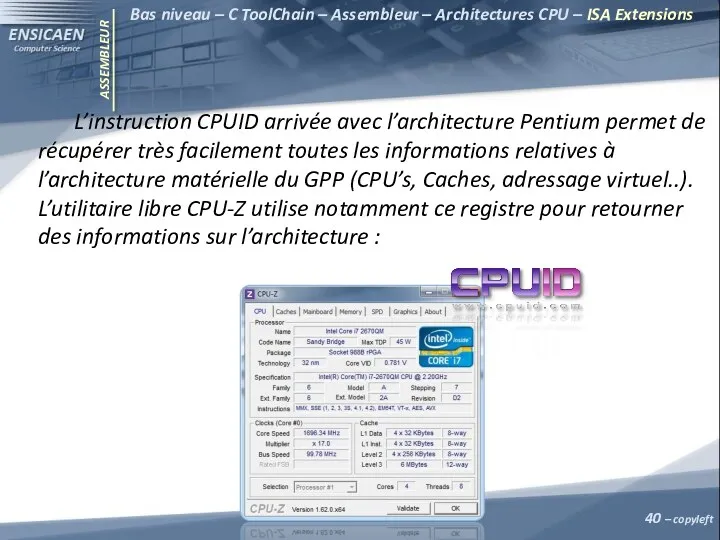

- 40. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

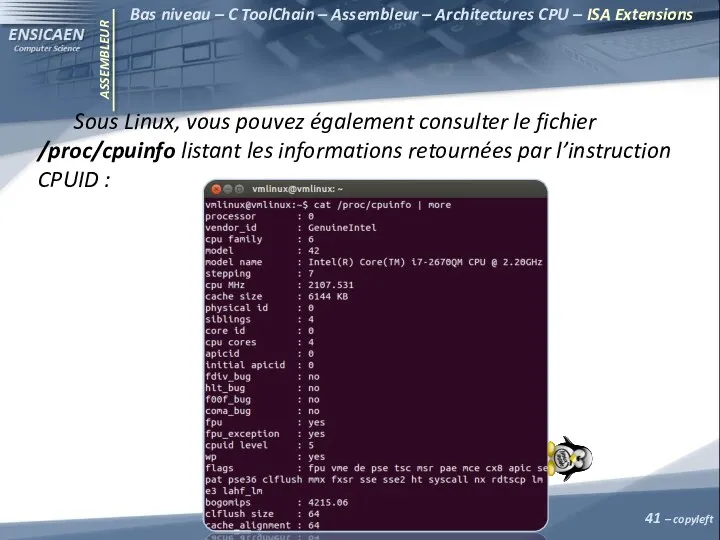

- 41. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

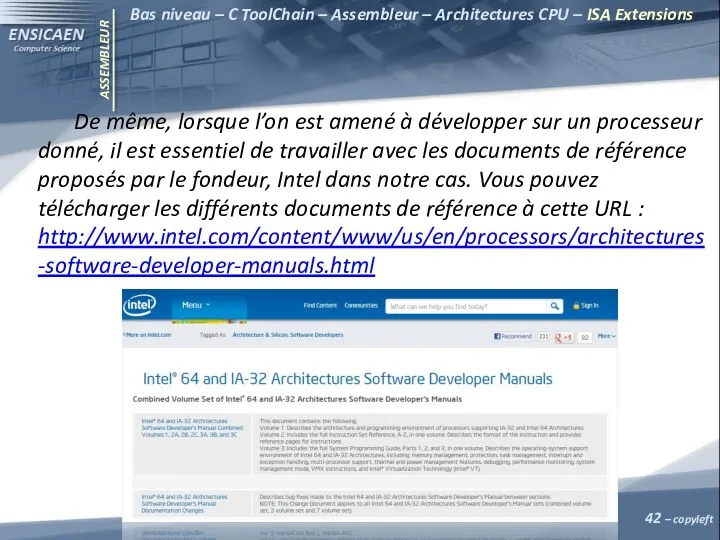

- 42. ASSEMBLEUR – copyleft Bas niveau – C ToolChain – Assembleur – Architectures CPU – ISA Extensions

- 44. Скачать презентацию

Презентация Мой поселок

Презентация Мой поселок Природное и общественное в человеке. Теории происхождения человека

Природное и общественное в человеке. Теории происхождения человека Дипломчики для первоклассников

Дипломчики для первоклассников Пусть наши дети будут всегда здоровы и счастливы!

Пусть наши дети будут всегда здоровы и счастливы! В гости к музыке

В гости к музыке Методика обследования хирургических больных. Операция, предоперационный и послеоперационный период

Методика обследования хирургических больных. Операция, предоперационный и послеоперационный период Награды военных лет

Награды военных лет Туристическая поездка в Горячий ключ

Туристическая поездка в Горячий ключ ПрезентацияФрукты

ПрезентацияФрукты Тайна имени Илья

Тайна имени Илья Родительское собрание первые дни ребёнка в школе

Родительское собрание первые дни ребёнка в школе Почитание преподобного Сергия Радонежского в истории моего города

Почитание преподобного Сергия Радонежского в истории моего города Понятие информационные систем. История развития баз данных

Понятие информационные систем. История развития баз данных Информационные средства обучения географии

Информационные средства обучения географии Мои презентации

Мои презентации Окна Роста. Агитационные плакаты

Окна Роста. Агитационные плакаты Языковые трудности при изучении иностранного языка

Языковые трудности при изучении иностранного языка Многоэтажные здания. Общая характеристика многоэтажных зданий

Многоэтажные здания. Общая характеристика многоэтажных зданий Классный час Утилизация батареек

Классный час Утилизация батареек Комплекс устройств и схема электроснабжения железных дорог

Комплекс устройств и схема электроснабжения железных дорог Теплотехника и тепловые установки

Теплотехника и тепловые установки Культура ХХ-ХХІ століття

Культура ХХ-ХХІ століття Химико-технологическая система, ее состав и структура

Химико-технологическая система, ее состав и структура Металлургический комплекс. Совокупность предприятий по добыче руд и изготовлению металлов

Металлургический комплекс. Совокупность предприятий по добыче руд и изготовлению металлов Лучшие практики зелёных школ

Лучшие практики зелёных школ Интерпретация ГИС в нефтяных и газовых скважинах

Интерпретация ГИС в нефтяных и газовых скважинах Потеря электроэнергии в верхнем строении железнодорожного пути

Потеря электроэнергии в верхнем строении железнодорожного пути Социальные аспекты экономического развития мира. (Тема 4)

Социальные аспекты экономического развития мира. (Тема 4)