Содержание

- 2. Модуль центрального процессора TMS320F28x N (бит ST05) – флаг знака. N установлен, если результат операции –

- 3. Модуль центрального процессора TMS320F28x C (бит ST03) – флаг переноса. Этот флаг показывает, когда сложение, инкремент

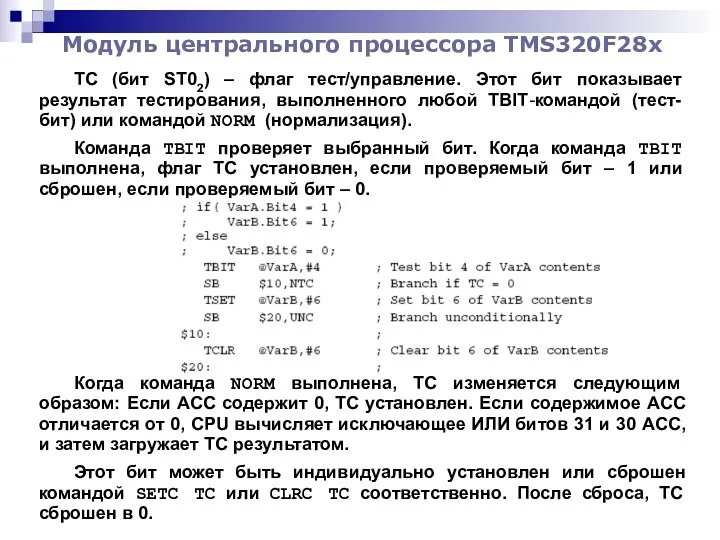

- 4. Модуль центрального процессора TMS320F28x TC (бит ST02) – флаг тест/управление. Этот бит показывает результат тестирования, выполненного

- 5. Модуль центрального процессора TMS320F28x OVM (бит ST01) – флаг режима переполнения. Когда ACC принимает результат сложения

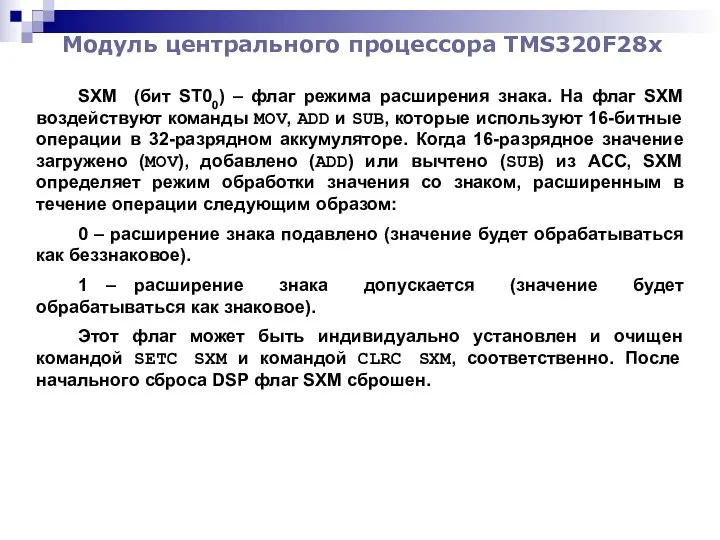

- 6. Модуль центрального процессора TMS320F28x SXM (бит ST00) – флаг режима расширения знака. На флаг SXM воздействуют

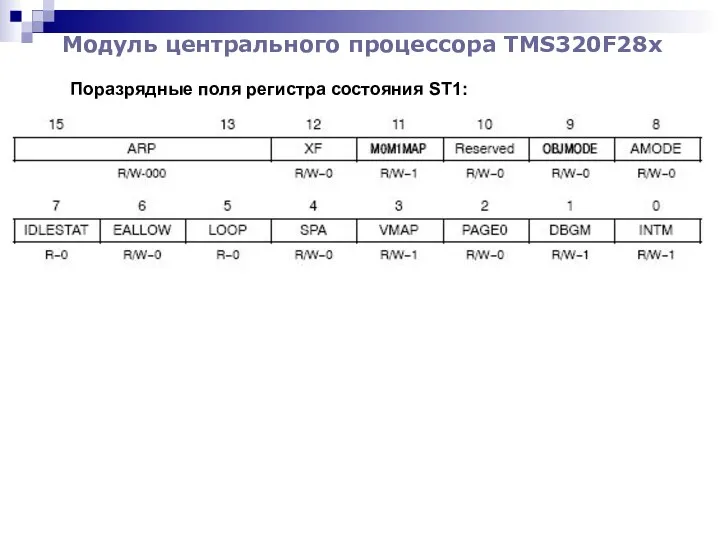

- 7. Модуль центрального процессора TMS320F28x Поразрядные поля регистра состояния ST1:

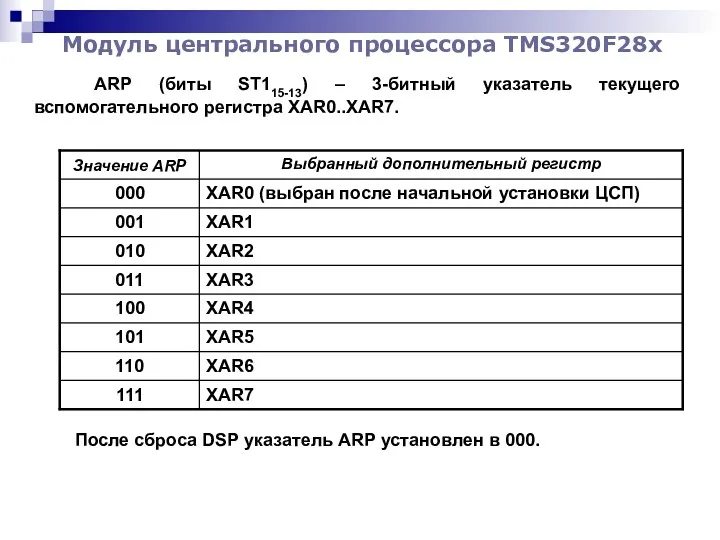

- 8. Модуль центрального процессора TMS320F28x ARP (биты ST115-13) – 3-битный указатель текущего вспомогательного регистра XAR0..XAR7. После сброса

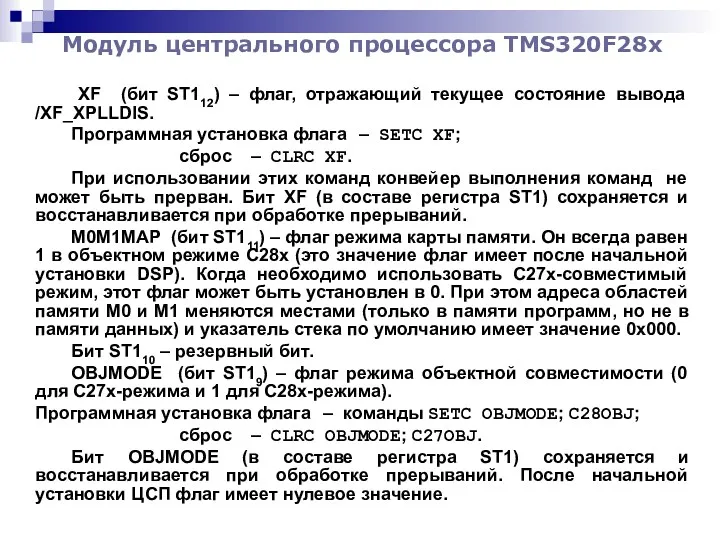

- 9. Модуль центрального процессора TMS320F28x XF (бит ST112) – флаг, отражающий текущее состояние вывода /XF_XPLLDIS. Программная установка

- 10. Модуль центрального процессора TMS320F28x AMODE (бит ST18) – флаг режима адресации. Этот бит, в сочетании с

- 11. Модуль центрального процессора TMS320F28x EALLOW (бит ST16) – этот флаг после установки разрешает доступ к эмуляционным

- 12. Модуль центрального процессора TMS320F28x SPA (бит ST14) – бит выравнивания указателя стека. Этот флаг показывает, выполнял

- 13. Модуль центрального процессора TMS320F28x VMAP (бит ST13) – бит карты векторов прерываний. VMAP определяет, где в

- 14. Модуль центрального процессора TMS320F28x PAGE0 (бит ST12) – бит конфигурации режима адресации PAGE0. Этот бит определяет

- 15. Модуль центрального процессора TMS320F28x DBGM (бит ST11) – бит маскирования разрешения отладки. Если флаг DBGM установлен,

- 16. Модуль центрального процессора TMS320F28x INTM (бит ST10) – бит общего маскирования прерываний. Этот бит глобально разрешает

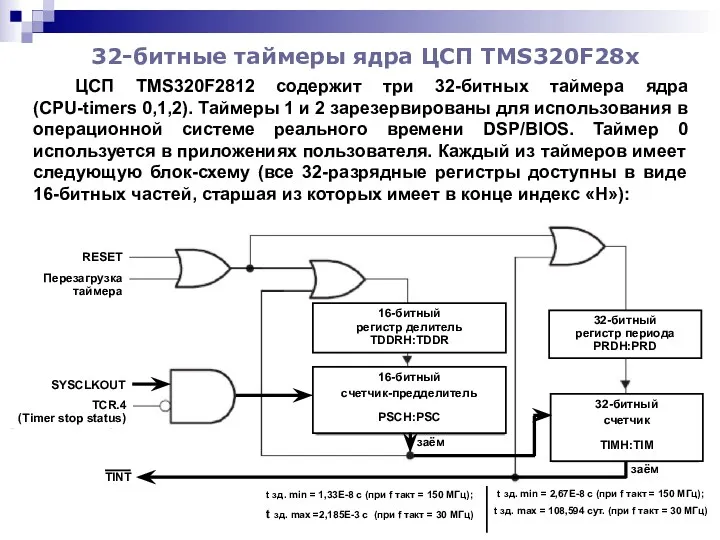

- 17. 32-битные таймеры ядра ЦСП TMS320F28x ЦСП TMS320F2812 содержит три 32-битных таймера ядра (CPU-timers 0,1,2). Таймеры 1

- 18. 32-битные таймеры ядра ЦСП TMS320F28x Каждый таймер тактируется системной частотой SYSCLKOUT после того, как в соответствующем

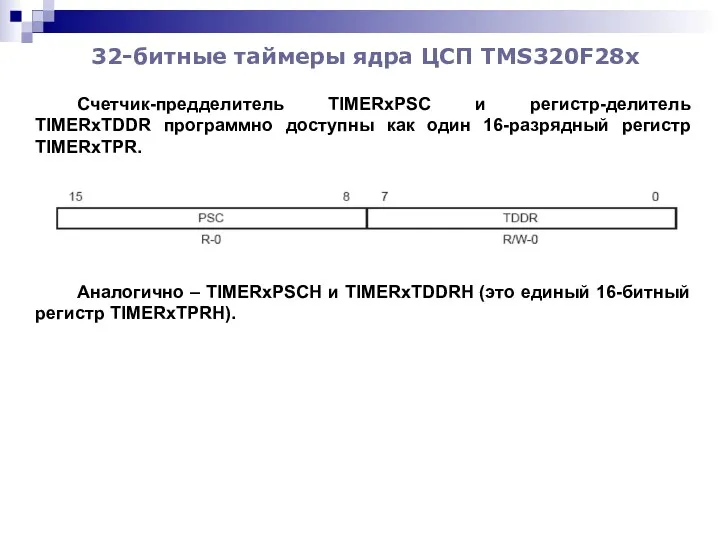

- 19. 32-битные таймеры ядра ЦСП TMS320F28x Счетчик-предделитель TIMERxPSC и регистр-делитель TIMERxTDDR программно доступны как один 16-разрядный регистр

- 20. Система прерываний DSP TMS320F2812 Прерывания – это программно- или аппаратно-управляемые сигналы, которые заставляют CPU приостанавливать текущее

- 21. Система прерываний DSP TMS320F2812 Прерывания выполняются в 4-х основных фазах: Прием запроса прерывания. Принятие прерывания к

- 22. Система прерываний DSP TMS320F2812

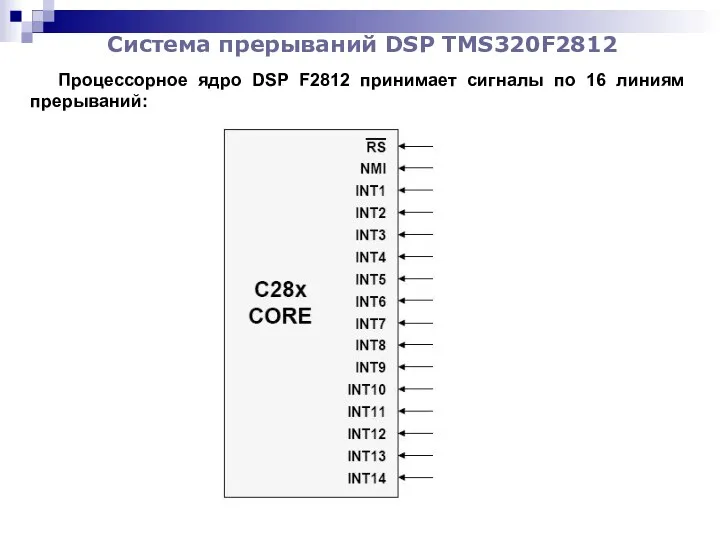

- 23. Система прерываний DSP TMS320F2812 Процессорное ядро DSP F2812 принимает сигналы по 16 линиям прерываний:

- 24. Система прерываний DSP TMS320F2812 Источники прерываний в DSP F2812:

- 26. Скачать презентацию

Рациональное питание

Рациональное питание Презентация История жеательной резинки

Презентация История жеательной резинки Правление Ивана IV Грозного (1533-1584)

Правление Ивана IV Грозного (1533-1584) Визитная карточка Д/С № 207

Визитная карточка Д/С № 207 Arduino. Проект: Beyond reason

Arduino. Проект: Beyond reason Спирты

Спирты Родительское собрание

Родительское собрание Большие социальные группы (Тема 4)

Большие социальные группы (Тема 4) Обобщенная структурная схема системы передачи дискретных сообщений (передачи данных)

Обобщенная структурная схема системы передачи дискретных сообщений (передачи данных) Мы делили апельсин. Пальчиковая гимнастика.

Мы делили апельсин. Пальчиковая гимнастика. Опыт проведения православного фестиваля детского художественного творчества Светлая Пасха

Опыт проведения православного фестиваля детского художественного творчества Светлая Пасха Эволюция звезд

Эволюция звезд Дүниежүзі елдерін даму деңгейі бойынша жіктеу

Дүниежүзі елдерін даму деңгейі бойынша жіктеу Правила школьной жизни

Правила школьной жизни Учет денежных средств в иностранной валюте

Учет денежных средств в иностранной валюте Возбуждение уголовного дела

Возбуждение уголовного дела О молитве

О молитве Улицы города Владимир, названные в честь владимирцев - героев Великой Отечественной Войны

Улицы города Владимир, названные в честь владимирцев - героев Великой Отечественной Войны Материал по краеведению Республики Адыгея

Материал по краеведению Республики Адыгея Теория и история потребительской кооперации

Теория и история потребительской кооперации Adding forces

Adding forces проект по теме: Дидактическая игра как средство развития словаря у детей младшего дошкольного возраста

проект по теме: Дидактическая игра как средство развития словаря у детей младшего дошкольного возраста Презентация к занятию Вежливость и доброта

Презентация к занятию Вежливость и доброта Общие положения об обязательствах

Общие положения об обязательствах СССР в годы перестройки

СССР в годы перестройки восприятие мира

восприятие мира Визитная карточка проекта НАШИ ПРЕЗЕНТАЦИИ.

Визитная карточка проекта НАШИ ПРЕЗЕНТАЦИИ. Опасности в Интернете

Опасности в Интернете