Содержание

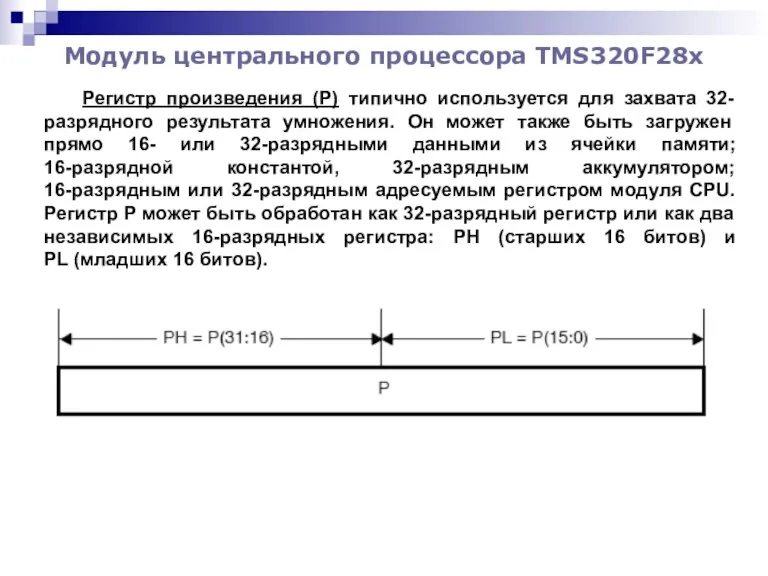

- 2. Модуль центрального процессора TMS320F28x Регистр произведения (P) типично используется для захвата 32-разрядного результата умножения. Он может

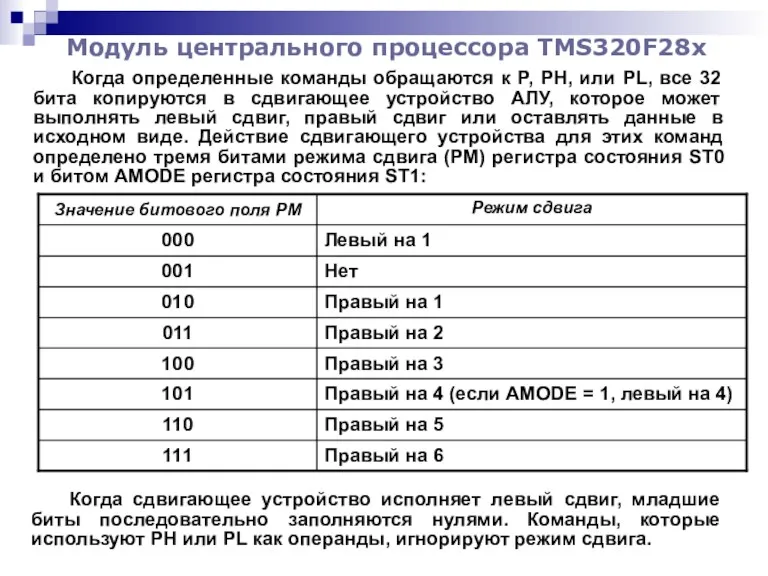

- 3. Модуль центрального процессора TMS320F28x Когда определенные команды обращаются к P, PH, или PL, все 32 бита

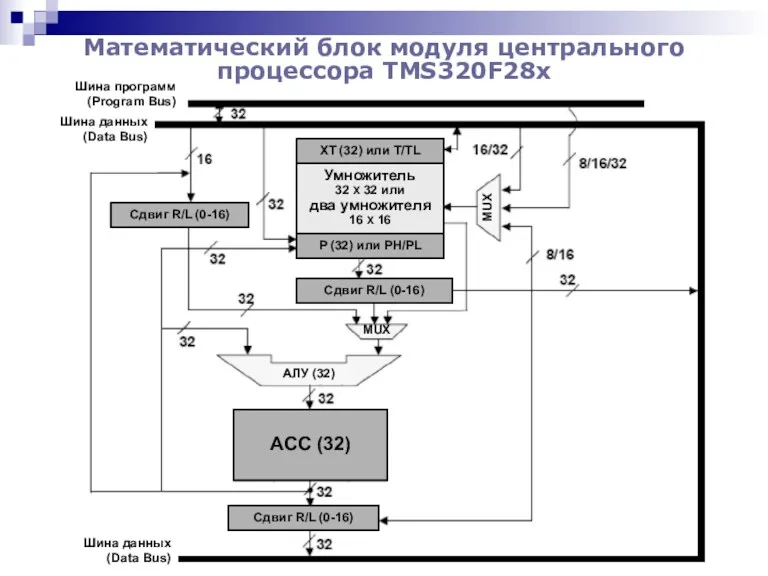

- 4. Математический блок модуля центрального процессора TMS320F28x

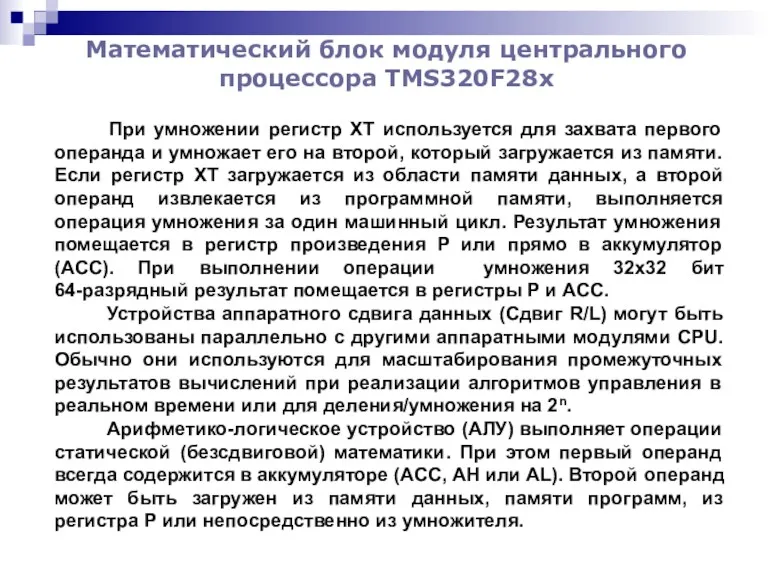

- 5. Математический блок модуля центрального процессора TMS320F28x При умножении регистр XT используется для захвата первого операнда и

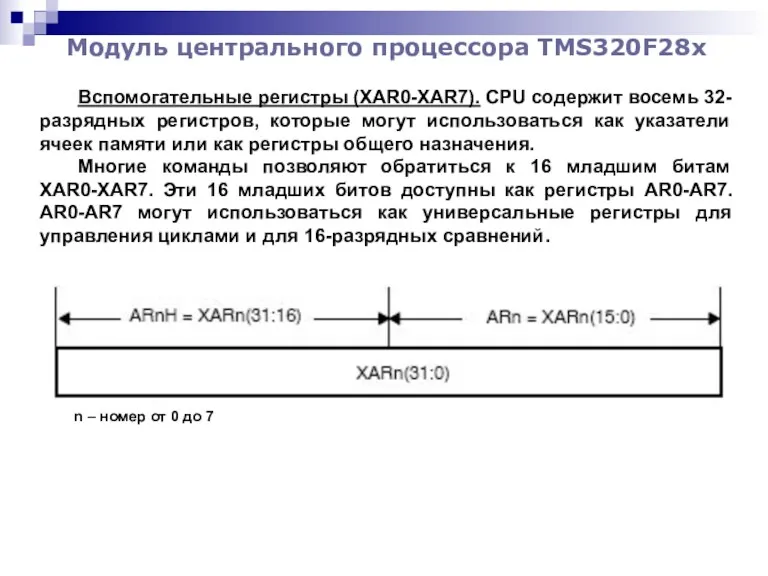

- 6. Модуль центрального процессора TMS320F28x Вспомогательные регистры (XAR0-XAR7). CPU содержит восемь 32-разрядных регистров, которые могут использоваться как

- 7. Модуль центрального процессора TMS320F28x При доступе AR0–AR7, старшие 16 битов регистра (обозначаемые как регистры AR0H–AR7H), могут

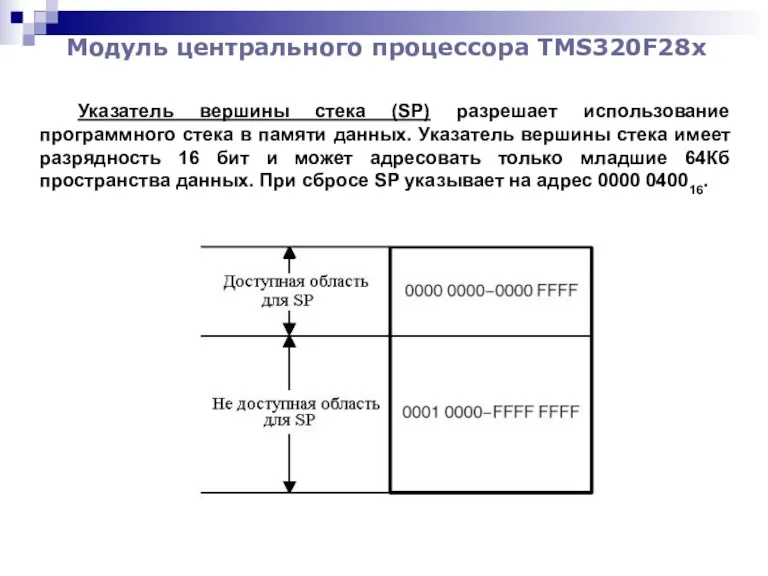

- 8. Модуль центрального процессора TMS320F28x Указатель вершины стека (SP) разрешает использование программного стека в памяти данных. Указатель

- 9. Модуль центрального процессора TMS320F28x Стек увеличивается по направлению от младших адресов к старшим. Указатель стека всегда

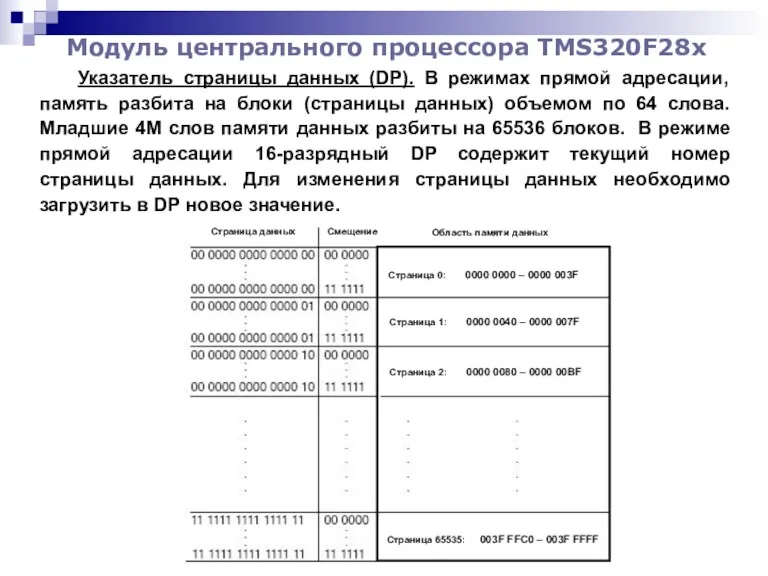

- 10. Модуль центрального процессора TMS320F28x Указатель страницы данных (DP). В режимах прямой адресации, память разбита на блоки

- 11. Блок адресации памяти данных модуля центрального процессора TMS320F28x Для доступа к произвольным областям памяти данных в

- 12. Шина программ (Program Bus) Шина данных (Data Bus) 6 младших бит из регистра инструкций Память данных

- 13. Блок адресации памяти данных модуля центрального процессора TMS320F28x В режиме прямой адресации 22-битный адрес доступа к

- 14. Блок адресации памяти данных модуля центрального процессора TMS320F28x В режиме косвенной адресации используются восемь 32-разрядных регистров

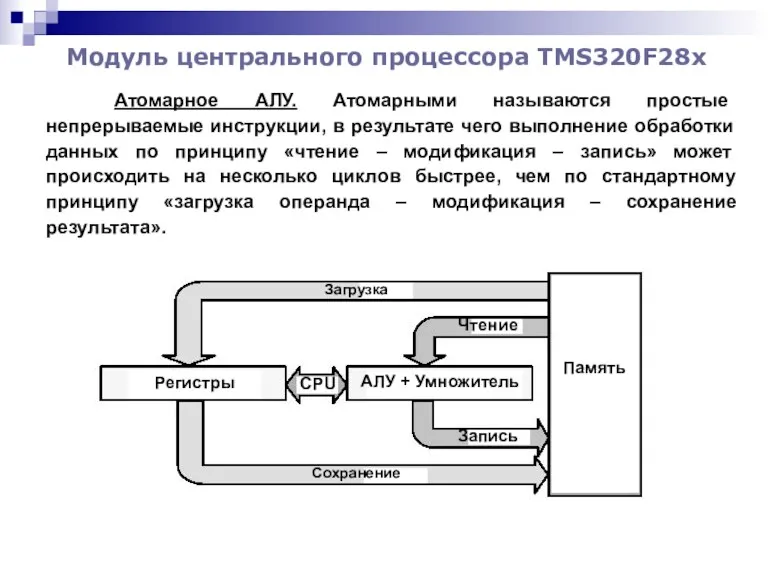

- 15. Модуль центрального процессора TMS320F28x Атомарное АЛУ. Атомарными называются простые непрерываемые инструкции, в результате чего выполнение обработки

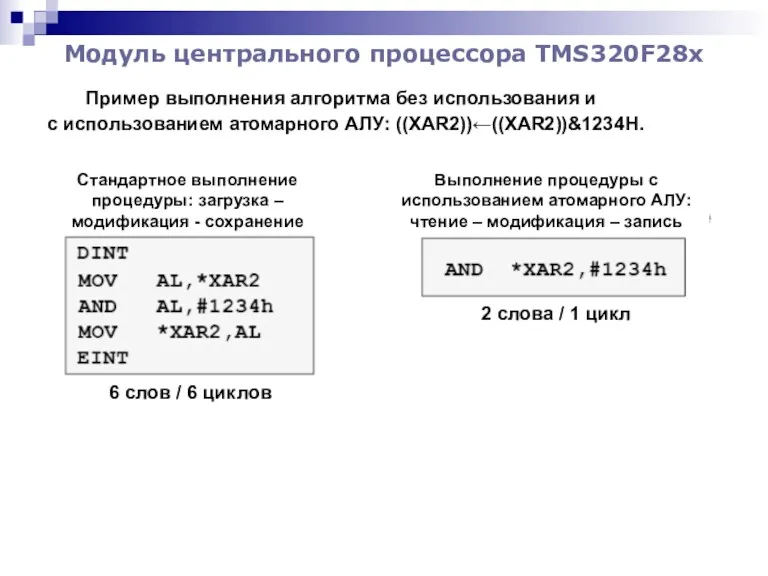

- 16. Модуль центрального процессора TMS320F28x Стандартное выполнение процедуры: загрузка – модификация - сохранение 6 слов / 6

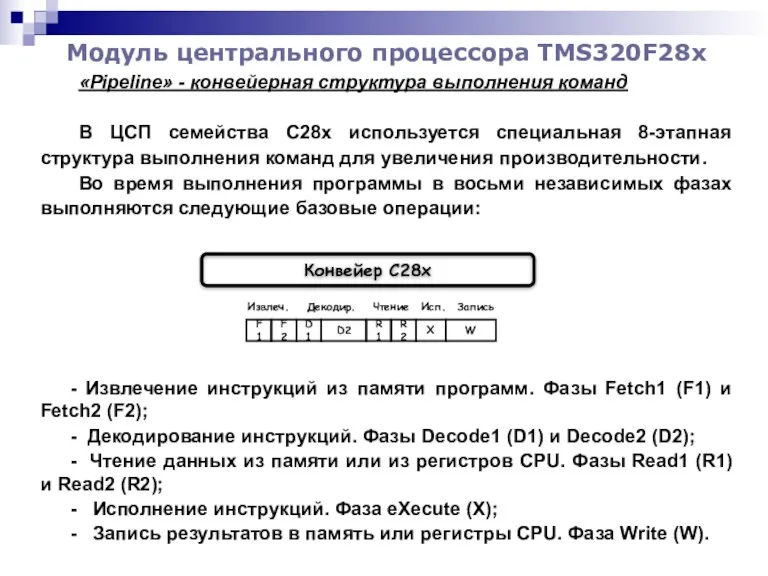

- 17. Модуль центрального процессора TMS320F28x «Pipeline» - конвейерная структура выполнения команд В ЦСП семейства С28x используется специальная

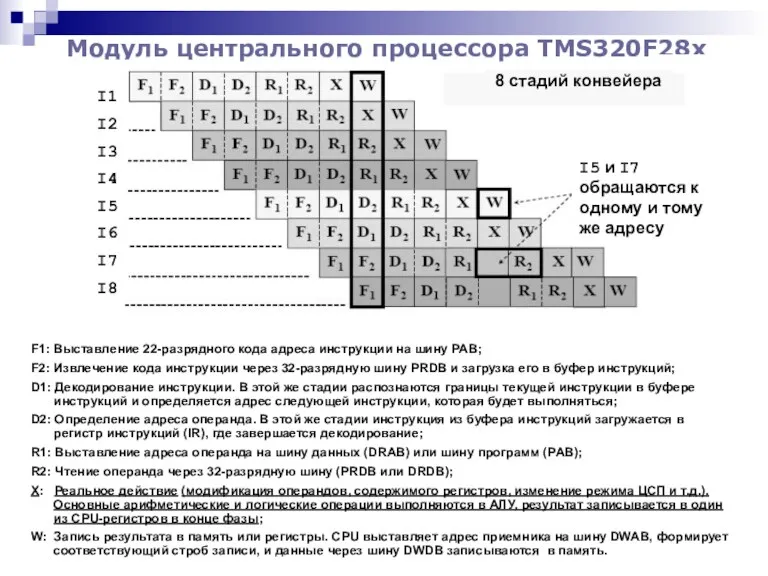

- 18. Модуль центрального процессора TMS320F28x F1: Instruction Address F2: Instruction Content D1: Decode Instruction D2: Resolve Operand

- 19. Модуль центрального процессора TMS320F28x X Циклы

- 21. Скачать презентацию

Понятие, роль, масштаб мирового финансового рынка

Понятие, роль, масштаб мирового финансового рынка Работа в группах в условиях малочисленного класса

Работа в группах в условиях малочисленного класса Урок географии в 5 классе в рамках ФГОС От плоской Земли к земному шару.

Урок географии в 5 классе в рамках ФГОС От плоской Земли к земному шару. Сюмсинский дом детского творчества

Сюмсинский дом детского творчества Тренажер по русскому языку

Тренажер по русскому языку Сочинение по картине Ивана Ивановича Шишкина Утро в сосновом лесу

Сочинение по картине Ивана Ивановича Шишкина Утро в сосновом лесу Лесной житель - белка

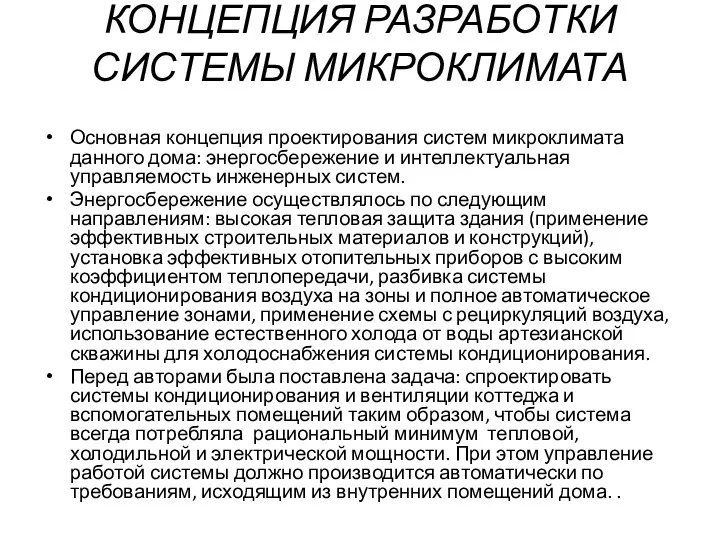

Лесной житель - белка Концепция разработки системы микроклимата

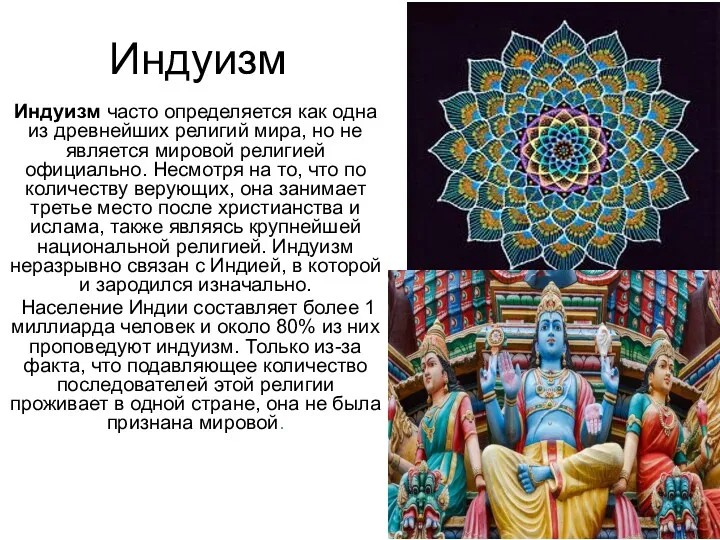

Концепция разработки системы микроклимата Индуизм. Направления индуизма

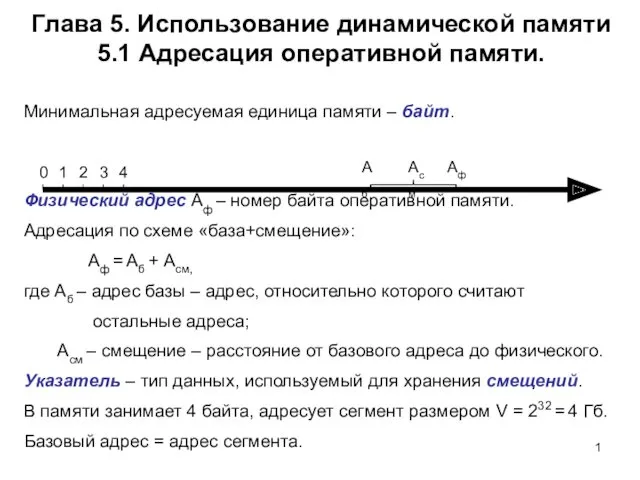

Индуизм. Направления индуизма Использование динамической памяти

Использование динамической памяти Биография Максима Горького

Биография Максима Горького Русь во времена политической раздробленности

Русь во времена политической раздробленности Внеурочная работа по предметам естественно-математического цикла

Внеурочная работа по предметам естественно-математического цикла Презентация Советы родителям

Презентация Советы родителям Объекты в JavaScript. Иерархия объектов. (Лекция 7)

Объекты в JavaScript. Иерархия объектов. (Лекция 7) Владимир Иванович Даль

Владимир Иванович Даль CoDeSys CNC functionality

CoDeSys CNC functionality Специальность 44.02.02 Преподавание в начальных классах

Специальность 44.02.02 Преподавание в начальных классах Семь принципов богоугодного брака

Семь принципов богоугодного брака Теория надежности. Характеристика научно-технического направления, основные понятия, термины и определения. (Лекция 1)

Теория надежности. Характеристика научно-технического направления, основные понятия, термины и определения. (Лекция 1) Близость оперы Жизнь за царя М. И. Глинки и оперы Князь Игорь А. П. Бородина

Близость оперы Жизнь за царя М. И. Глинки и оперы Князь Игорь А. П. Бородина Презентация к логопедическому занятию Зима

Презентация к логопедическому занятию Зима апр2021презентация Сапрунова

апр2021презентация Сапрунова Презентация Жемчужина Каспия.

Презентация Жемчужина Каспия. Ложный круп

Ложный круп Презентация 5

Презентация 5 Возрастные особенности развития личности

Возрастные особенности развития личности физминутка для глаз

физминутка для глаз