Содержание

- 2. OUTLINE 1. Microelectronics: Present status and challenges - CMOS: the technology which has changed the world

- 3. Из пещер к цифровому обществу

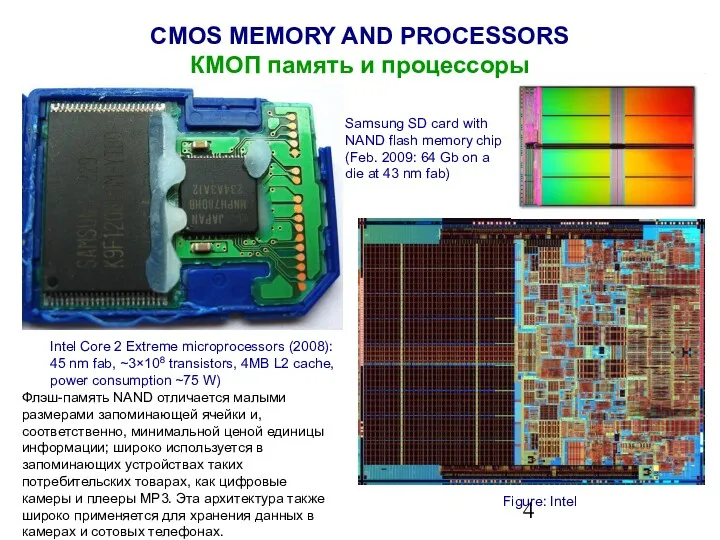

- 4. CMOS MEMORY AND PROCESSORS КМОП память и процессоры Intel Core 2 Extreme microprocessors (2008): 45 nm

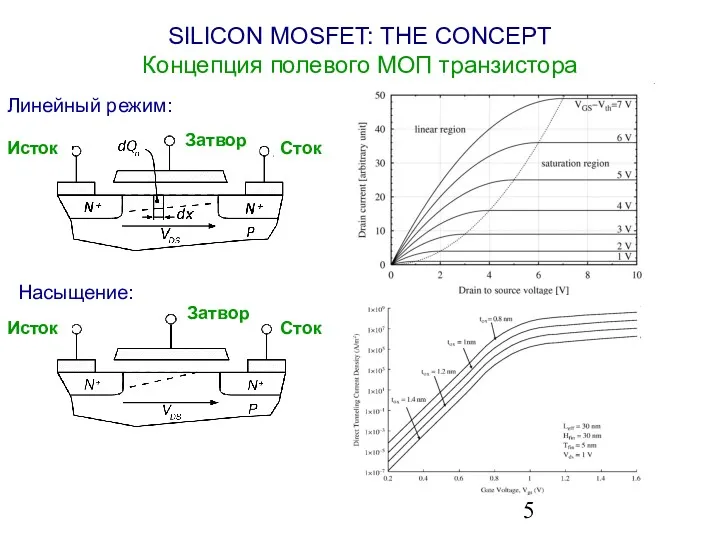

- 5. SILICON MOSFET: THE CONCEPT Концепция полевого МОП транзистора Линейный режим: Насыщение: Исток Исток Сток Сток Затвор

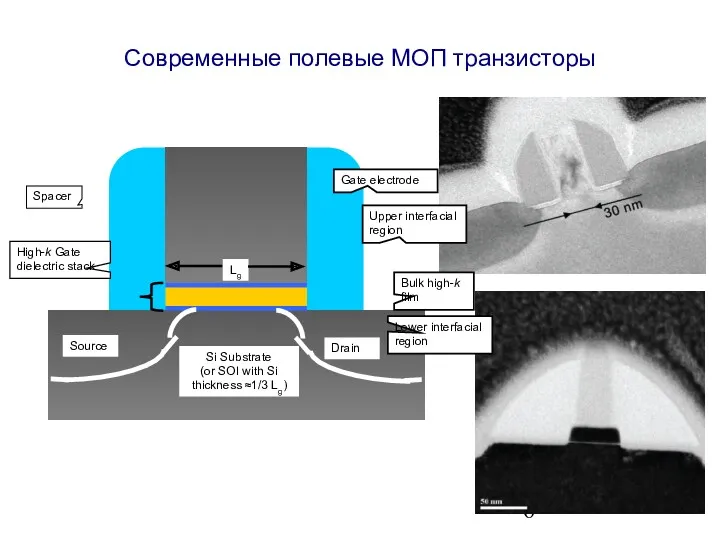

- 6. Современные полевые МОП транзисторы Upper interfacial region Bulk high-k film Lower interfacial region Gate electrode Si

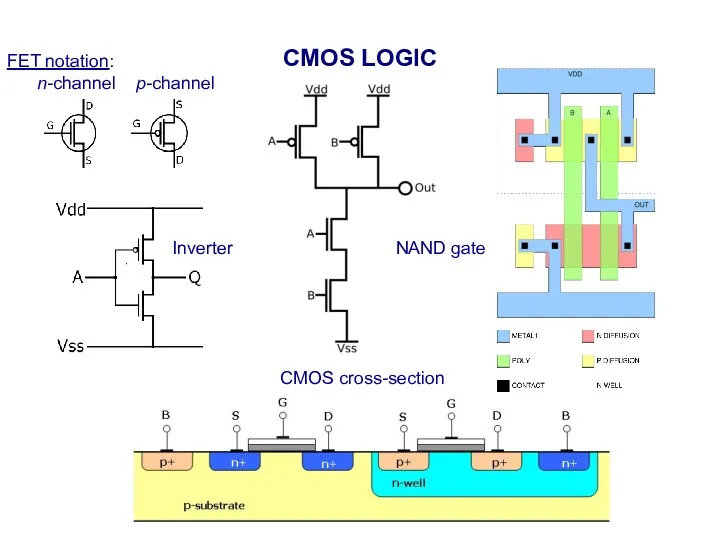

- 7. CMOS LOGIC Inverter NAND gate CMOS cross-section FET notation: n-channel p-channel

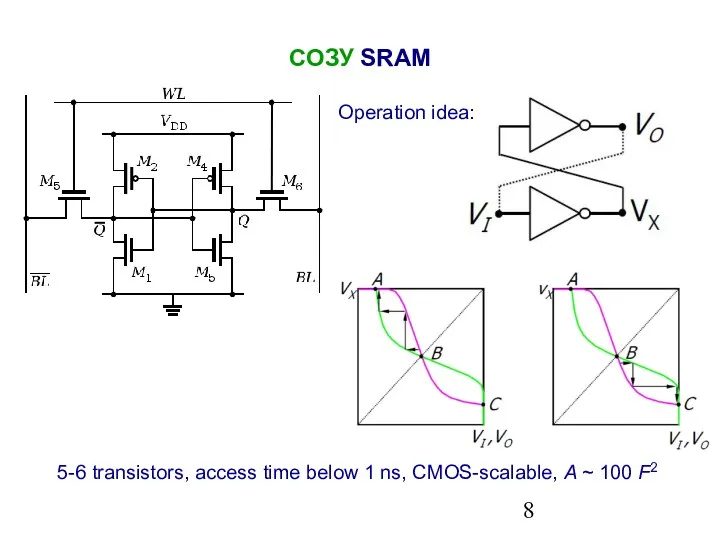

- 8. СОЗУ SRAM 5-6 transistors, access time below 1 ns, CMOS-scalable, A ~ 100 F2 Operation idea:

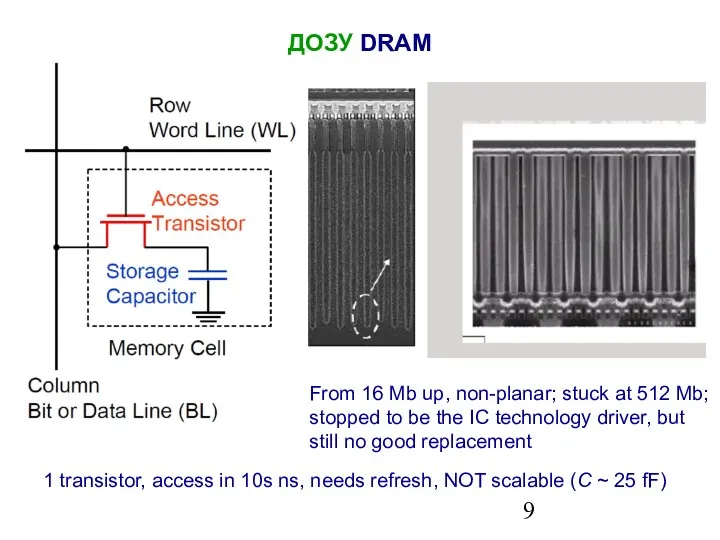

- 9. ДОЗУ DRAM 1 transistor, access in 10s ns, needs refresh, NOT scalable (C ~ 25 fF)

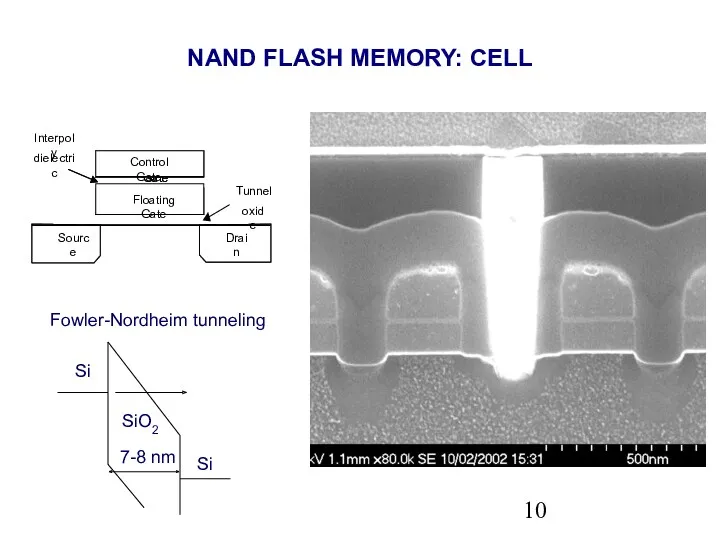

- 10. NAND FLASH MEMORY: CELL Drain Source Control Gate Interpoly Drain Source Control Gate Drain Source Floating

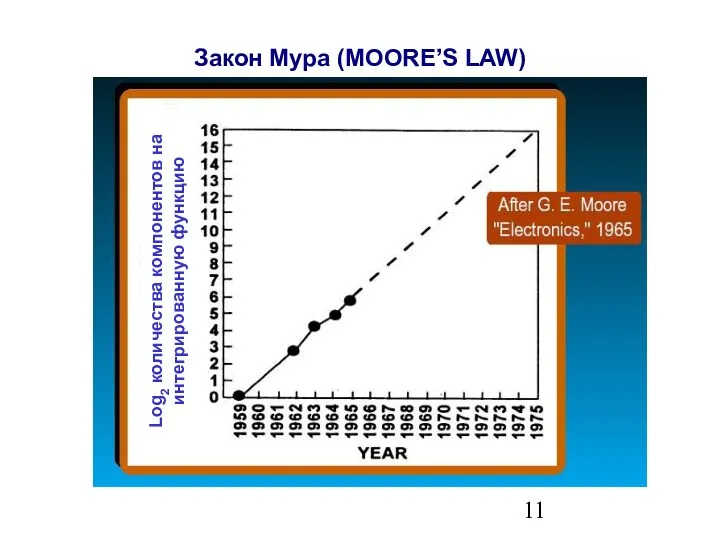

- 11. Закон Мура (MOORE’S LAW) Log2 количества компонентов на интегрированную функцию

- 12. Закон Мура для интегрированных схем Figure: Intel Сложность интегрированных схем

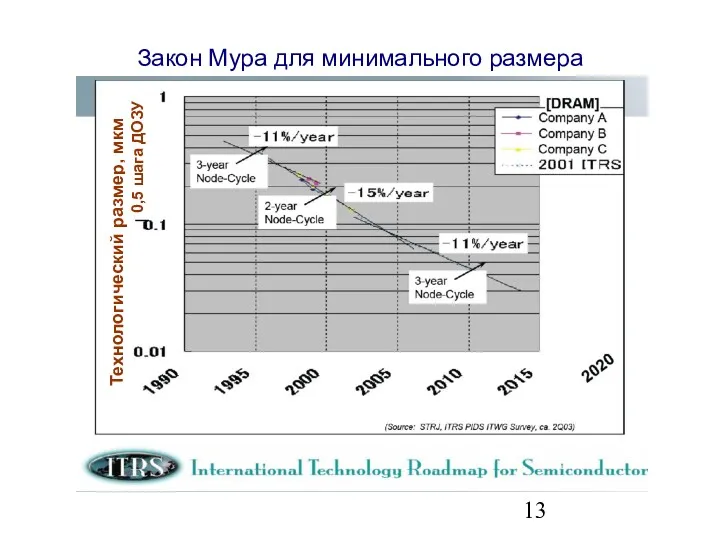

- 13. Закон Мура для минимального размера Технологический размер, мкм 0,5 шага ДОЗУ

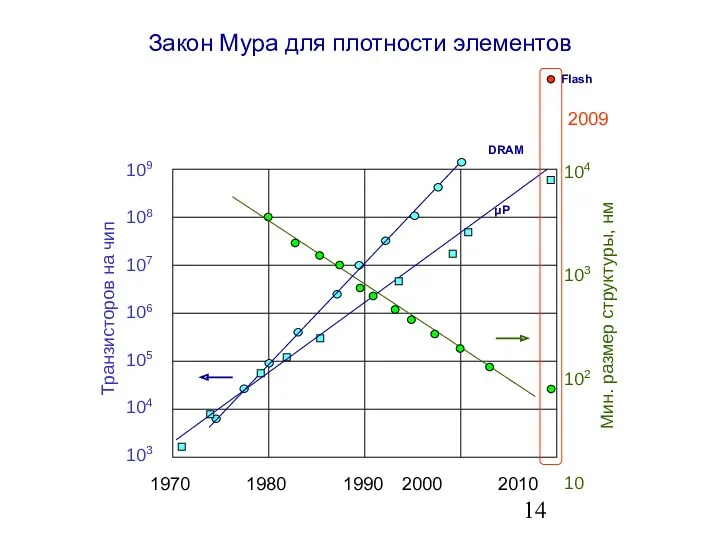

- 14. 1970 1980 1990 2000 2010 Закон Мура для плотности элементов Транзисторов на чип 109 108 107

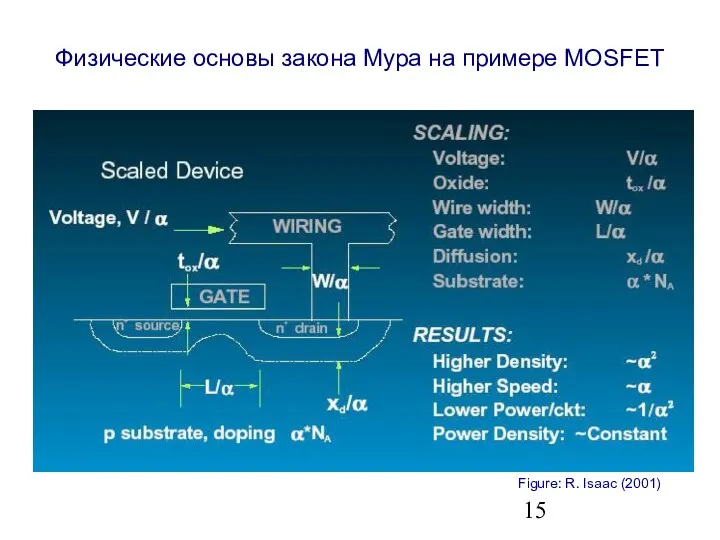

- 15. Физические основы закона Мура на примере MOSFET Figure: R. Isaac (2001)

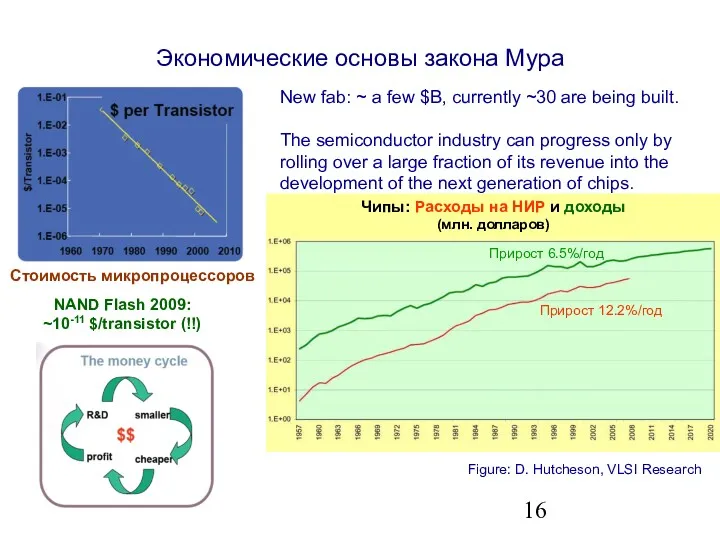

- 16. Экономические основы закона Мура Стоимость микропроцессоров NAND Flash 2009: ~10-11 $/transistor (!!) Figure: D. Hutcheson, VLSI

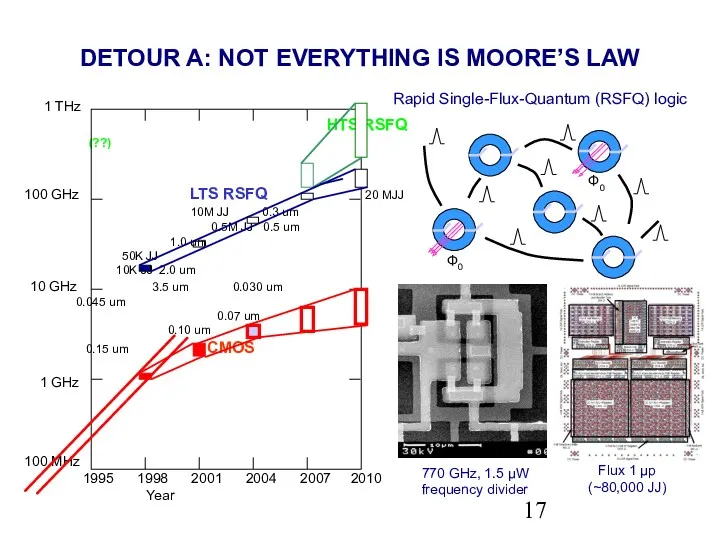

- 17. 1 THz HTS RSFQ (??) 100 GHz LTS RSFQ 20 MJJ 10M JJ 0.3 um 0.5M

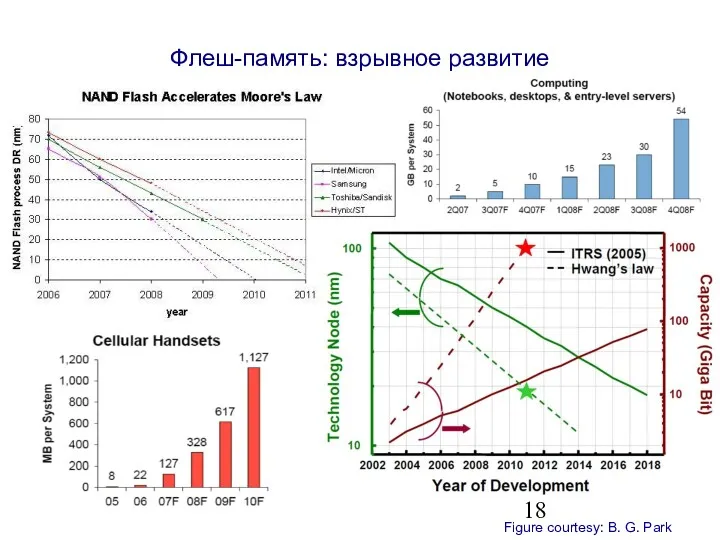

- 18. Флеш-память: взрывное развитие Figure courtesy: B. G. Park

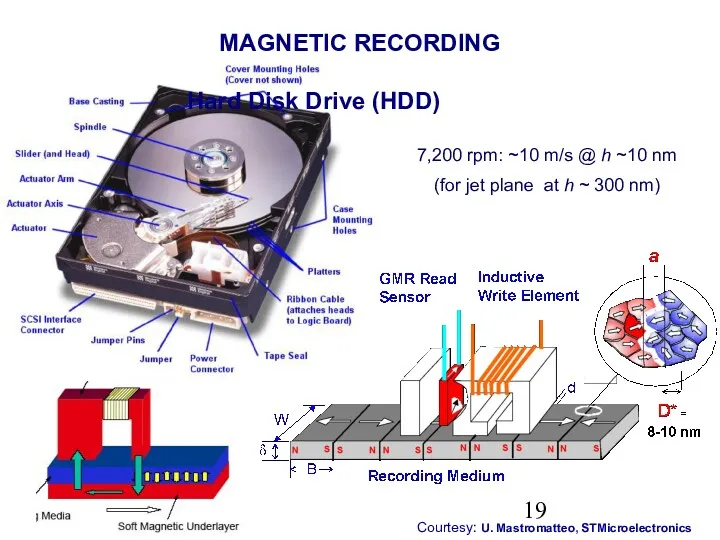

- 19. Courtesy: U. Mastromatteo, STMicroelectronics MAGNETIC RECORDING Hard Disk Drive (HDD) 7,200 rpm: ~10 m/s @ h

- 20. MAGNETIC RECORDING: AREAL DENSITY AS OF 2001

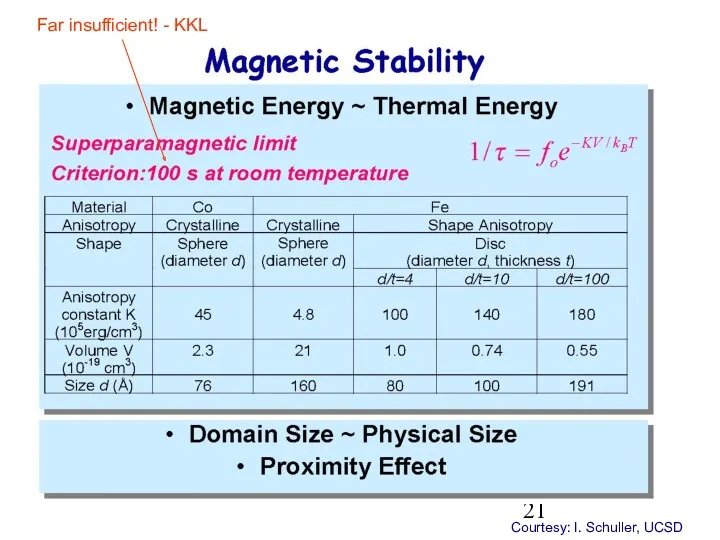

- 21. Courtesy: I. Schuller, UCSD Far insufficient! - KKL

- 23. Скачать презентацию

урок Ветер

урок Ветер Виды информации

Виды информации Популяція біології. Вплив вітамінів на організм людини

Популяція біології. Вплив вітамінів на організм людини Глухие и звонкие согласные звуки

Глухие и звонкие согласные звуки Портрет воды

Портрет воды Исторические типы философии. Античная философия

Исторические типы философии. Античная философия Лекция 1-2020 (общ. данные)

Лекция 1-2020 (общ. данные) Презентация Бурятский национальный костюм

Презентация Бурятский национальный костюм Sonic Theology

Sonic Theology Недобросовестная конкуренция

Недобросовестная конкуренция Спортивный комплекс Крылатское

Спортивный комплекс Крылатское Период младенчества (грудного возраста). Практическое занятие

Период младенчества (грудного возраста). Практическое занятие Новые ароматы из Франции

Новые ароматы из Франции Презентация Замки Луары

Презентация Замки Луары Понятие орнамент

Понятие орнамент Прямая и косвенная речь

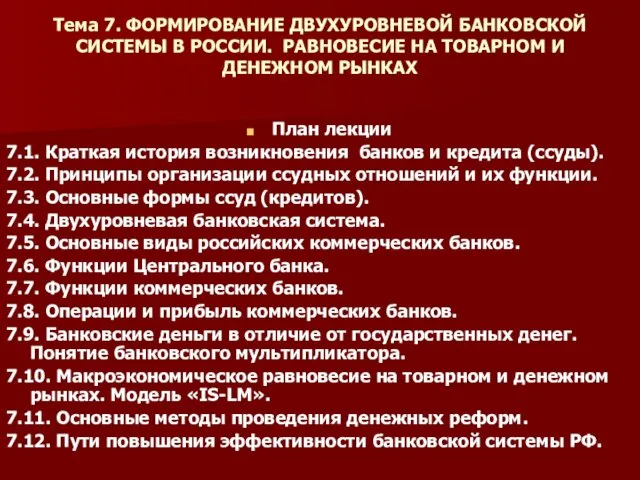

Прямая и косвенная речь Формирование двухуровневой банковской системы в России. Равновесие на товарном и денежном рынках. (Тема 7)

Формирование двухуровневой банковской системы в России. Равновесие на товарном и денежном рынках. (Тема 7) Закономерности наследования признаков

Закономерности наследования признаков Насосная станция нефтебаз

Насосная станция нефтебаз Заповедники, заказники, национальные парки, памятники природы

Заповедники, заказники, национальные парки, памятники природы Презентация к уроку технологии.

Презентация к уроку технологии. Квантовая оптика. Тепловое излучение

Квантовая оптика. Тепловое излучение Синтоизм. Суть синтоизма

Синтоизм. Суть синтоизма презентация Литье из гипса. Подсвечник из листьев

презентация Литье из гипса. Подсвечник из листьев Александр Сергеевич Пушкин

Александр Сергеевич Пушкин Народная педагогика конца XIX века

Народная педагогика конца XIX века Боевая травма сосудов

Боевая травма сосудов Рідини тіла. Склад і функції крові

Рідини тіла. Склад і функції крові