Содержание

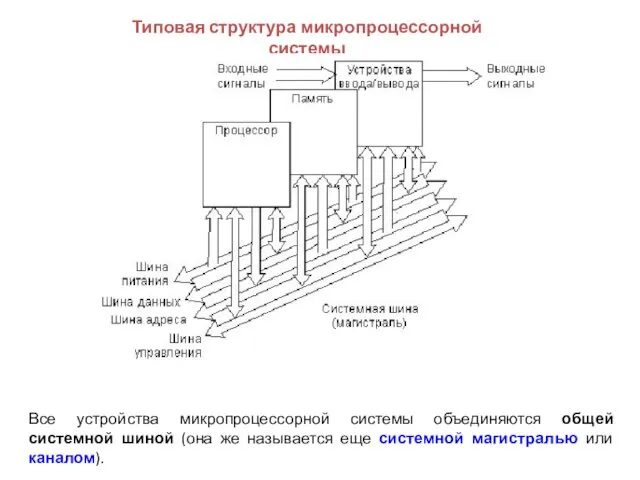

- 2. Типовая структура микропроцессорной системы Все устройства микропроцессорной системы объединяются общей системной шиной (она же называется еще

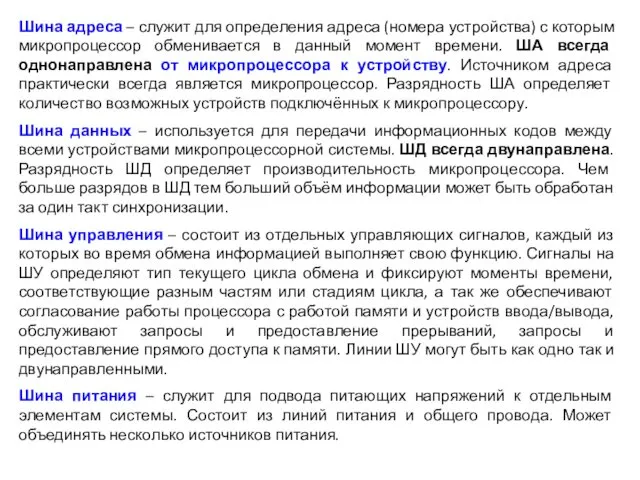

- 3. Шина адреса – служит для определения адреса (номера устройства) с которым микропроцессор обменивается в данный момент

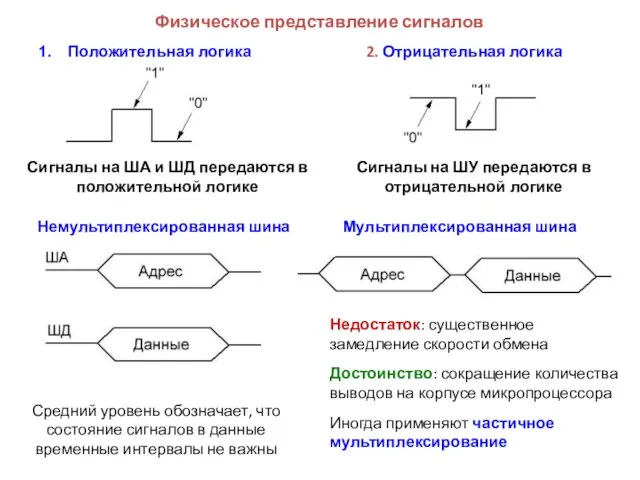

- 4. Физическое представление сигналов Положительная логика 2. Отрицательная логика Немультиплексированная шина Средний уровень обозначает, что состояние сигналов

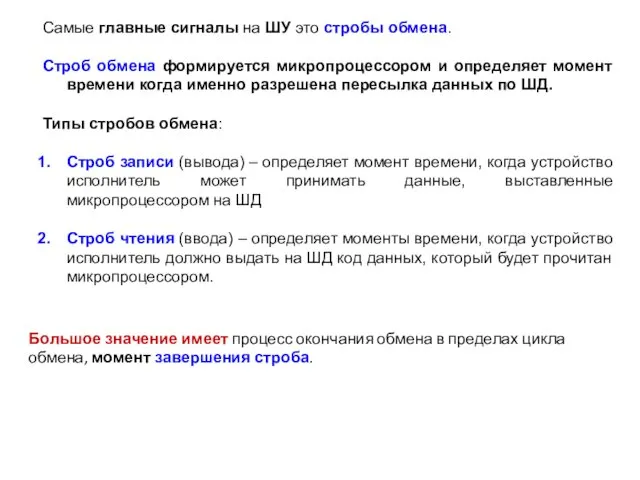

- 5. Самые главные сигналы на ШУ это стробы обмена. Строб обмена формируется микропроцессором и определяет момент времени

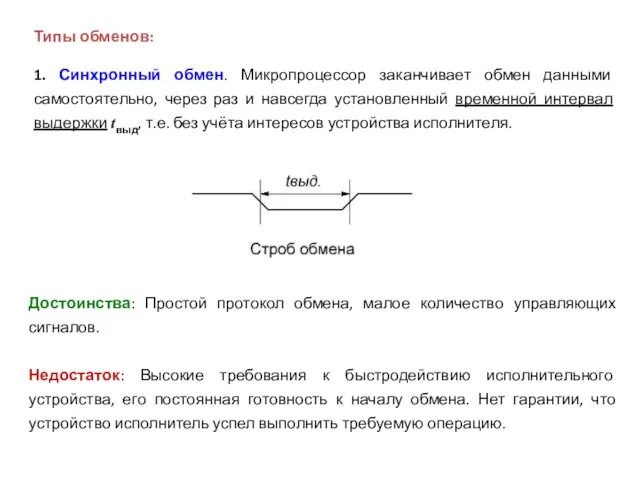

- 6. Типы обменов: 1. Синхронный обмен. Микропроцессор заканчивает обмен данными самостоятельно, через раз и навсегда установленный временной

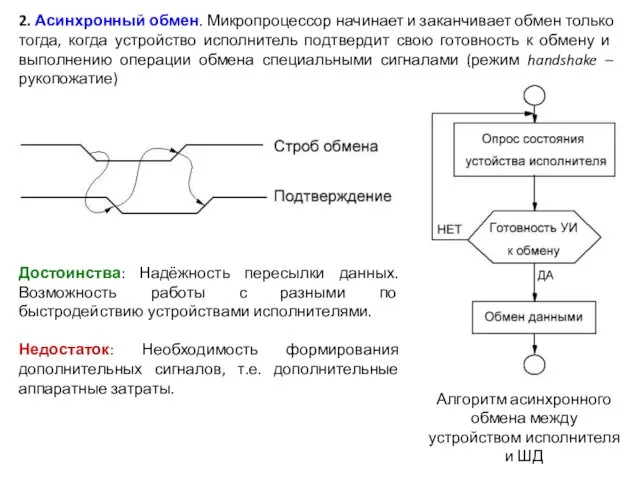

- 7. 2. Асинхронный обмен. Микропроцессор начинает и заканчивает обмен только тогда, когда устройство исполнитель подтвердит свою готовность

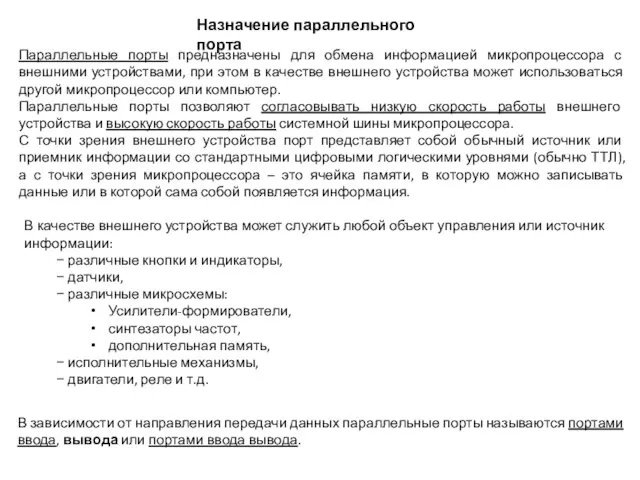

- 8. Назначение параллельного порта Параллельные порты предназначены для обмена информацией микропроцессора с внешними устройствами, при этом в

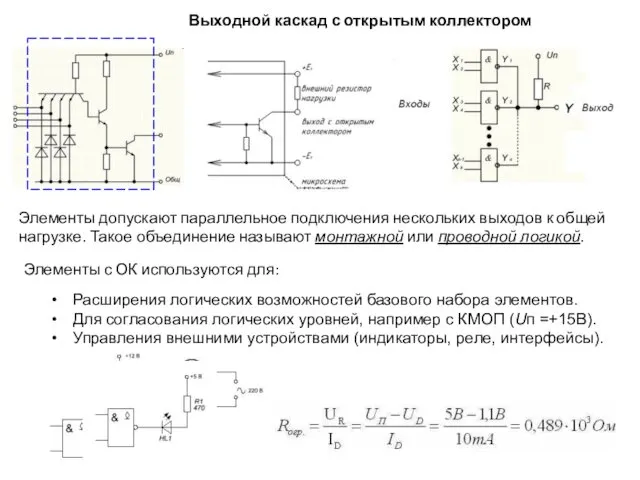

- 9. Выходной каскад с открытым коллектором Элементы с ОК используются для: Расширения логических возможностей базового набора элементов.

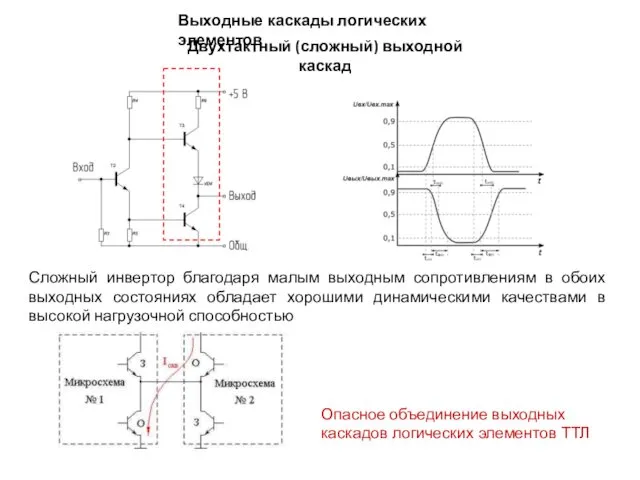

- 10. Выходные каскады логических элементов Двухтактный (сложный) выходной каскад Опасное объединение выходных каскадов логических элементов ТТЛ Сложный

- 11. Выходной каскад с третьим состоянием (Z–состоянием) Z–состояние необходимо когда выходы нескольких логических элементов подключены к одной

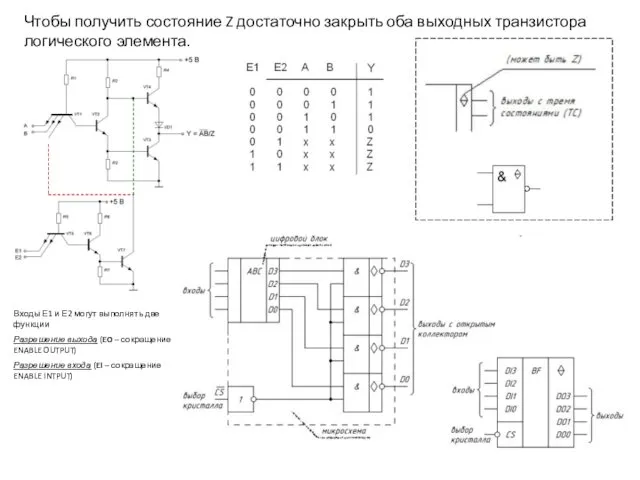

- 12. Чтобы получить состояние Z достаточно закрыть оба выходных транзистора логического элемента. Входы Е1 и Е2 могут

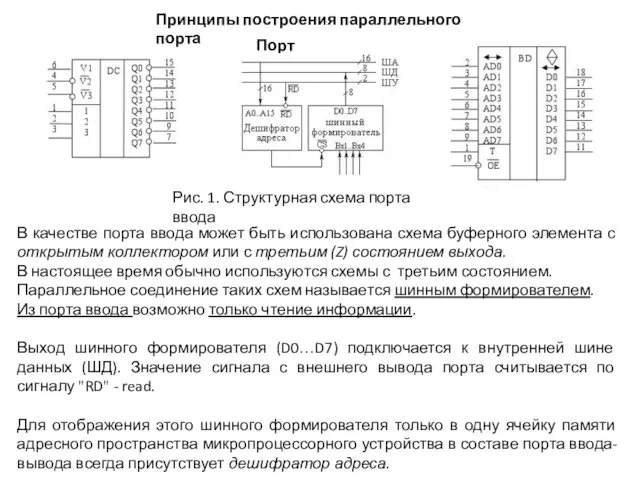

- 13. Порт ввода Рис. 1. Структурная схема порта ввода В качестве порта ввода может быть использована схема

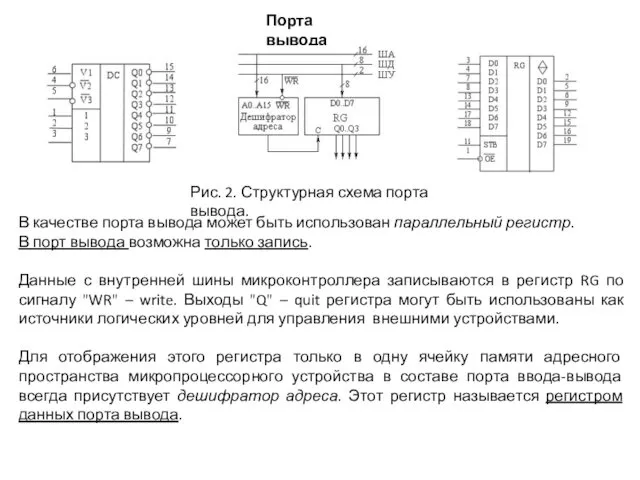

- 14. Порта вывода Рис. 2. Структурная схема порта вывода. В качестве порта вывода может быть использован параллельный

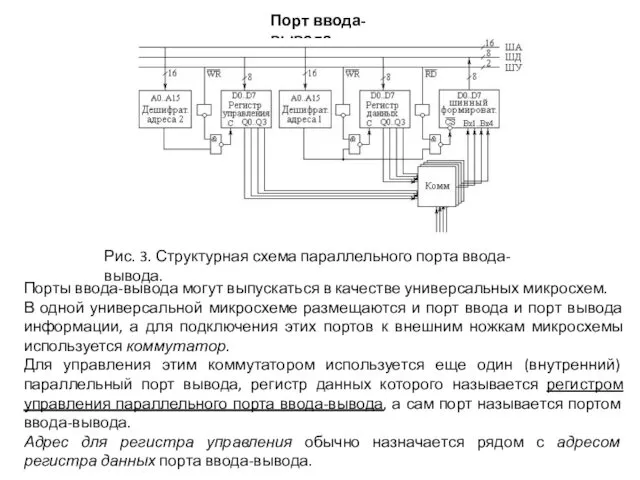

- 15. Порт ввода-вывода Рис. 3. Структурная схема параллельного порта ввода-вывода. Порты ввода-вывода могут выпускаться в качестве универсальных

- 16. Каждый порт микроконтроллеров состоит из определенного числа выводов, через которые микроконтроллер может осуществлять прием и передачу

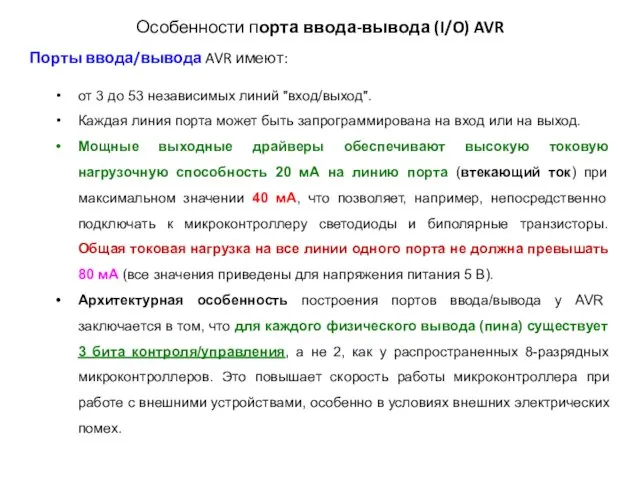

- 17. Особенности порта ввода-вывода (I/O) AVR Порты ввода/вывода AVR имеют: от 3 до 53 независимых линий "вход/выход".

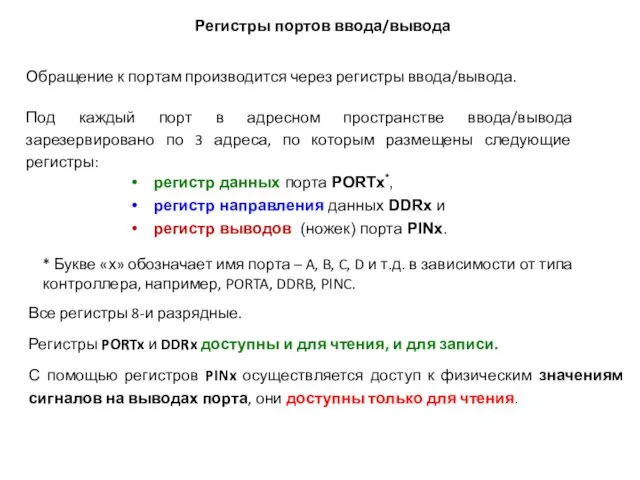

- 18. Обращение к портам производится через регистры ввода/вывода. Под каждый порт в адресном пространстве ввода/вывода зарезервировано по

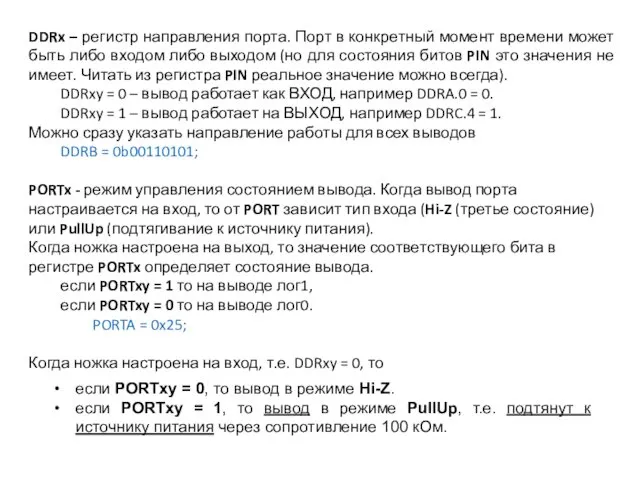

- 19. DDRx – регистр направления порта. Порт в конкретный момент времени может быть либо входом либо выходом

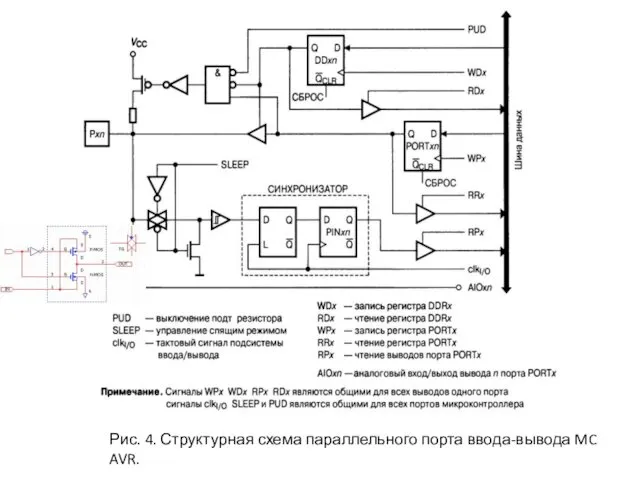

- 20. Рис. 4. Структурная схема параллельного порта ввода-вывода MC AVR.

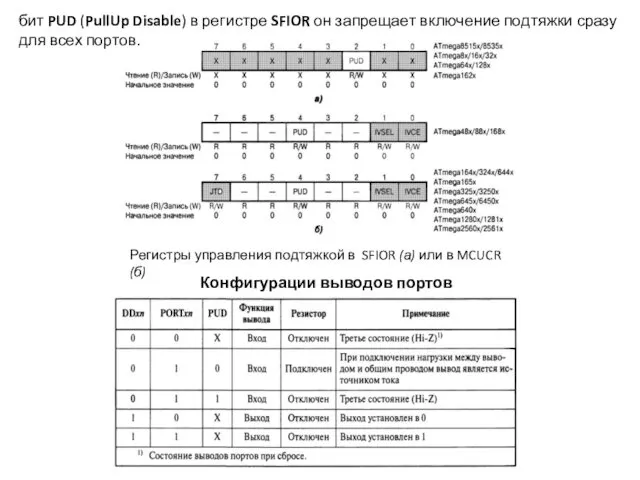

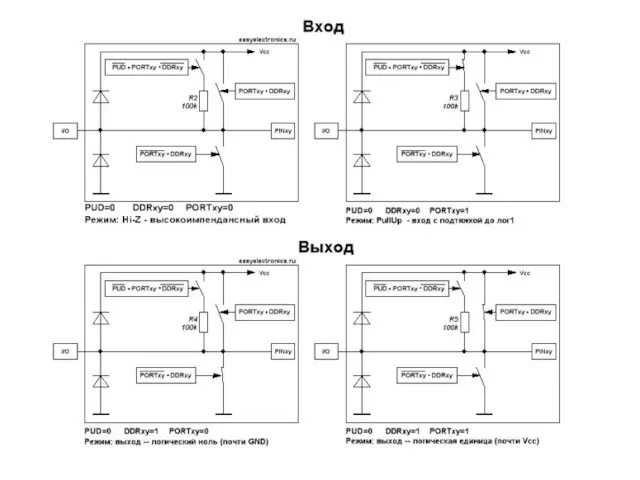

- 21. Регистры управления подтяжкой в SFIOR (а) или в MCUCR (б) Конфигурации выводов портов бит PUD (PullUp

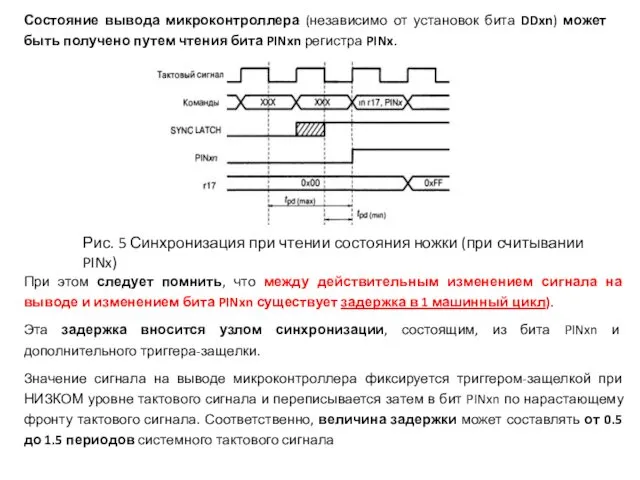

- 23. Состояние вывода микроконтроллера (независимо от установок бита DDxn) может быть получено путем чтения бита PINxn регистра

- 25. Скачать презентацию

Антиоксидантный комплекс витаминов Новомин. Сибирское здоровье

Антиоксидантный комплекс витаминов Новомин. Сибирское здоровье День летних и осенних именинников

День летних и осенних именинников Полы промышленных зданий

Полы промышленных зданий Жил человек... христианские притчи.

Жил человек... христианские притчи. Проблемы ИТВ. Кратко о плагиатах телеканалов и о плохих каналах

Проблемы ИТВ. Кратко о плагиатах телеканалов и о плохих каналах Оценка уровня обслуживания в магазинах Колеса даром

Оценка уровня обслуживания в магазинах Колеса даром Развитие страхования жизни в ООО Альянс жизнь

Развитие страхования жизни в ООО Альянс жизнь Обзор распространенных причин, препятствующих осуществлению государственного кадастрового учета

Обзор распространенных причин, препятствующих осуществлению государственного кадастрового учета Диагностика метапредметных результатов обучения

Диагностика метапредметных результатов обучения Кофе и кофейные напитки

Кофе и кофейные напитки Гипотиреоз

Гипотиреоз Неорганические (минеральные) воздушные вяжущие вещества

Неорганические (минеральные) воздушные вяжущие вещества Жизнь и творчество Ван Гога

Жизнь и творчество Ван Гога Физические и механические свойства древесины. 6 класс

Физические и механические свойства древесины. 6 класс Теория + пратика = ? Размышления, рассуждения, выводы

Теория + пратика = ? Размышления, рассуждения, выводы Проблемное обучение на уроке математики

Проблемное обучение на уроке математики Проект бурения скважины на Верхне-Ветлянском месторождении с выбором мероприятий по борьбе с поглощениями бурового раствора

Проект бурения скважины на Верхне-Ветлянском месторождении с выбором мероприятий по борьбе с поглощениями бурового раствора Сестринский уход при различных заболеваниях и состояниях

Сестринский уход при различных заболеваниях и состояниях Учебный тренажёр и проверочный тест по теме: Члены предложения

Учебный тренажёр и проверочный тест по теме: Члены предложения Презентация урока-исследования Байкал-уникальное творение природы

Презентация урока-исследования Байкал-уникальное творение природы Презентация1 апреля

Презентация1 апреля Толерантность - путь к культуре мира.

Толерантность - путь к культуре мира. Введение в предмет Алгебра логики

Введение в предмет Алгебра логики Презентация к классному часу в 7 классе по теме Кижи

Презентация к классному часу в 7 классе по теме Кижи Тіс-жақ аймағының аурулары, асқазан ішек жолдарында эррозиялы ойық-жаралы зақымдануға алып келетін факторлар

Тіс-жақ аймағының аурулары, асқазан ішек жолдарында эррозиялы ойық-жаралы зақымдануға алып келетін факторлар Регистрирующее устройство

Регистрирующее устройство Единый всекубанский классный час Год культуры - история Кубани в лицах, 4 класс

Единый всекубанский классный час Год культуры - история Кубани в лицах, 4 класс Отчёт-презентация на тему:Социально-личностное развитие дошкольников

Отчёт-презентация на тему:Социально-личностное развитие дошкольников