Содержание

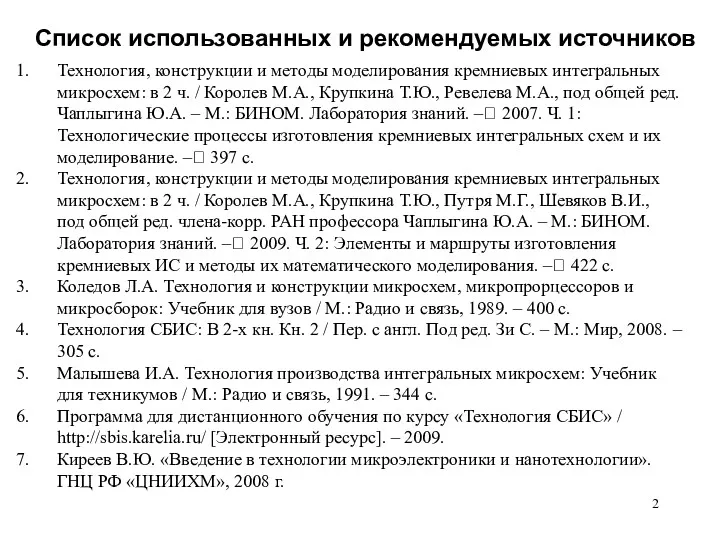

- 2. Список использованных и рекомендуемых источников Технология, конструкции и методы моделирования кремниевых интегральных микросхем: в 2 ч.

- 4. Уровень технологии определяется минимально возможной топологической нормой, т. е. минимальным размером элемента или зазора в периодических

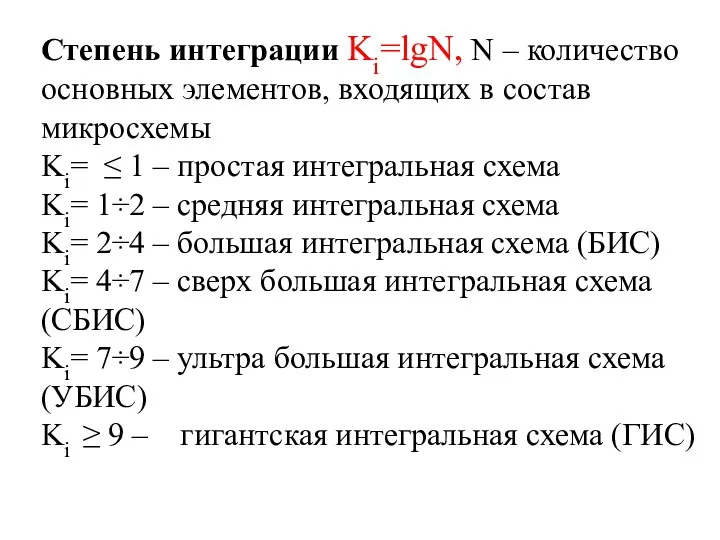

- 5. Степень интеграции Ki=lgN, N – количество основных элементов, входящих в состав микросхемы Ki= ≤ 1 –

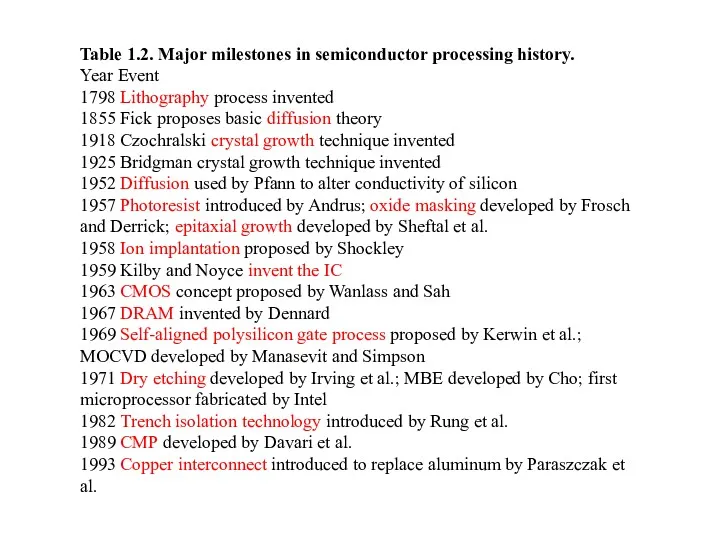

- 6. Table 1.2. Major milestones in semiconductor processing history. Year Event 1798 Lithography process invented 1855 Fick

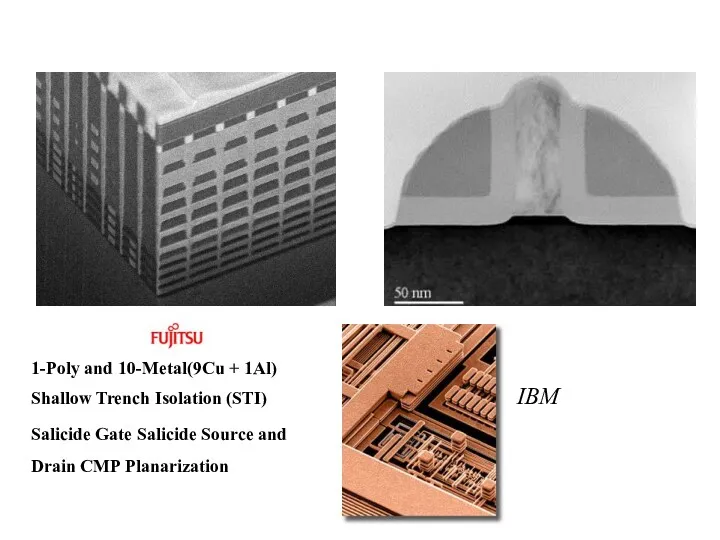

- 7. 1-Poly and 10-Metal(9Cu + 1Al) Shallow Trench Isolation (STI) Salicide Gate Salicide Source and Drain CMP

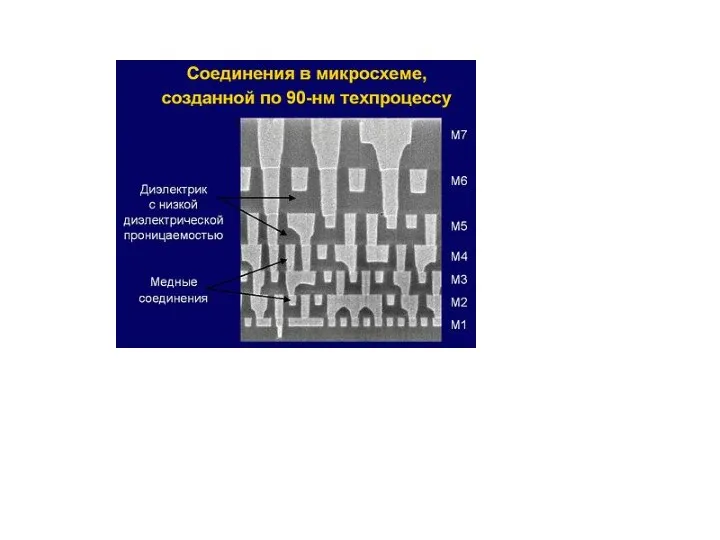

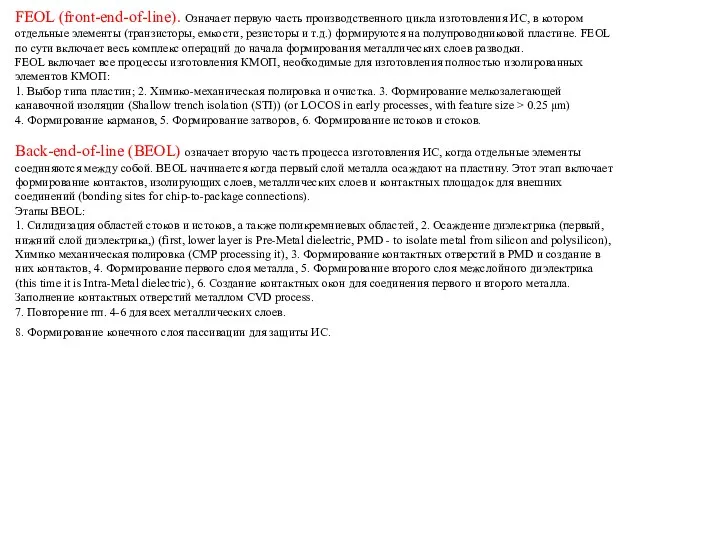

- 9. FEOL (front-end-of-line). Означает первую часть производственного цикла изготовления ИС, в котором отдельные элементы (транзисторы, емкости, резисторы

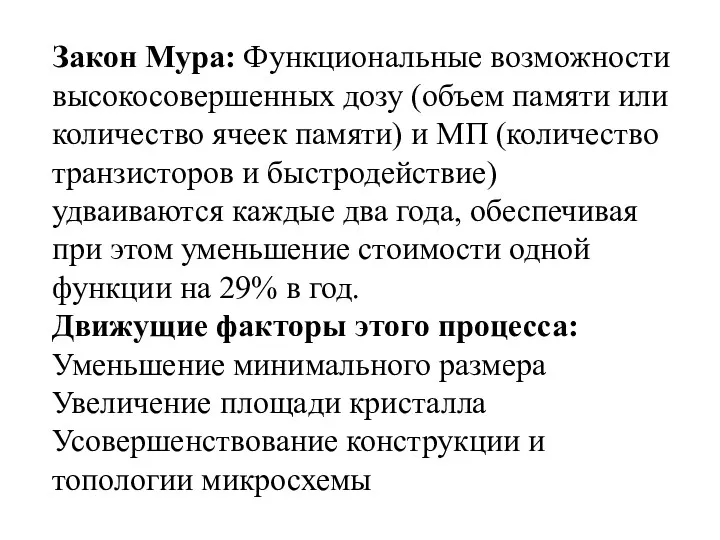

- 13. Закон Мура: Функциональные возможности высокосовершенных дозу (объем памяти или количество ячеек памяти) и МП (количество транзисторов

- 14. Закон Гордона Мура Современные тенденции масштабирования ИС могут быть сформулированы следующим образом: - новое поколение технологии

- 15. В последние десятилетия основной фактор повышения степени интеграции -масштабирование (уменьшение размеров элементов)

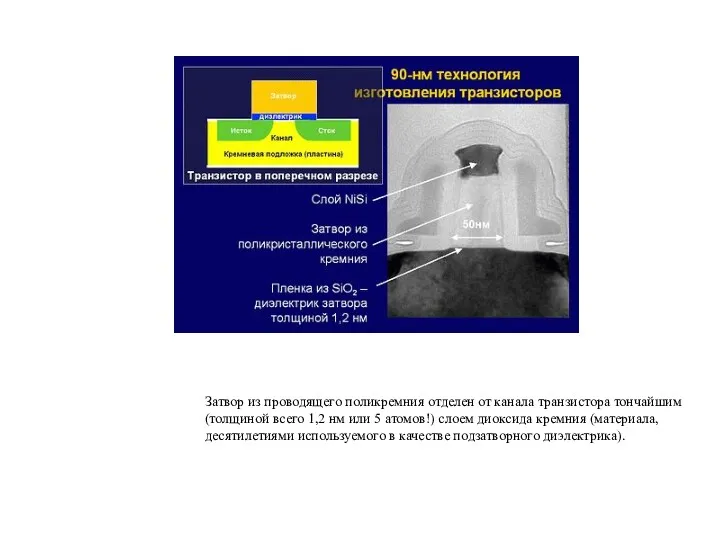

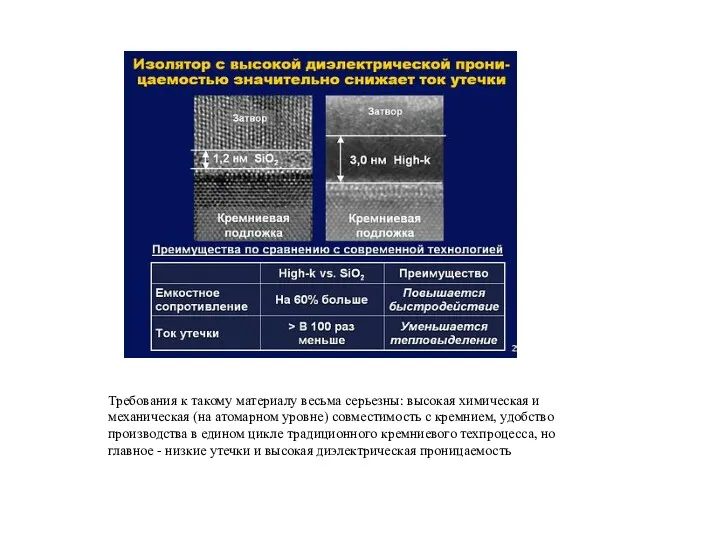

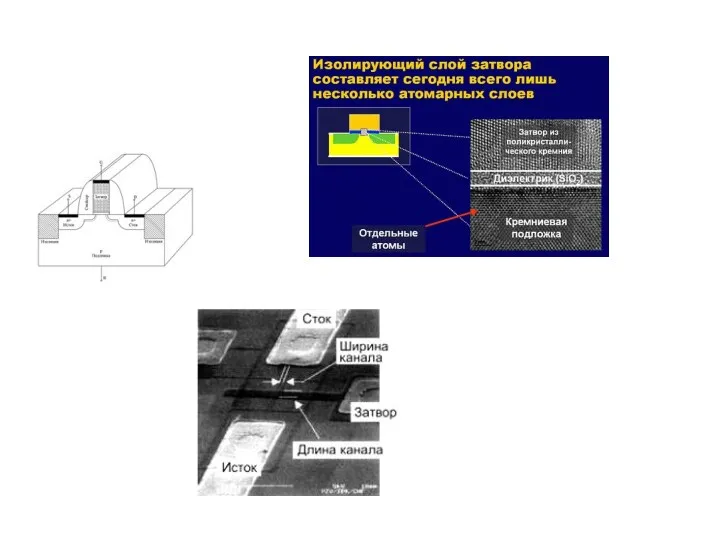

- 16. Затвор из проводящего поликремния отделен от канала транзистора тончайшим (толщиной всего 1,2 нм или 5 атомов!)

- 17. С ростом степени интеграции СБИС и систем на кристалле увеличивается доля чипов, содержащих аналоговые блоки, которые

- 19. Требования к такому материалу весьма серьезны: высокая химическая и механическая (на атомарном уровне) совместимость с кремнием,

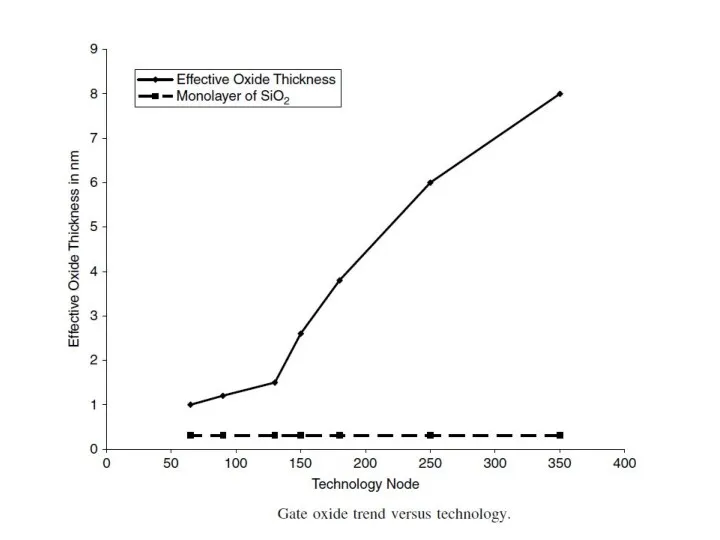

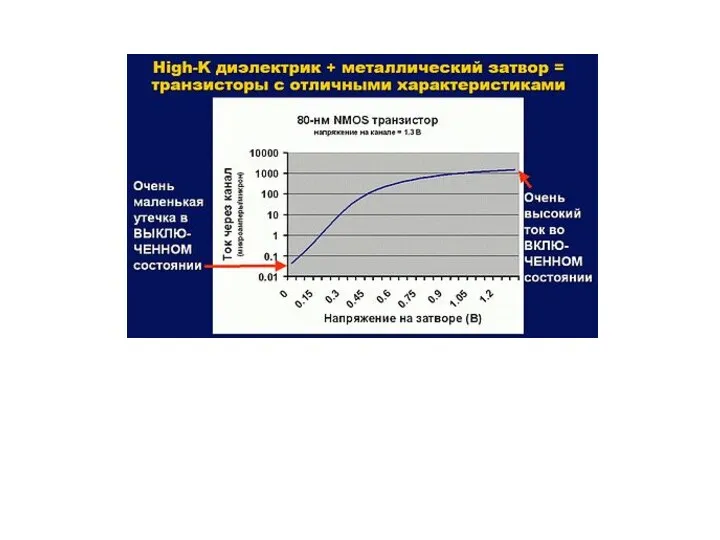

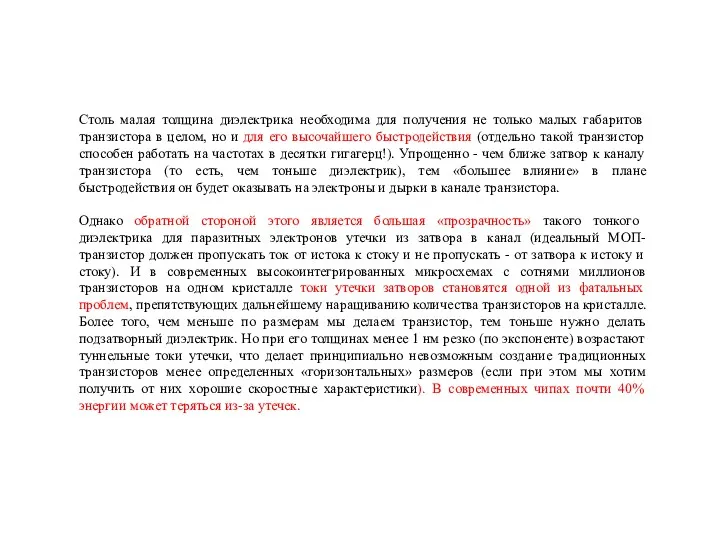

- 22. Столь малая толщина диэлектрика необходима для получения не только малых габаритов транзистора в целом, но и

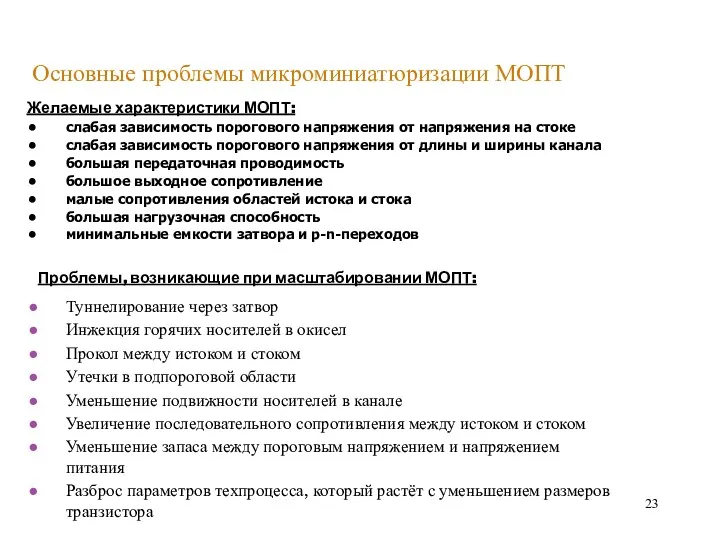

- 23. слабая зависимость порогового напряжения от напряжения на стоке слабая зависимость порогового напряжения от длины и ширины

- 24. Масштабирование МОПТ Сравнительная таблица технологий XXI века:

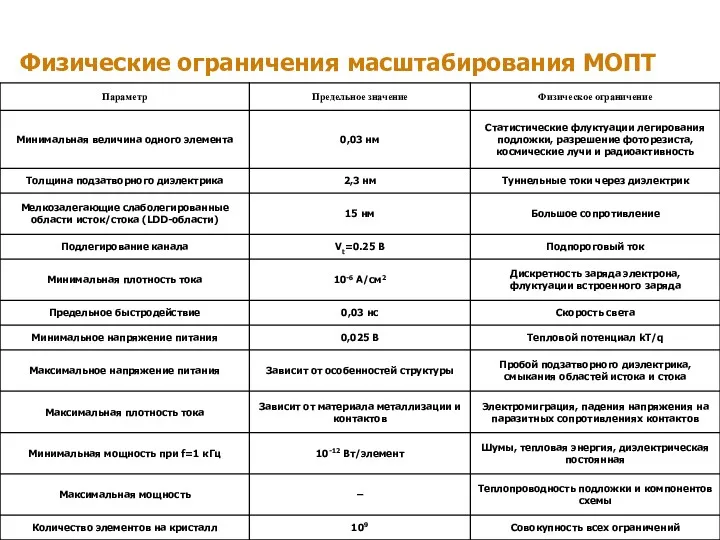

- 25. Физические ограничения масштабирования МОПТ

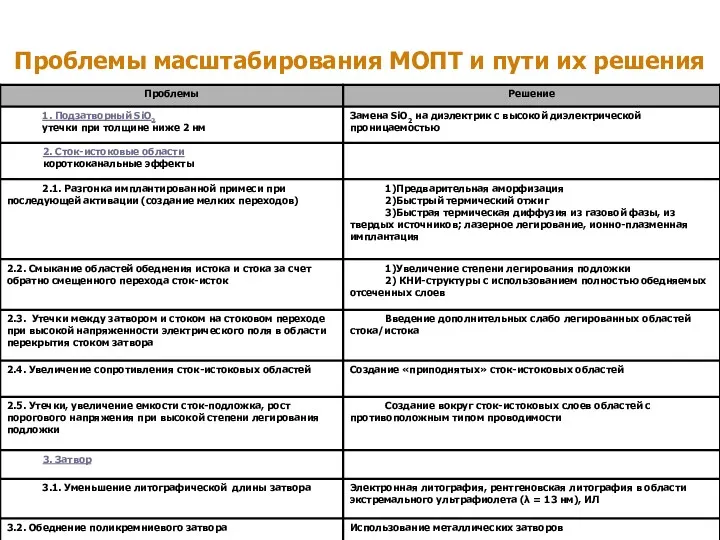

- 26. Проблемы масштабирования МОПТ и пути их решения

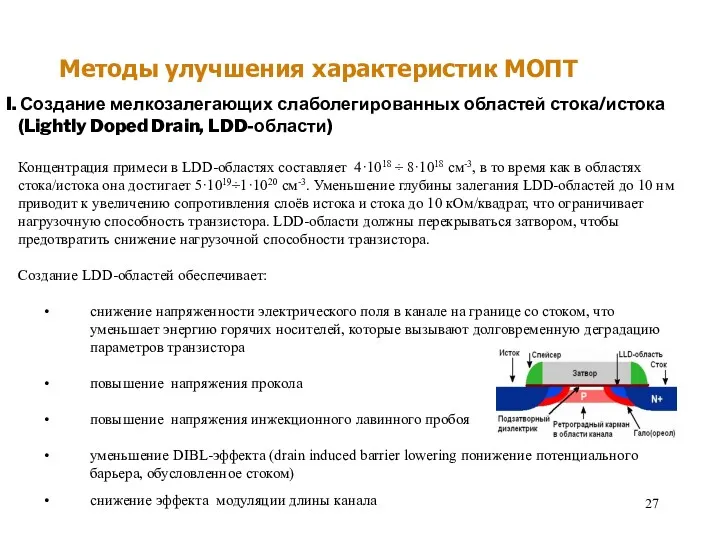

- 27. Методы улучшения характеристик МОПТ I. Создание мелкозалегающих слаболегированных областей стока/истока (Lightly Doped Drain, LDD-области) Концентрация примеси

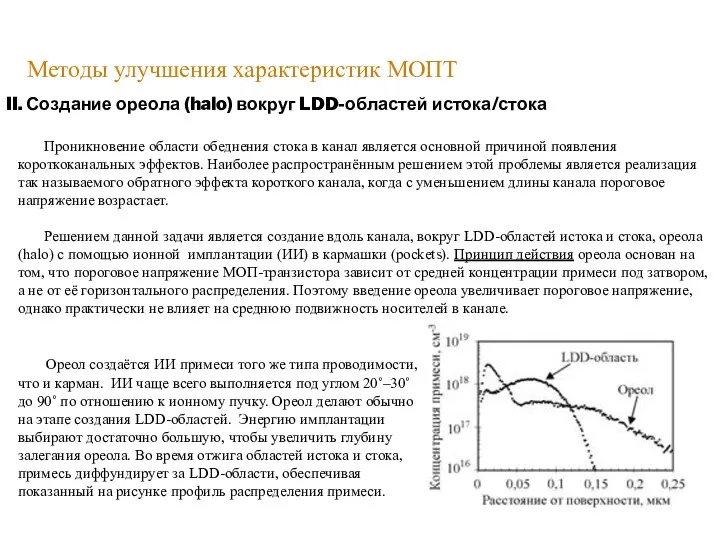

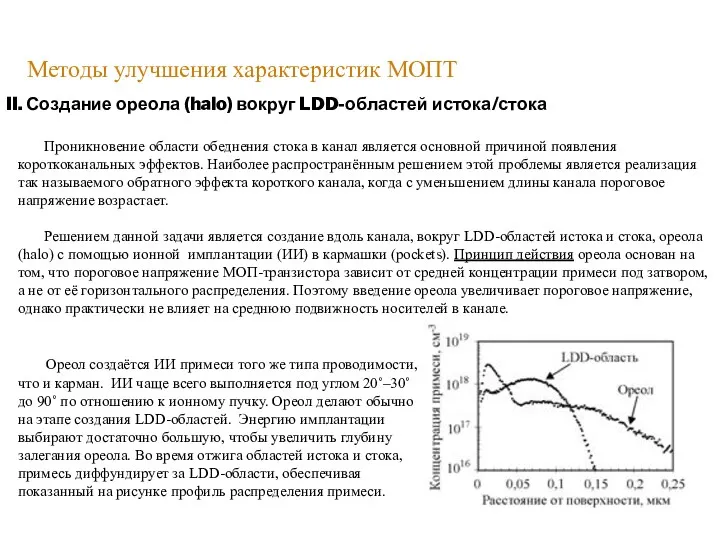

- 28. II. Создание ореола (halo) вокруг LDD-областей истока/стока Проникновение области обеднения стока в канал является основной причиной

- 29. II. Создание ореола (halo) вокруг LDD-областей истока/стока Проникновение области обеднения стока в канал является основной причиной

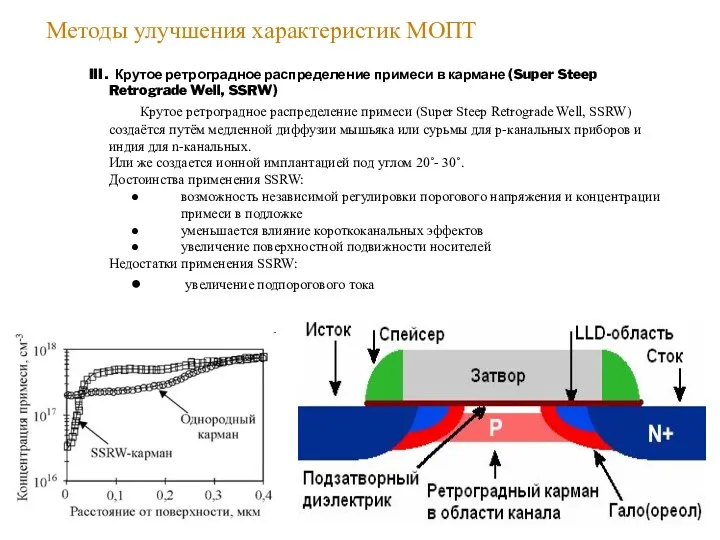

- 30. Методы улучшения характеристик МОПТ III . Крутое ретроградное распределение примеси в кармане (Super Steep Retrograde Well,

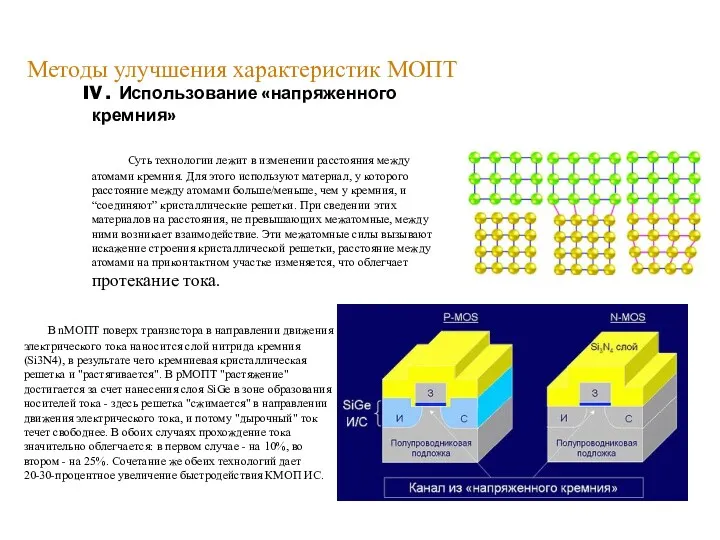

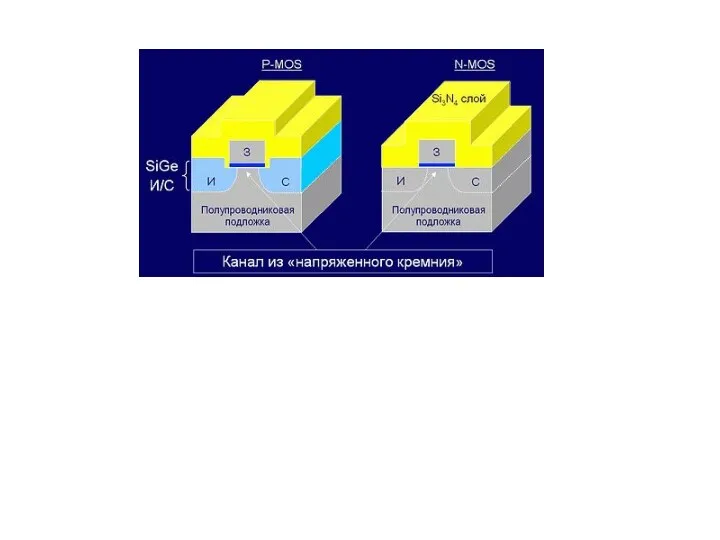

- 31. Методы улучшения характеристик МОПТ IV . Использование «напряженного кремния» Суть технологии лежит в изменении расстояния между

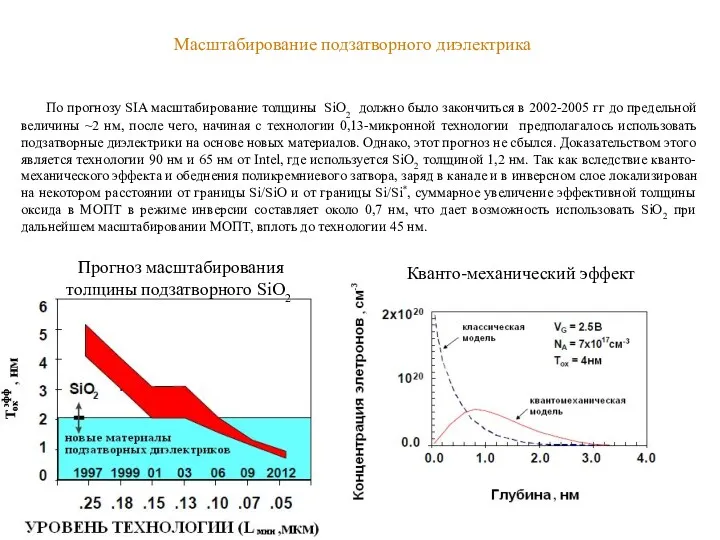

- 32. Масштабирование подзатворного диэлектрика Прогноз масштабирования толщины подзатворного SiO2 Кванто-механический эффект По прогнозу SIA масштабирование толщины SiO2

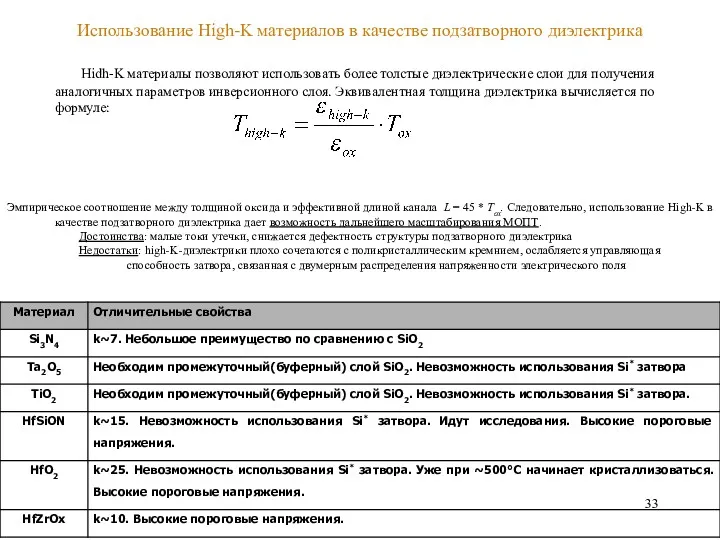

- 33. Использование High-K материалов в качестве подзатворного диэлектрика Hidh-K материалы позволяют использовать более толстые диэлектрические слои для

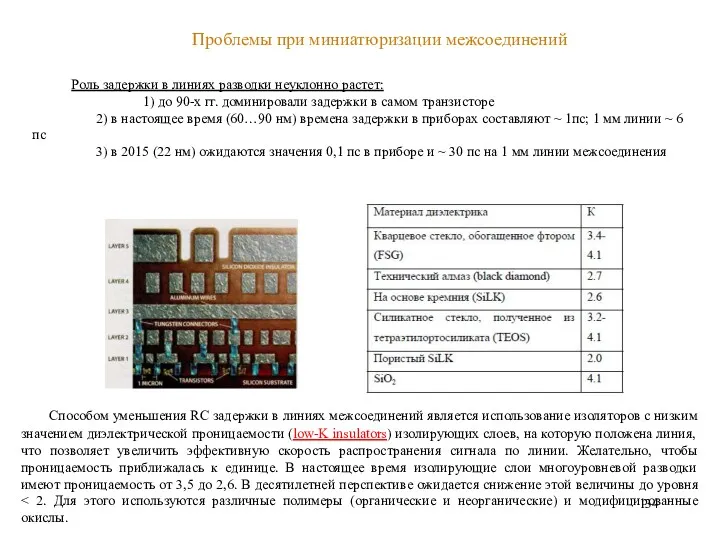

- 34. Проблемы при миниатюризации межсоединений Роль задержки в линиях разводки неуклонно растет: 1) до 90-х гг. доминировали

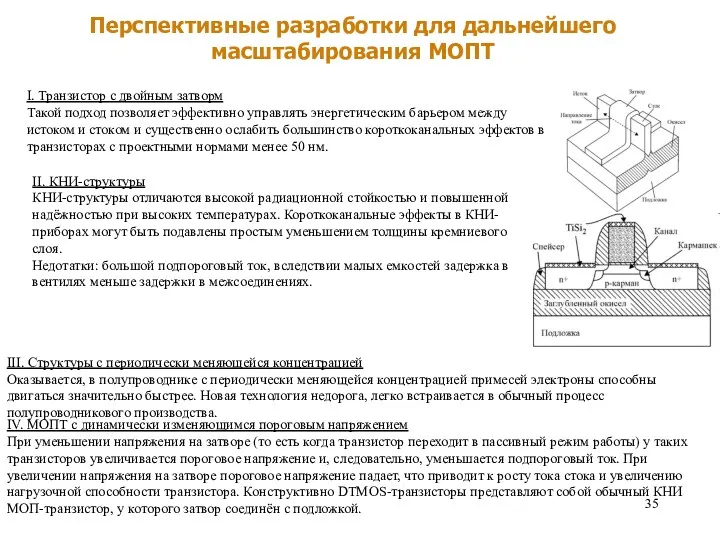

- 35. Перспективные разработки для дальнейшего масштабирования МОПТ I. Транзистор с двойным затворм Такой подход позволяет эффективно управлять

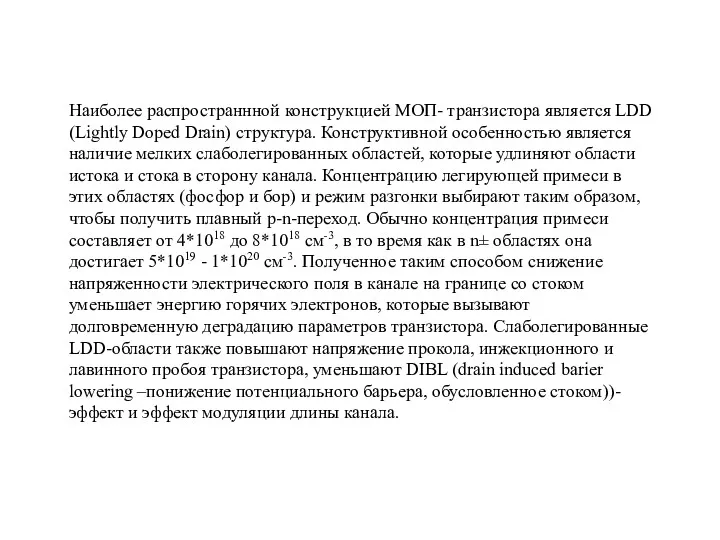

- 37. Наиболее распространнной конструкцией МОП- транзистора является LDD (Lightly Doped Drain) структура. Конструктивной особенностью является наличие мелких

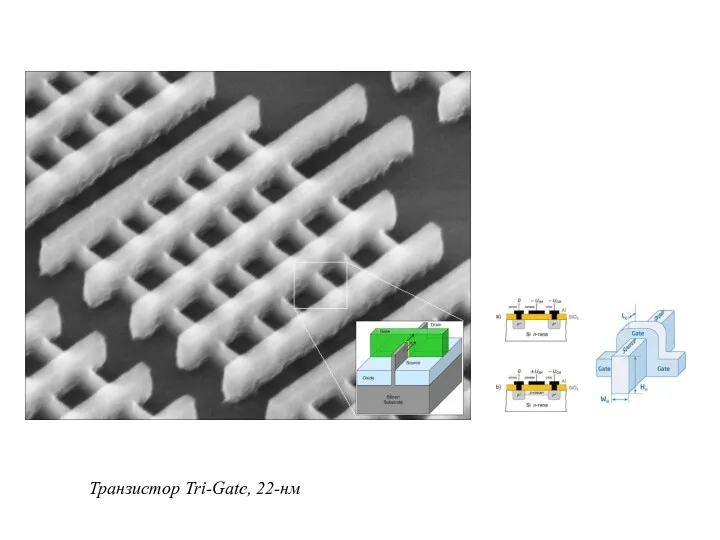

- 39. Транзистор Tri-Gate, 22-нм

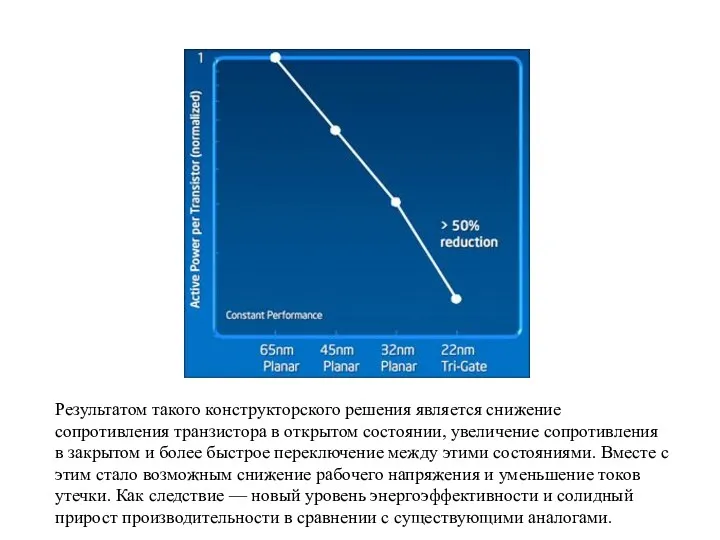

- 40. Результатом такого конструкторского решения является снижение сопротивления транзистора в открытом состоянии, увеличение сопротивления в закрытом и

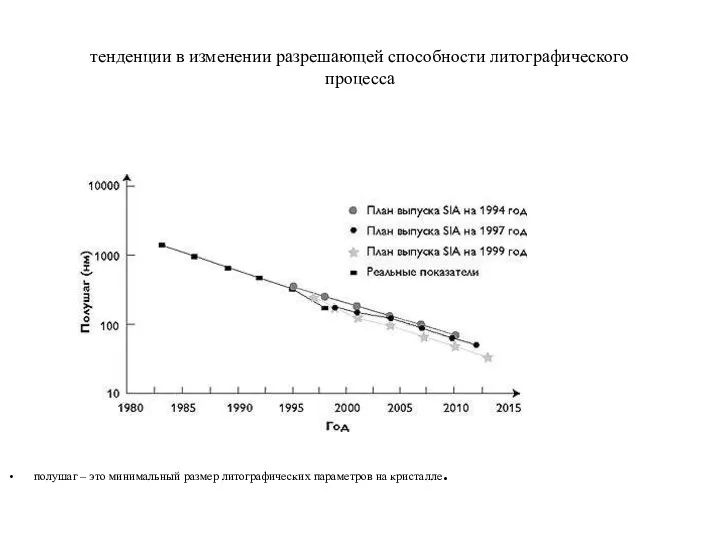

- 41. тенденции в изменении разрешающей способности литографического процесса полушаг – это минимальный размер литографических параметров на кристалле.

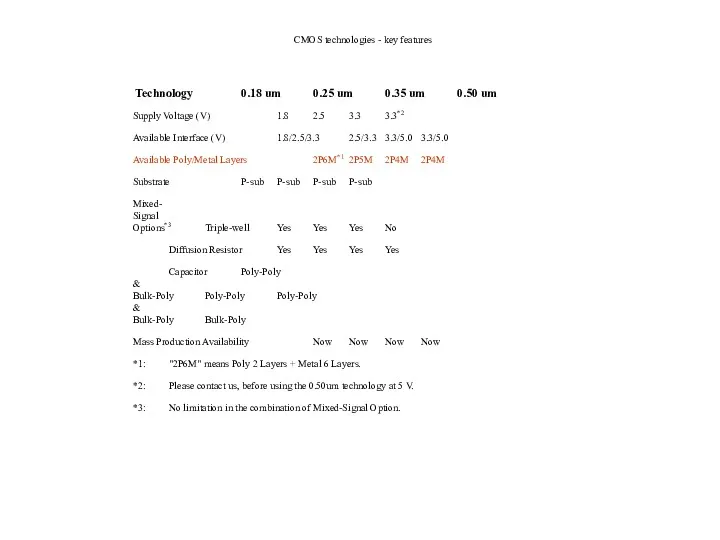

- 42. Technology 0.18 um 0.25 um 0.35 um 0.50 um Supply Voltage (V) 1.8 2.5 3.3 3.3*2

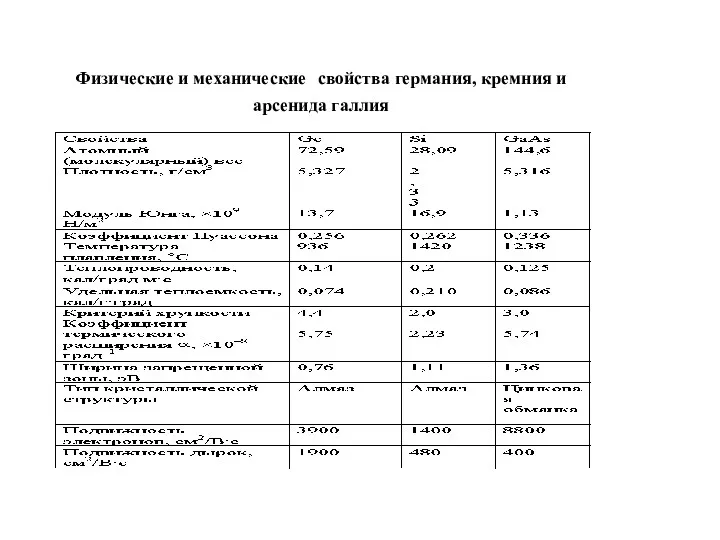

- 43. Физические и механические свойства германия, кремния и арсенида галлия

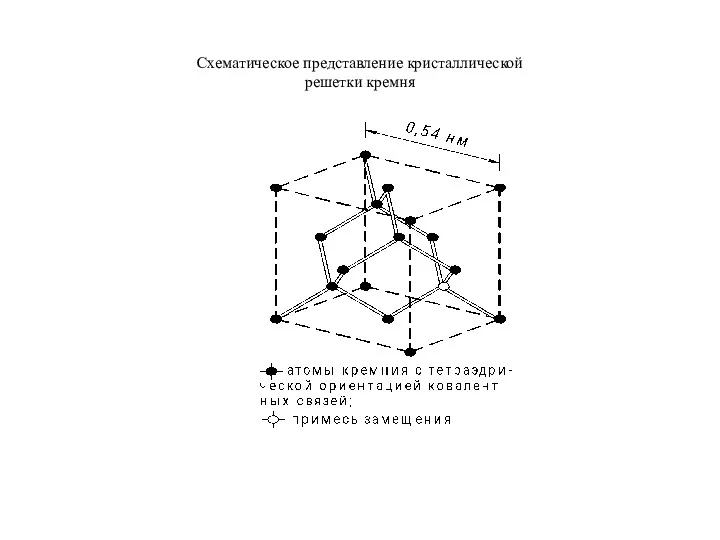

- 44. Схематическое представление кристаллической решетки кремня

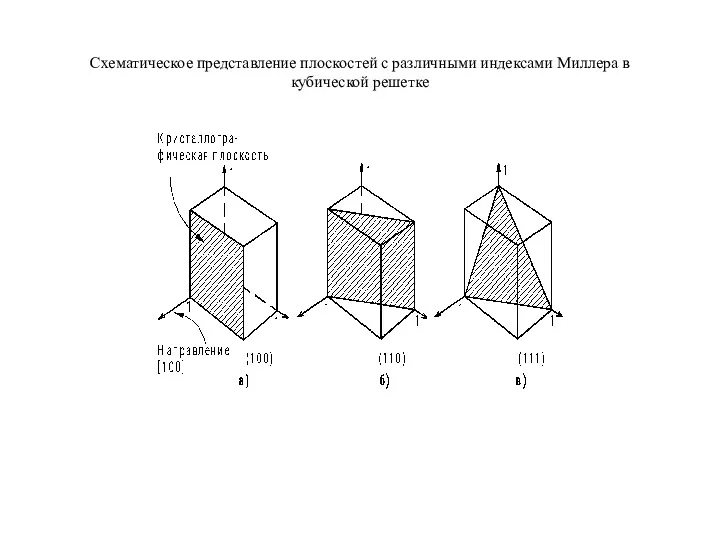

- 45. Схематическое представление плоскостей с различными индексами Миллера в кубической решетке

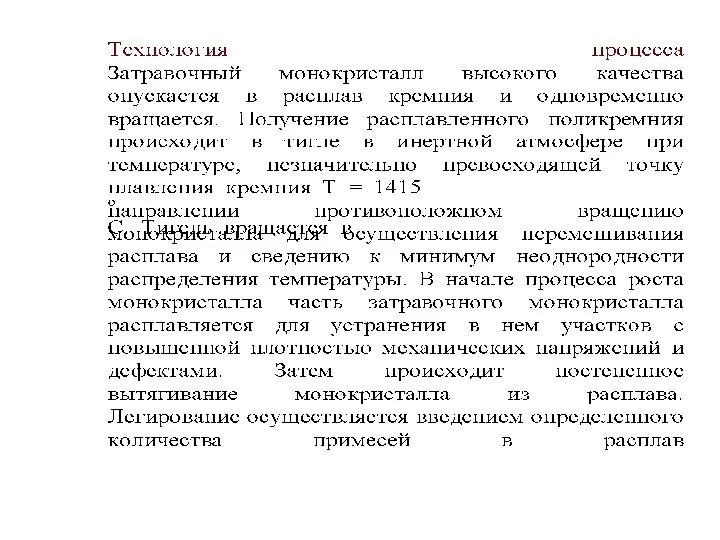

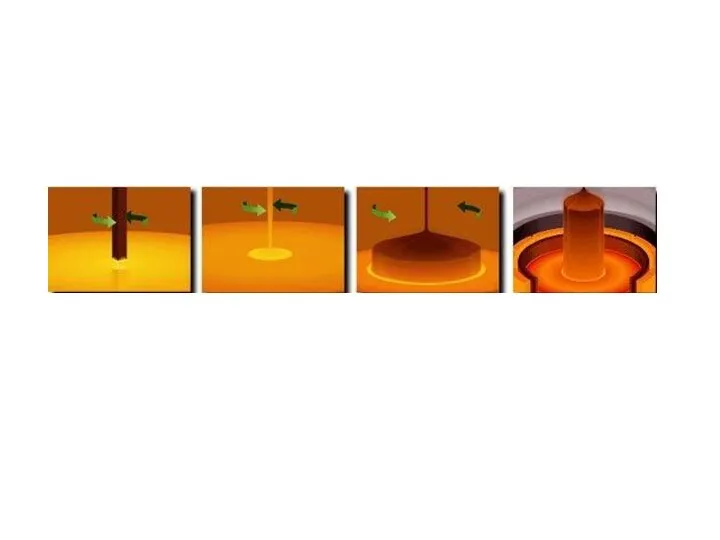

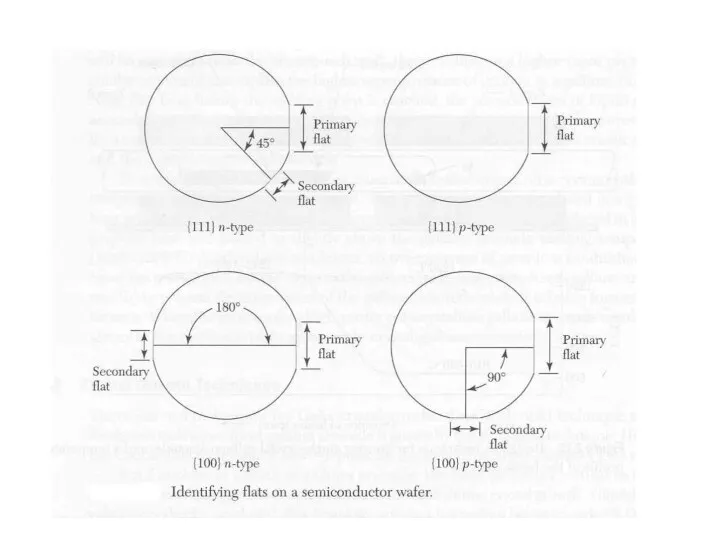

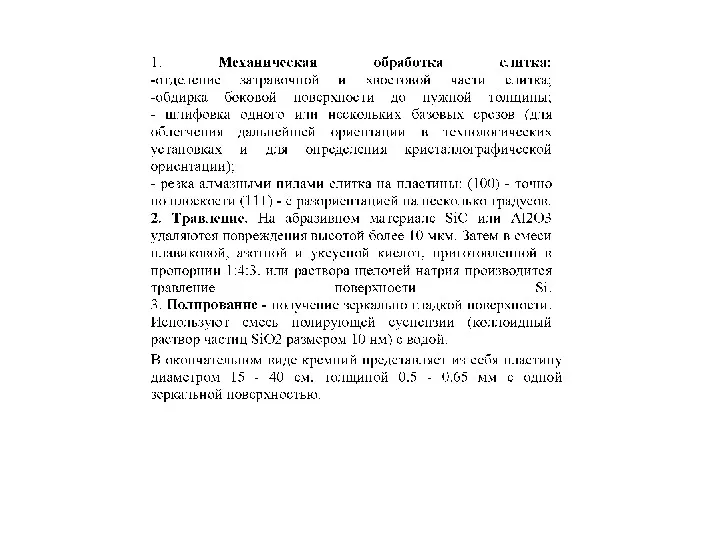

- 48. Процесс Чохральского для выращивания кристаллов кремния

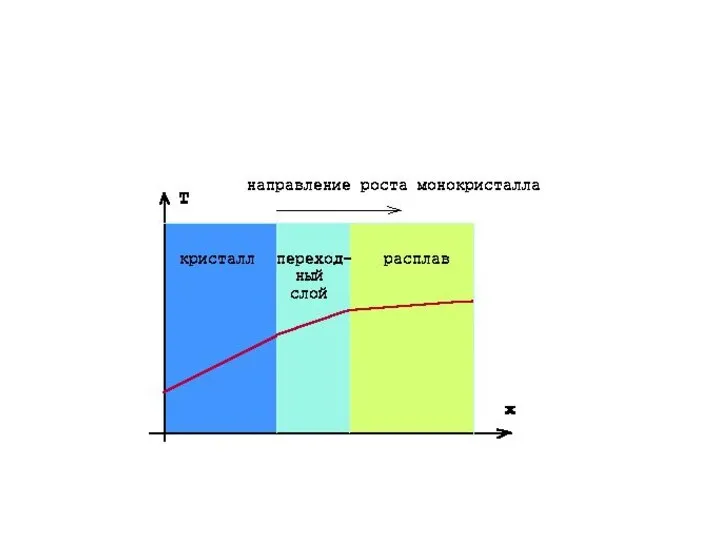

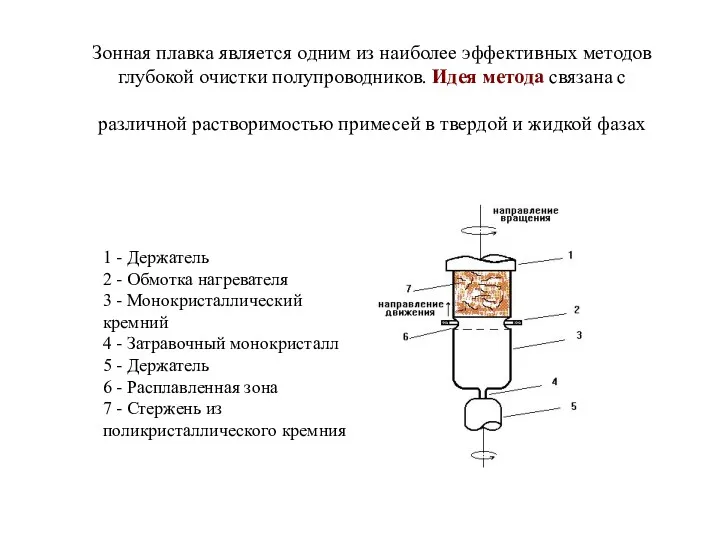

- 52. 1 - Держатель 2 - Обмотка нагревателя 3 - Монокристаллический кремний 4 - Затравочный монокристалл 5

- 58. Скачать презентацию

Задачи. Наплавка металла

Задачи. Наплавка металла досуг в подготовительной группе

досуг в подготовительной группе Виды информации. Методы поиска информации

Виды информации. Методы поиска информации Презентация Геодезическая дуга Струве

Презентация Геодезическая дуга Струве Техника оригами. Лисичка и заяц

Техника оригами. Лисичка и заяц Психопатология. Основные понятия психосоматики

Психопатология. Основные понятия психосоматики Основные средства предприятия

Основные средства предприятия Владимир Онуфриевич Ковалевский

Владимир Онуфриевич Ковалевский Яйца и яйцепродукты в кондитерском производстве

Яйца и яйцепродукты в кондитерском производстве Электронды - вакуумды шамдар

Электронды - вакуумды шамдар Оценка основных направлений совершенствования ресурсосбережения жилых помещений

Оценка основных направлений совершенствования ресурсосбережения жилых помещений Презентация1

Презентация1 Интегрированное занятие во второй младшей группе ( познание, художественное слово, художественное творчество) на тему Путешествие в осенний лес

Интегрированное занятие во второй младшей группе ( познание, художественное слово, художественное творчество) на тему Путешествие в осенний лес Сетевые технологии систем связи с коммутацией каналов

Сетевые технологии систем связи с коммутацией каналов Требования к развивающей предметно-пространственной среде.

Требования к развивающей предметно-пространственной среде. Франция на пути к абсолютизму

Франция на пути к абсолютизму Алты мүшелі гетероциклдердің туындылары: барбитураттар, қасиеті, медицинада колданылуы

Алты мүшелі гетероциклдердің туындылары: барбитураттар, қасиеті, медицинада колданылуы Структурирование проблем функционирования и развития НГХК

Структурирование проблем функционирования и развития НГХК ИСПОЛЬЗОВАНИЕ ПРИЕМОВ ТЕХНОЛОГИИ РАЗВИТИЯ КРИТИЧЕСКОГО МЫШЛЕНИЯ ДЛЯ ФОРМИРОВАНИЯ КЛЮЧЕВЫХ КОМПЕТЕНЦИЙ УЧАЩИХСЯ НА УРОКАХ ГЕОГРАФИИ

ИСПОЛЬЗОВАНИЕ ПРИЕМОВ ТЕХНОЛОГИИ РАЗВИТИЯ КРИТИЧЕСКОГО МЫШЛЕНИЯ ДЛЯ ФОРМИРОВАНИЯ КЛЮЧЕВЫХ КОМПЕТЕНЦИЙ УЧАЩИХСЯ НА УРОКАХ ГЕОГРАФИИ Мышление и деятельность. Потребности и интересы. Свобода и ответственность

Мышление и деятельность. Потребности и интересы. Свобода и ответственность Присутствие Иисуса с избытком восполняет любой недостаток

Присутствие Иисуса с избытком восполняет любой недостаток Органы дыхания

Органы дыхания Презентация День за днём

Презентация День за днём Рак шейки матки (клиника, диагностика, лечение)

Рак шейки матки (клиника, диагностика, лечение) Литература Древнего Рима периода распада полиса (конец II века до н.э. - 30-е годы до н.э.)

Литература Древнего Рима периода распада полиса (конец II века до н.э. - 30-е годы до н.э.) Ко Дню Матери.

Ко Дню Матери. Конструктивные элементы производственных зданий

Конструктивные элементы производственных зданий Птицы Владимирской области

Птицы Владимирской области