Содержание

- 2. Определение СБИС 2 Сверхбольшая интегральная схема (СБИС) – электронная схема, изготовленная на полупроводниковом кристалле, помещенная в

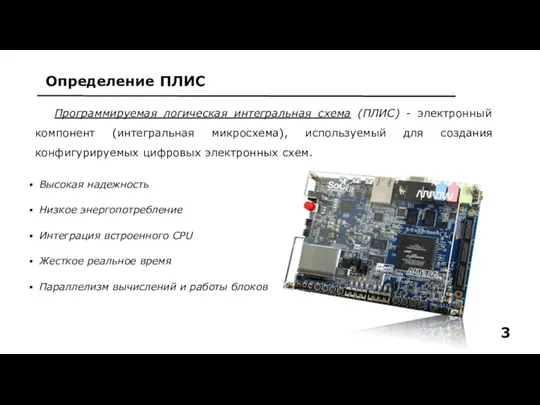

- 3. Определение ПЛИС 3 Программируемая логическая интегральная схема (ПЛИС) - электронный компонент (интегральная микросхема), используемый для создания

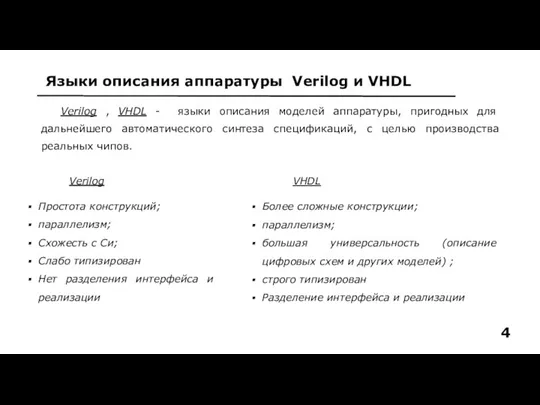

- 4. Языки описания аппаратуры Verilog и VHDL 4 Verilog , VHDL - языки описания моделей аппаратуры, пригодных

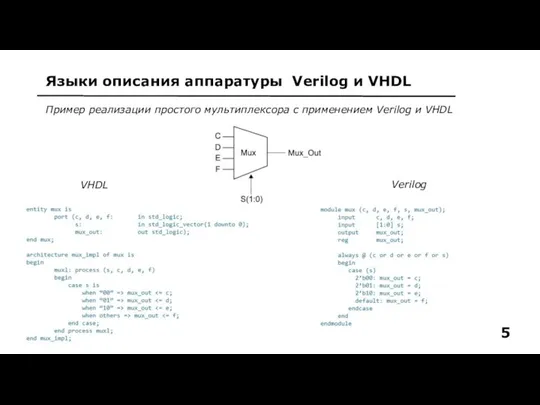

- 5. Языки описания аппаратуры Verilog и VHDL 5 Пример реализации простого мультиплексора с применением Verilog и VHDL

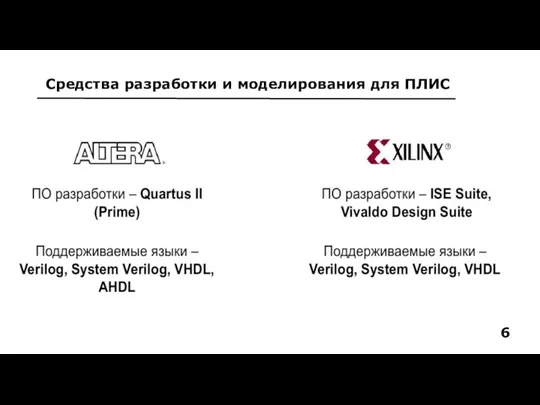

- 6. Средства разработки и моделирования для ПЛИС 6

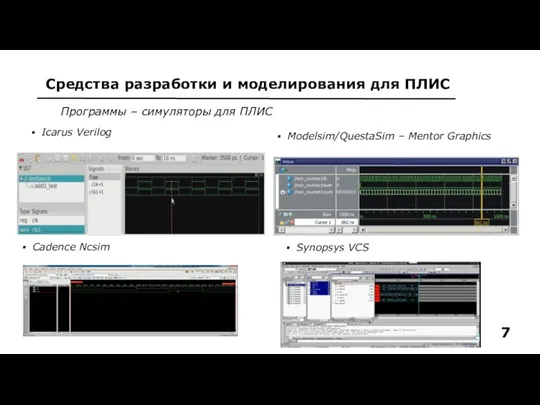

- 7. Средства разработки и моделирования для ПЛИС 7 Программы – симуляторы для ПЛИС Modelsim/QuestaSim – Mentor Graphics

- 8. Средства разработки и моделирования для ПЛИС 8 Intel Quartus Prime - для разработки дизайна систем на

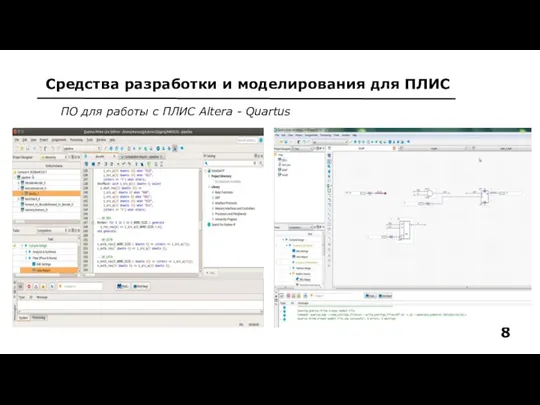

- 9. Средства разработки и моделирования для ПЛИС 8 ПО для работы с ПЛИС Altera - Quartus

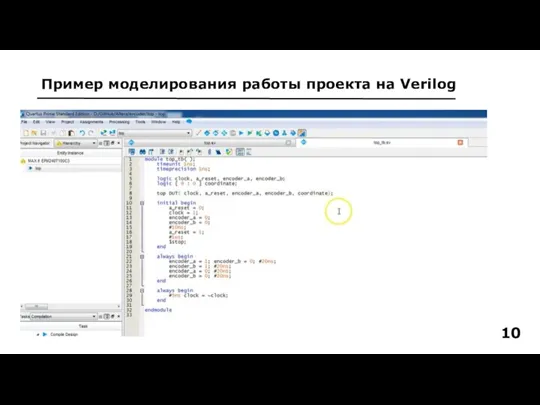

- 10. 10 Пример моделирования работы проекта на Verilog

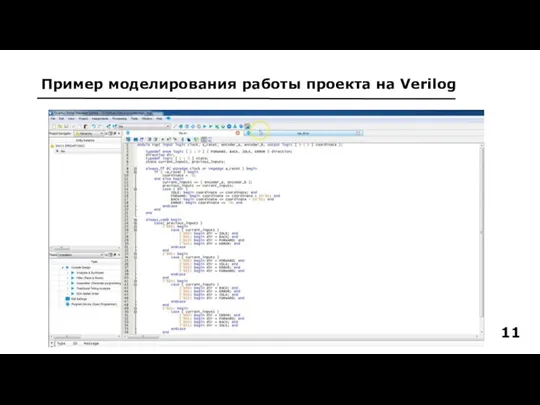

- 11. 11 Пример моделирования работы проекта на Verilog

- 12. 12 Пример моделирования работы проекта на Verilog

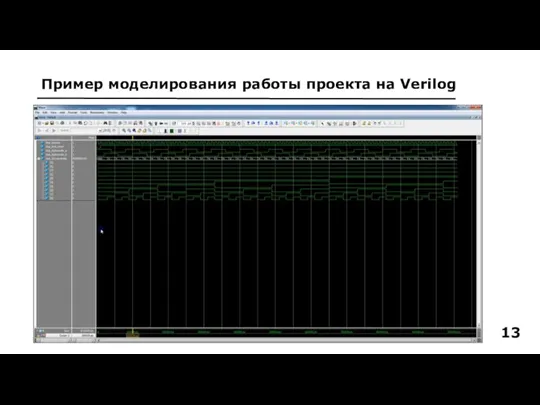

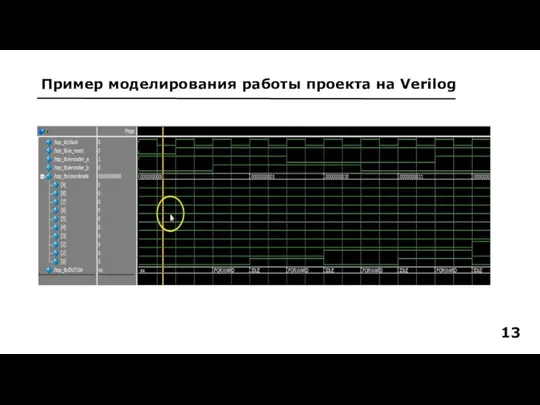

- 13. 13 Пример моделирования работы проекта на Verilog

- 14. 13 Пример моделирования работы проекта на Verilog

- 16. Скачать презентацию

Избирательная и партийная системы

Избирательная и партийная системы Понятие о специальных сталях и сплавах, эффективность их применения

Понятие о специальных сталях и сплавах, эффективность их применения Мастер-класс (презентация) для родителей воспитанников с нарушением речи.

Мастер-класс (презентация) для родителей воспитанников с нарушением речи. Сестринский процесс при заболеваниях прямой кишки

Сестринский процесс при заболеваниях прямой кишки Экологический проект Почему листья разной формы?

Экологический проект Почему листья разной формы? Внеурочная деятельность неотъемлемая часть образовательного процесса, направленная на воспитание и социализацию личности.

Внеурочная деятельность неотъемлемая часть образовательного процесса, направленная на воспитание и социализацию личности. Металлические конструкции. Сварные соединения. (Лекция 7)

Металлические конструкции. Сварные соединения. (Лекция 7) День науки.

День науки. Развитие логического мышления у старших дошкольников через развивающие игры

Развитие логического мышления у старших дошкольников через развивающие игры Общая классификация микропроцессорных средств

Общая классификация микропроцессорных средств МОНИТОРИНГ обеспечения антитеррористической защищенности МБДОУ

МОНИТОРИНГ обеспечения антитеррористической защищенности МБДОУ Лингводидактические принципы обучения русскому языку

Лингводидактические принципы обучения русскому языку Устройства для нагревания воздуха. Очистка вентиляционного воздуха. Системы местной вентиляции. (Лекция 8)

Устройства для нагревания воздуха. Очистка вентиляционного воздуха. Системы местной вентиляции. (Лекция 8) Внутренние воды Африки

Внутренние воды Африки Education in Britain

Education in Britain Человек – уникальный вид органического мира. Тема 8

Человек – уникальный вид органического мира. Тема 8 Электрическая система всего автомобиля C7H

Электрическая система всего автомобиля C7H Преступления против правосудия

Преступления против правосудия Общегородская программа Начальная управленческая подготовка

Общегородская программа Начальная управленческая подготовка Афанасий Фет 1820 - 1892

Афанасий Фет 1820 - 1892 Презентация по лепке для воспитателей

Презентация по лепке для воспитателей Эксплуатация скважин в осложненных условиях

Эксплуатация скважин в осложненных условиях Северный Кавказ

Северный Кавказ Уход за бейбиком

Уход за бейбиком Проект на тему Путешествие по сказкам

Проект на тему Путешествие по сказкам Научно-исследовательская работа в группе Следопыт

Научно-исследовательская работа в группе Следопыт Кислородно-конвертерный процесс

Кислородно-конвертерный процесс Климат

Климат