Слайд 2

Виды узлов ЭВМ

Узлы ЭВМ:

комбинационные:

выходные сигналы зависят только от входных сигналов;

накапливающие:

выходные сигналы зависят

не только

от действующих входных сигналов, но и от поступавших ранее.

Слайд 3

Комбинационные узлы

Комбинационные узлы:

Шифратор/Дешифратор

Сумматор по модулю 2

Мультиплексор/Демультиплексор

Сумматор

Программируемая логическая матрица

И др.

Слайд 4

Накапливающие узлы

Накапливающие узлы:

Триггер

Регистр

Счётчики

И др.

Слайд 5

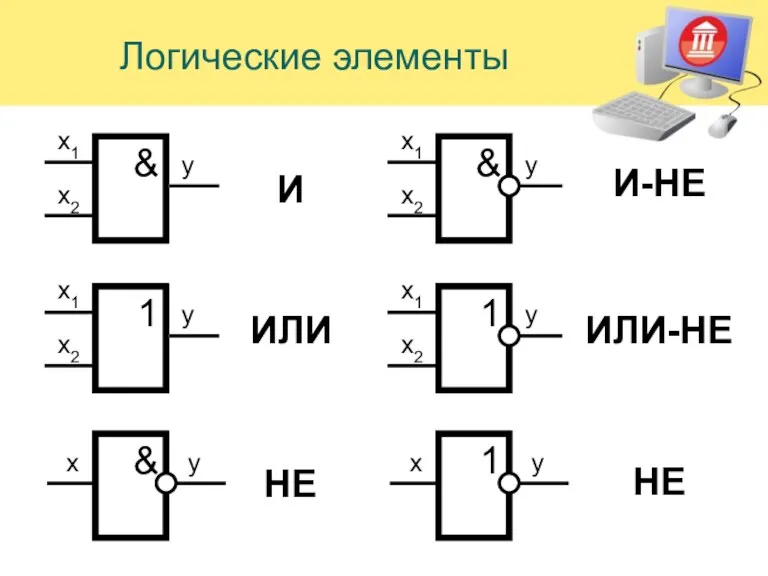

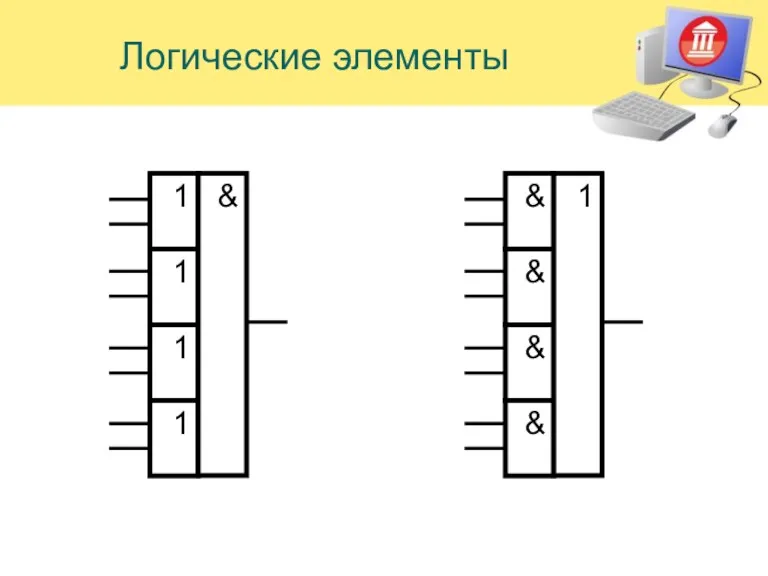

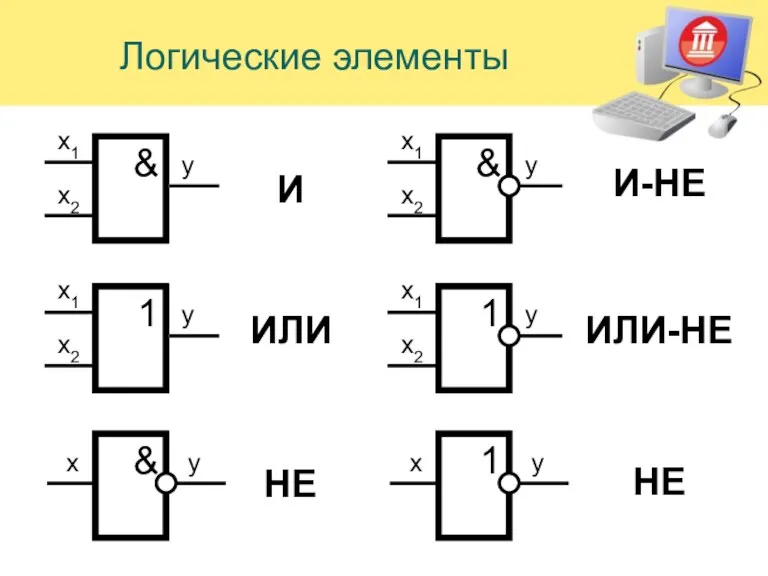

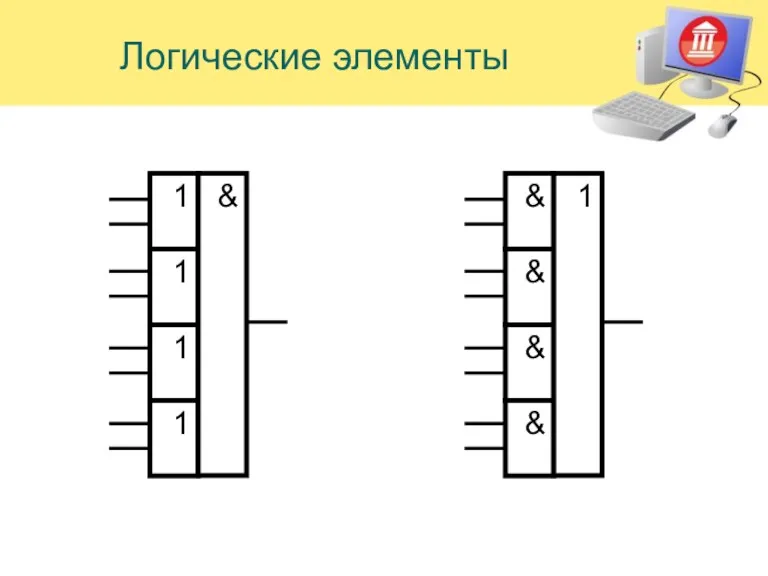

Логические элементы

ИЛИ

И

НЕ

ИЛИ-НЕ

И-НЕ

НЕ

Слайд 6

Слайд 7

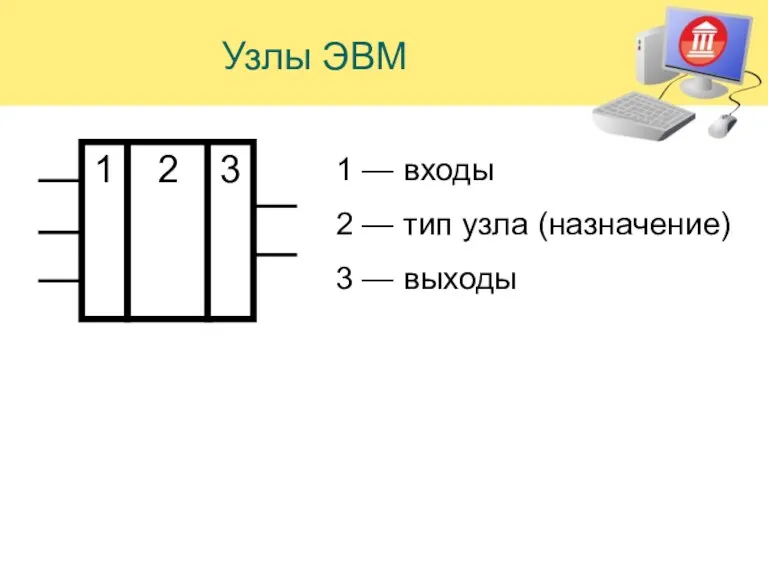

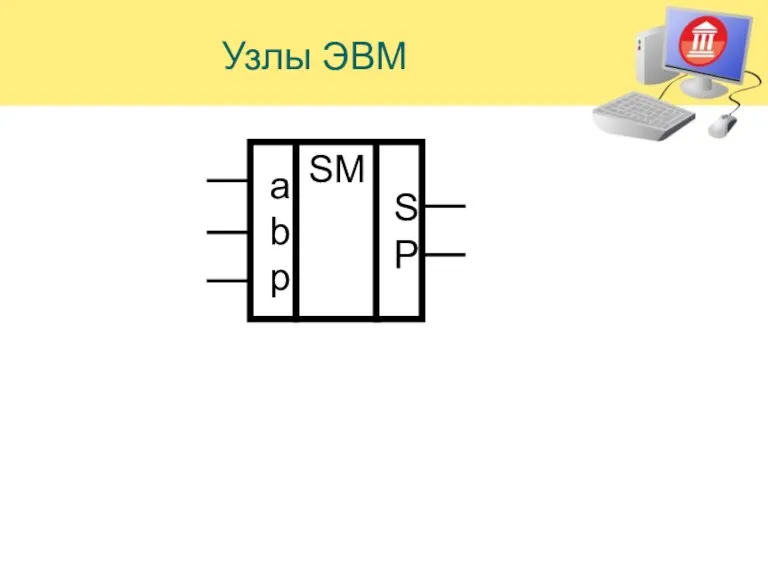

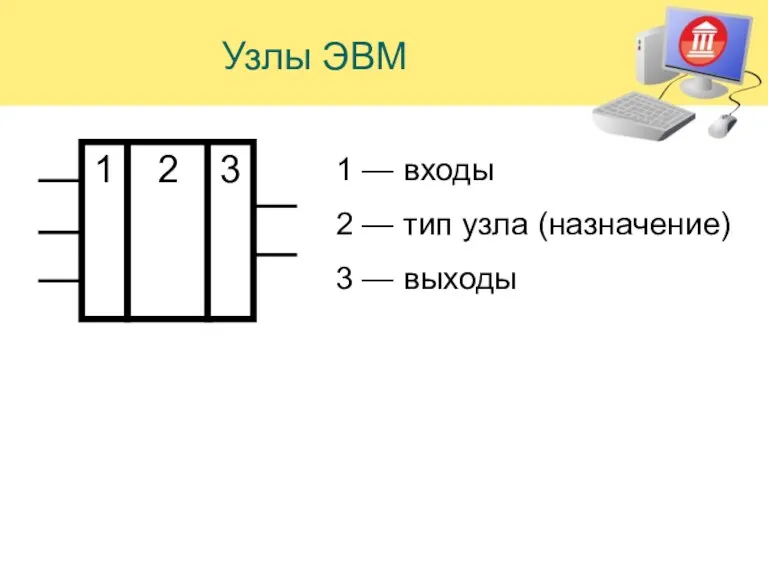

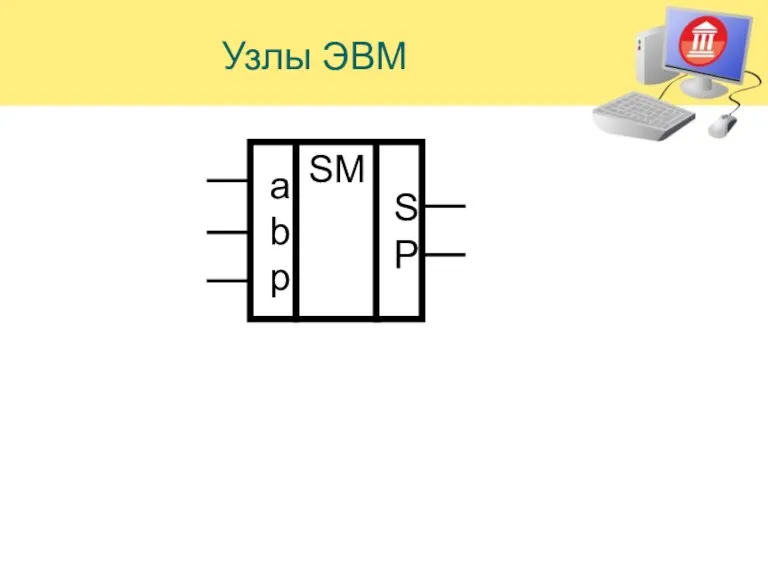

Узлы ЭВМ

1 — входы

2 — тип узла (назначение)

3 — выходы

Слайд 8

Слайд 9

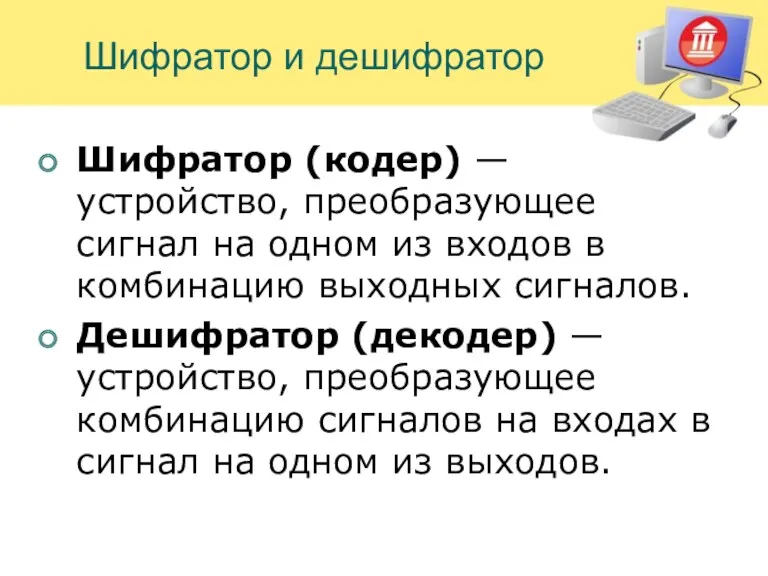

Шифратор и дешифратор

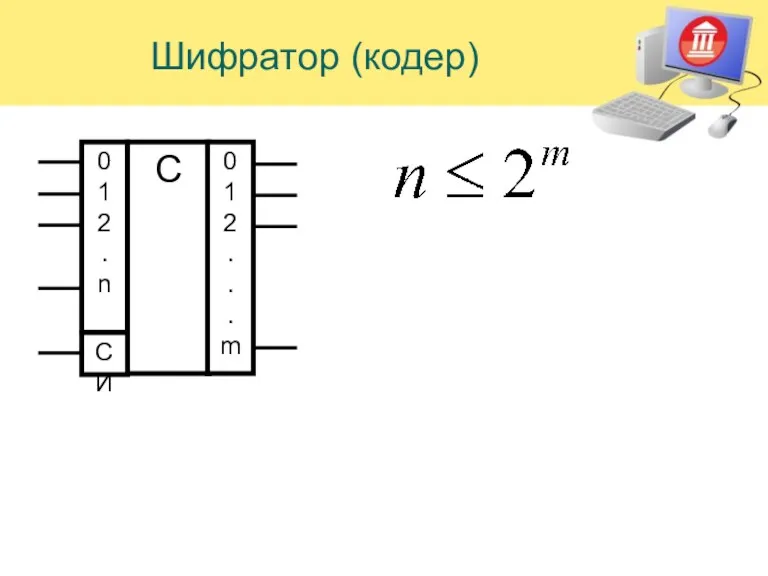

Шифратор (кодер) —

устройство, преобразующее сигнал на одном из входов в

комбинацию выходных сигналов.

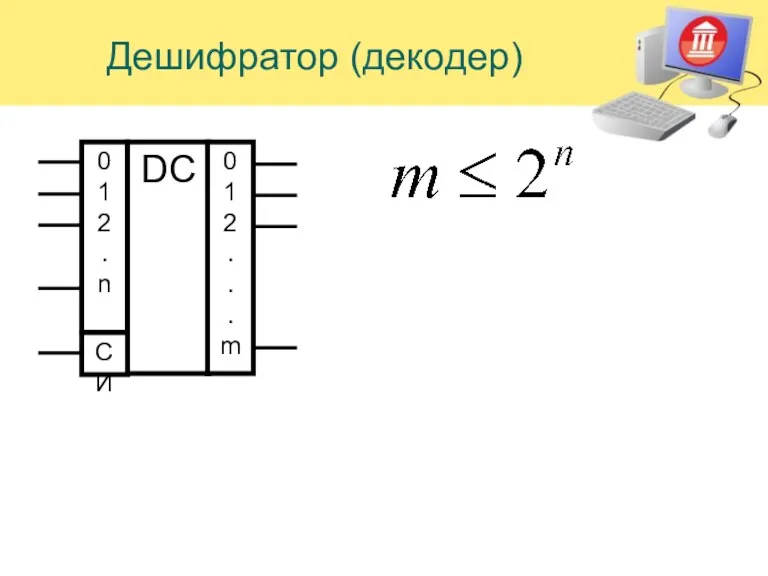

Дешифратор (декодер) — устройство, преобразующее комбинацию сигналов на входах в сигнал на одном из выходов.

Слайд 10

Слайд 11

Слайд 12

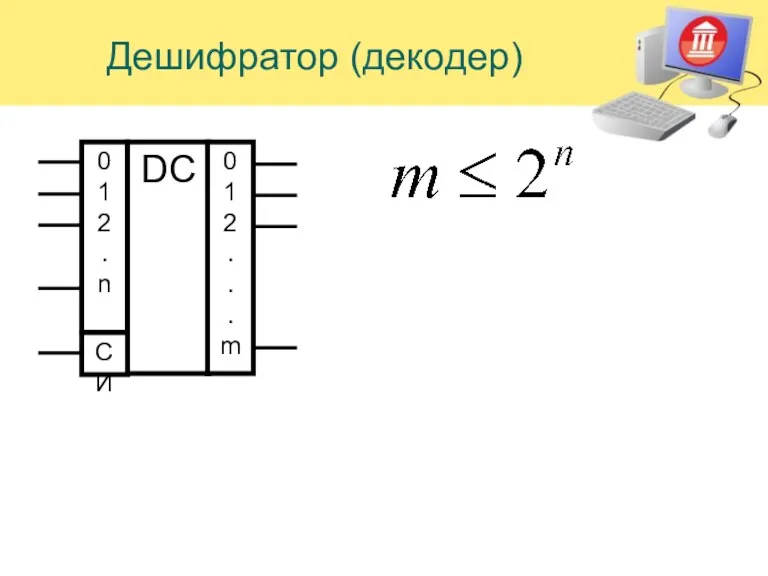

Дешифратор (декодер)

x1 x2 x3

&

&

&

&

&

&

&

&

Слайд 13

Дешифратор (декодер)

x1 x2 x3

&

&

&

&

&

&

&

&

0

1

2

3

4

5

6

7

Слайд 14

Слайд 15

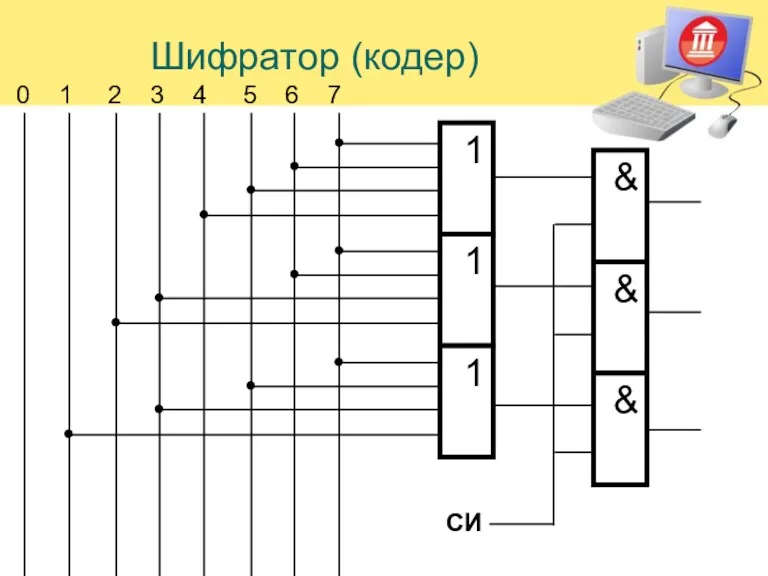

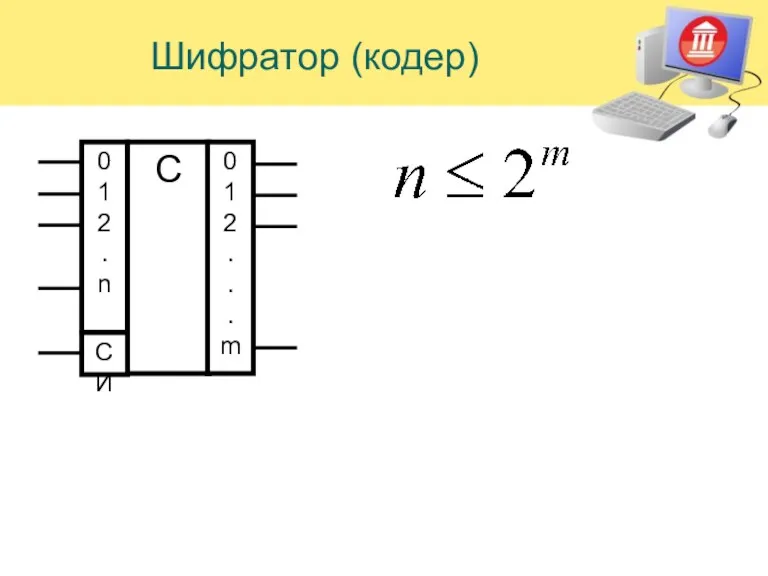

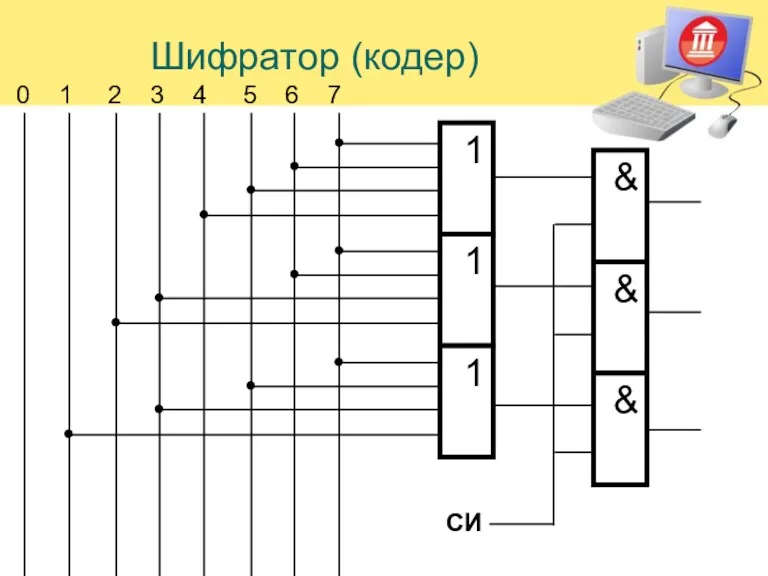

Шифратор (кодер)

0 1 2 3 4 5 6 7

1

1

1

&

&

&

СИ

Слайд 16

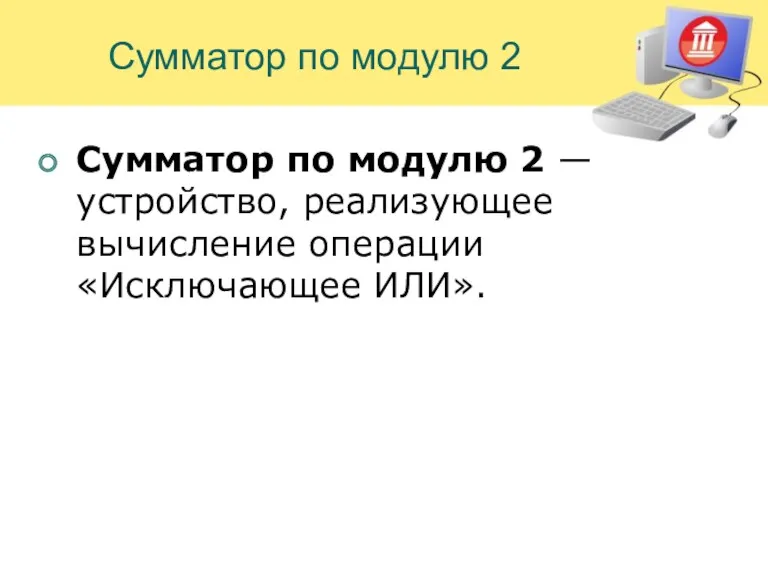

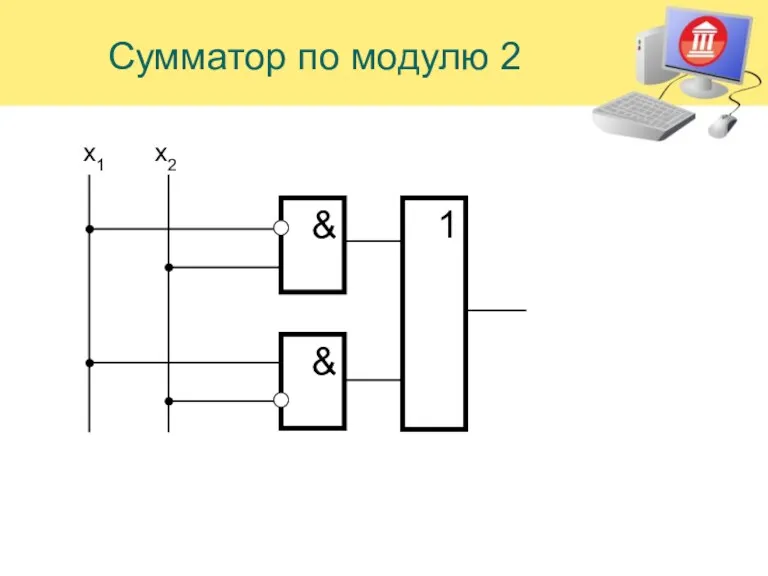

Сумматор по модулю 2

Сумматор по модулю 2 —

устройство, реализующее вычисление операции «Исключающее

ИЛИ».

Слайд 17

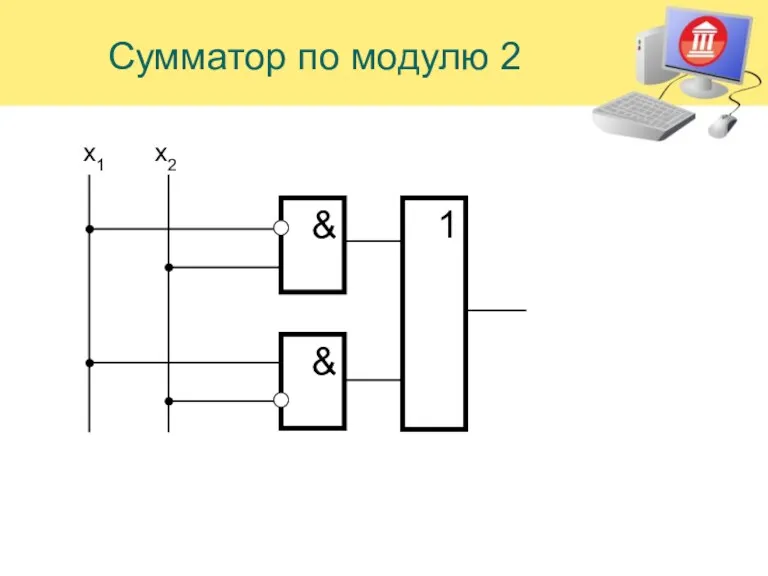

Сумматор по модулю 2

x1 x2

&

&

1

Слайд 18

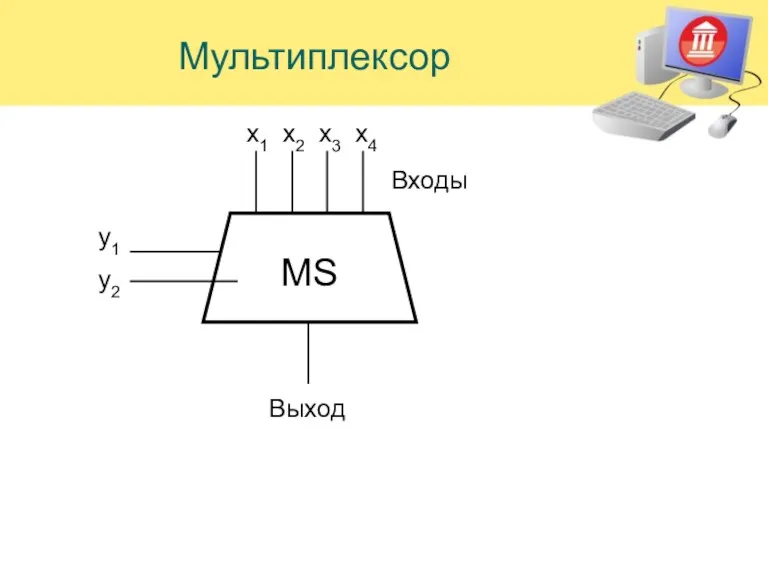

Мультиплексор и демультиплексор

Мультиплексор — устройство, обеспечивающее подключение одного из нескольких входов к

выходу.

Демультиплексор — устройство, обеспечивающее подключение входа к одному из нескольких выходов.

Слайд 19

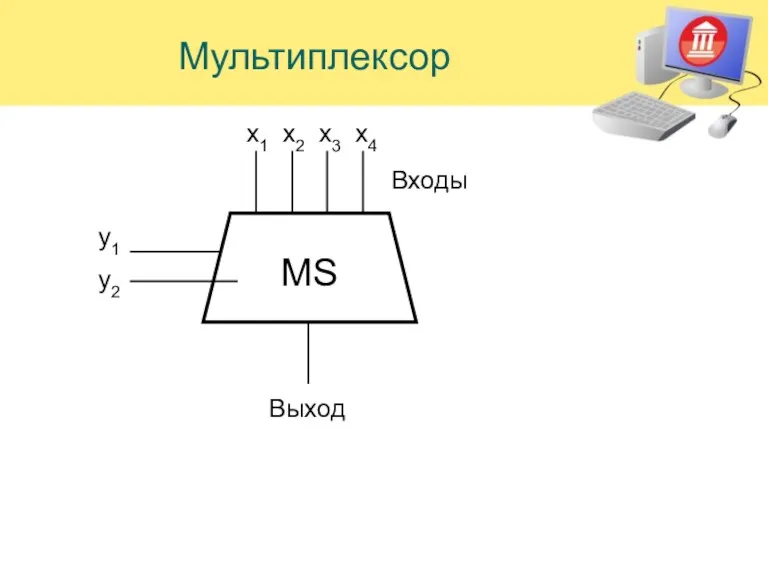

Мультиплексор

MS

Входы

x1 x2 x3 x4

y1

y2

Выход

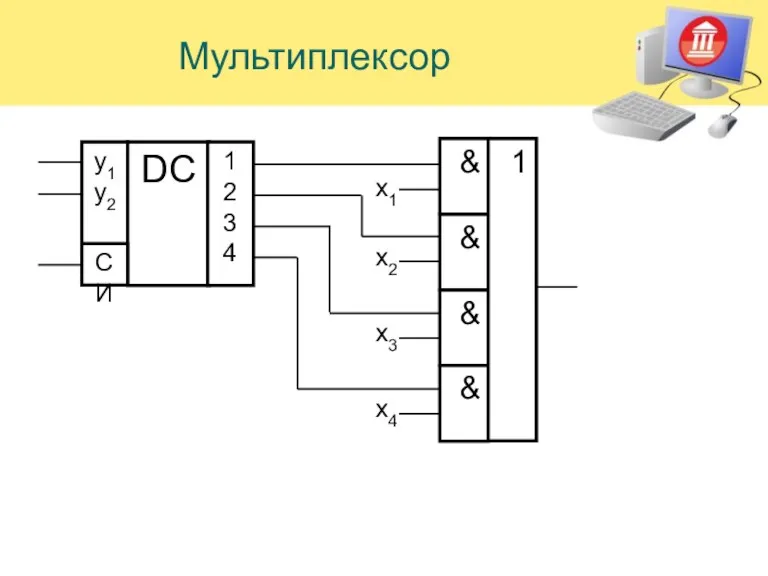

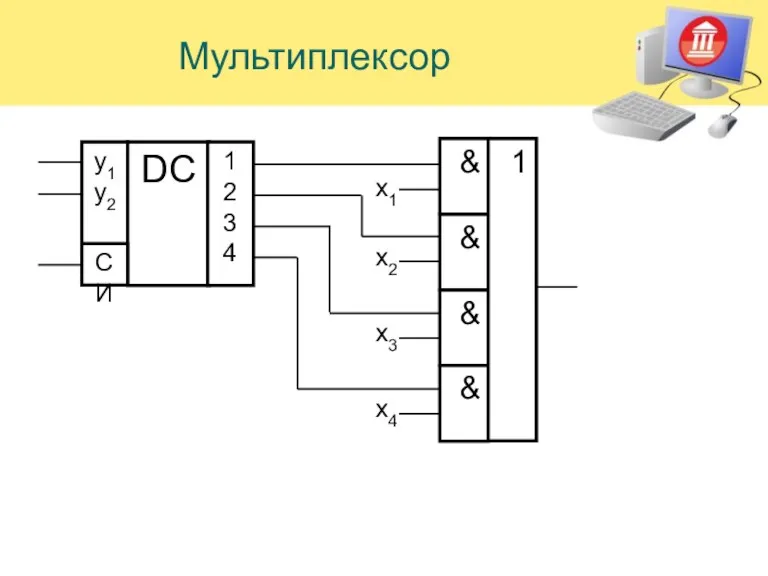

Слайд 20

Мультиплексор

y1

y2

DC

1

2

3

4

СИ

&

&

&

&

1

x1

x2

x3

x4

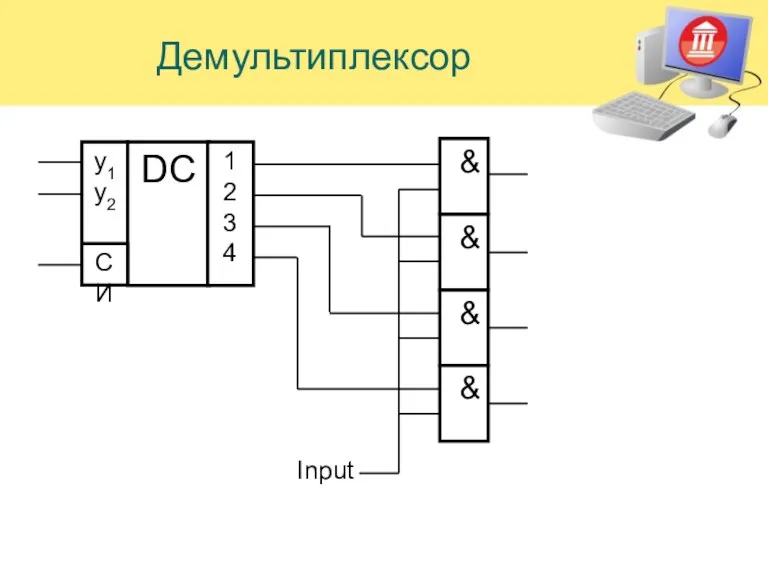

Слайд 21

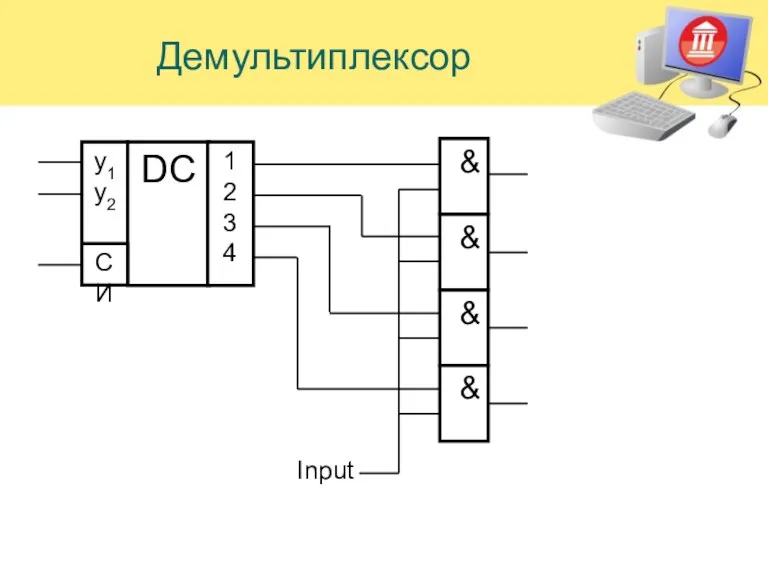

Демультиплексор

y1

y2

DC

1

2

3

4

СИ

&

&

&

&

Input

Слайд 22

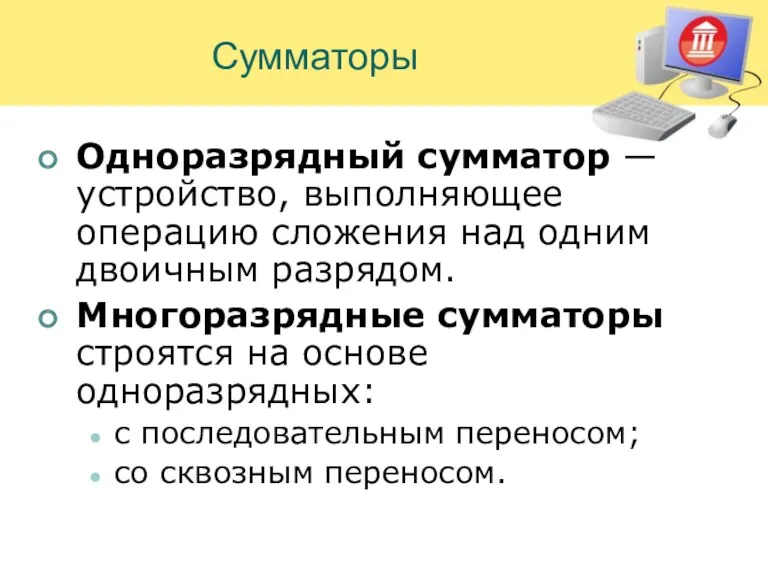

Сумматоры

Одноразрядный сумматор — устройство, выполняющее операцию сложения над одним двоичным разрядом.

Многоразрядные сумматоры

строятся на основе одноразрядных:

с последовательным переносом;

со сквозным переносом.

Слайд 23

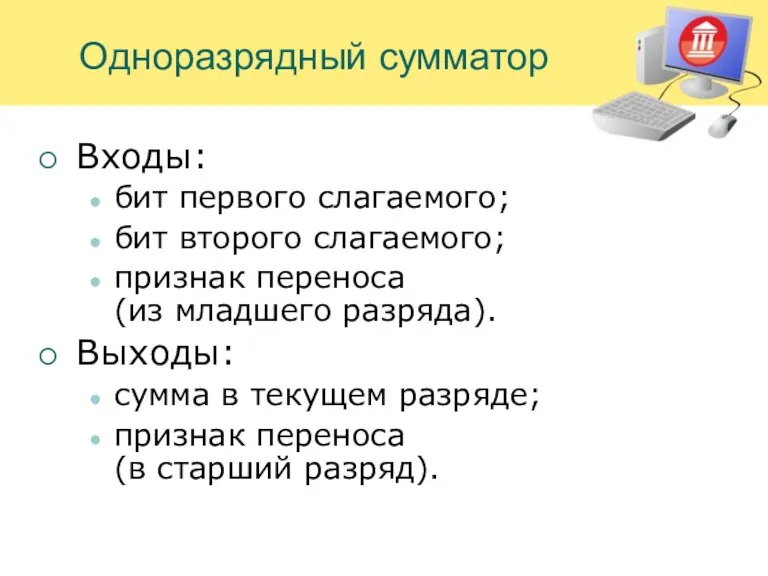

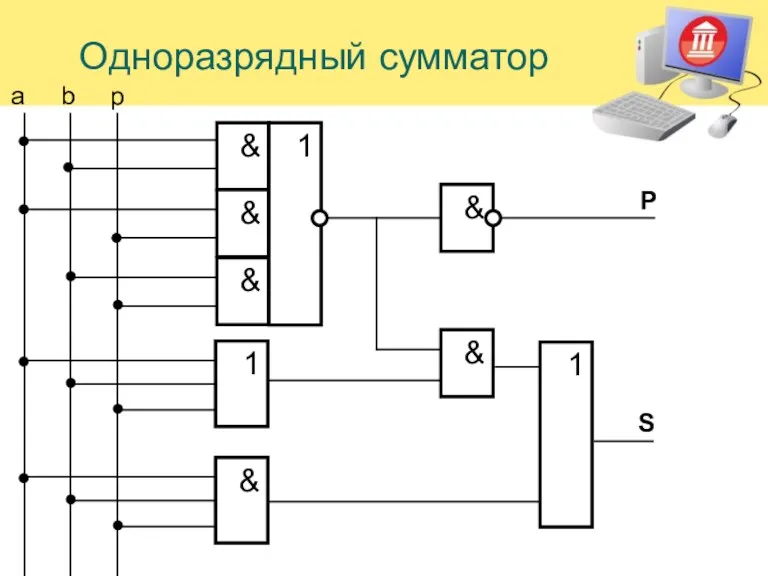

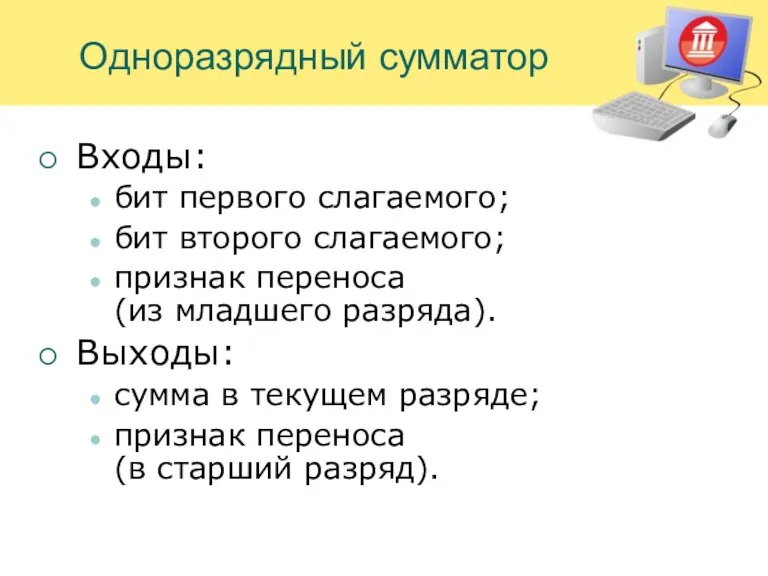

Одноразрядный сумматор

Входы:

бит первого слагаемого;

бит второго слагаемого;

признак переноса

(из младшего разряда).

Выходы:

сумма в текущем

разряде;

признак переноса

(в старший разряд).

Слайд 24

Слайд 25

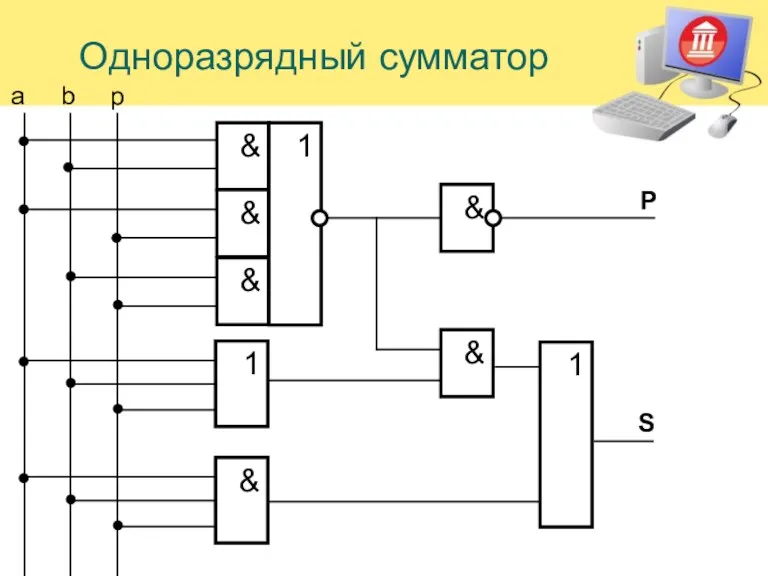

Одноразрядный сумматор

a b p

&

&

&

1

&

1

&

&

1

S

P

Слайд 26

Слайд 27

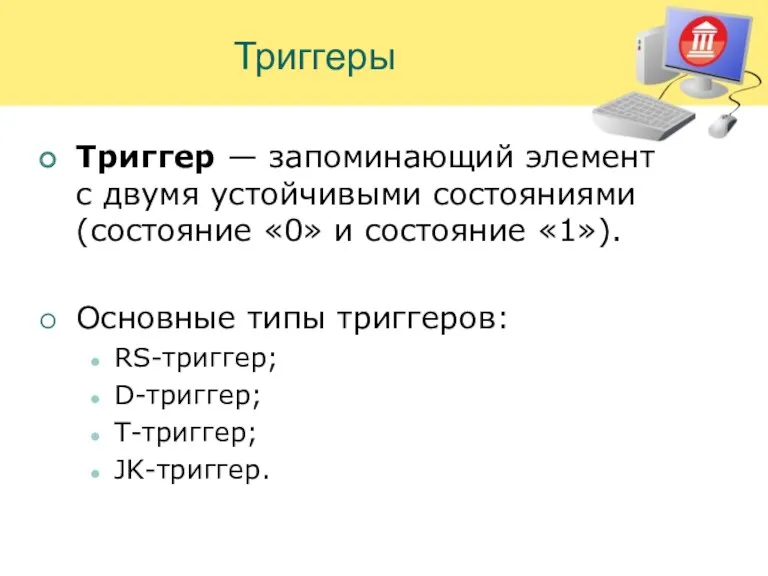

Триггеры

Триггер — запоминающий элемент

с двумя устойчивыми состояниями (состояние «0» и состояние «1»).

Основные

типы триггеров:

RS-триггер;

D-триггер;

T-триггер;

JK-триггер.

Слайд 28

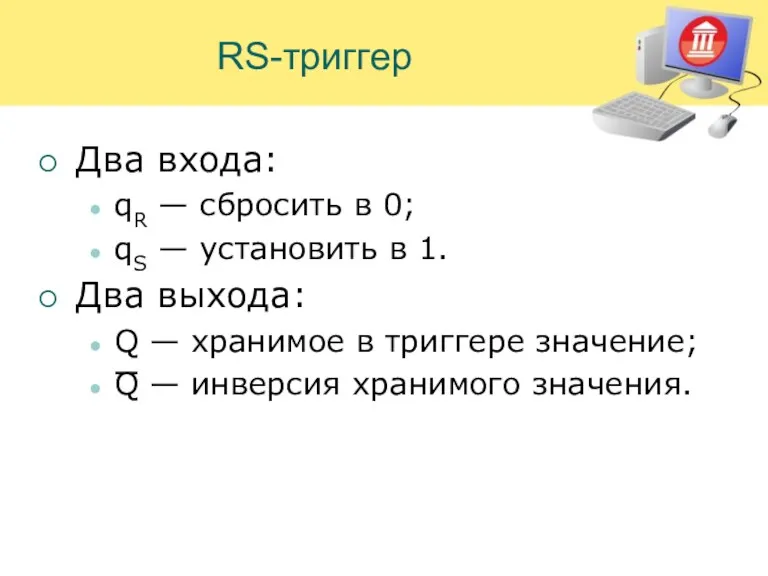

RS-триггер

Два входа:

qR — сбросить в 0;

qS — установить в 1.

Два выхода:

Q — хранимое в

триггере значение;

Q — инверсия хранимого значения.

Слайд 29

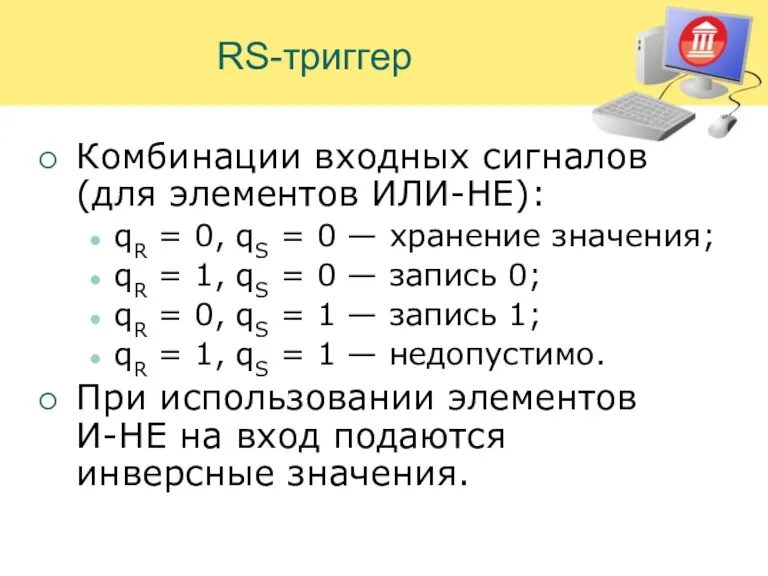

RS-триггер

Комбинации входных сигналов (для элементов ИЛИ-НЕ):

qR = 0, qS = 0 —

хранение значения;

qR = 1, qS = 0 — запись 0;

qR = 0, qS = 1 — запись 1;

qR = 1, qS = 1 — недопустимо.

При использовании элементов

И-НЕ на вход подаются

инверсные значения.

Слайд 30

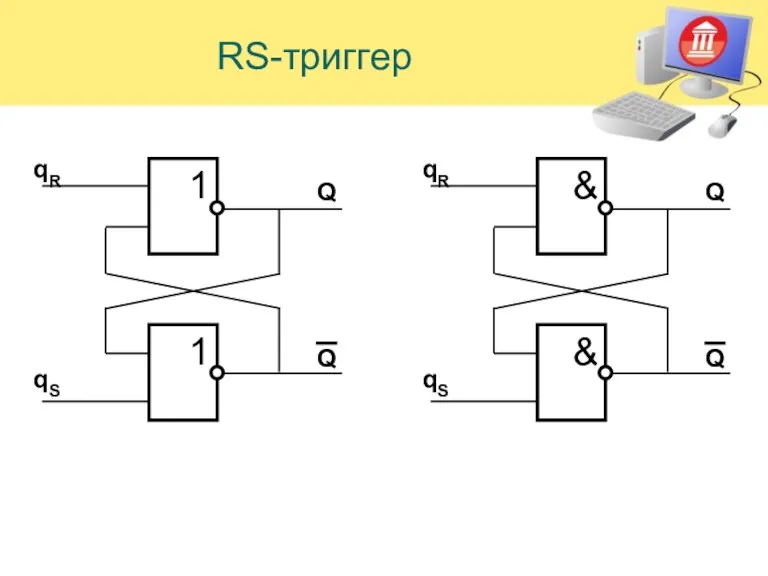

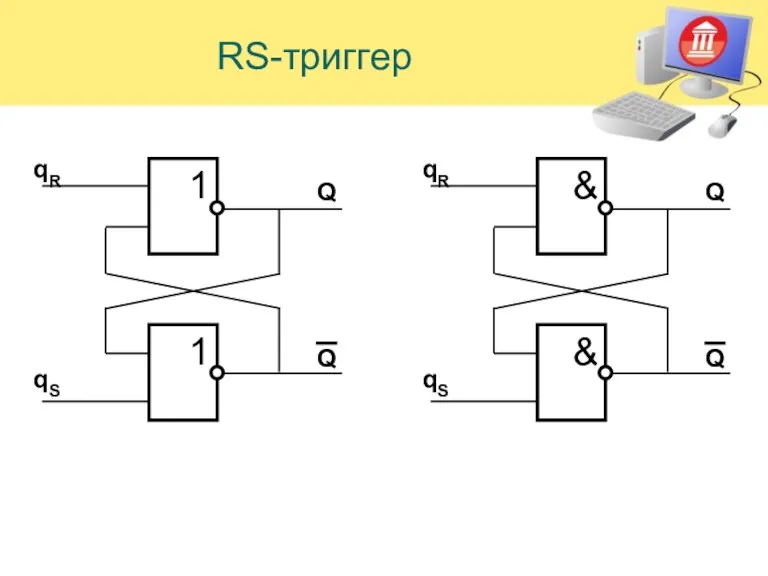

RS-триггер

1

1

qR

qS

Q

Q

&

&

qR

qS

Q

Q

Слайд 31

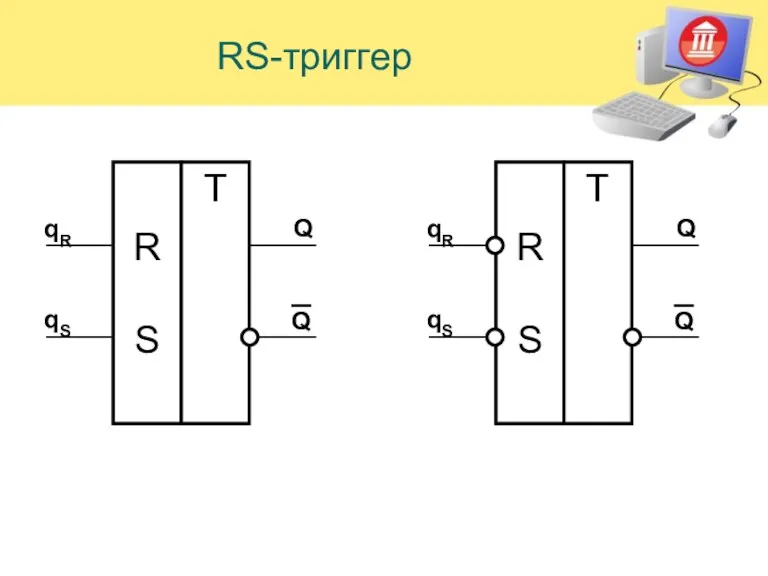

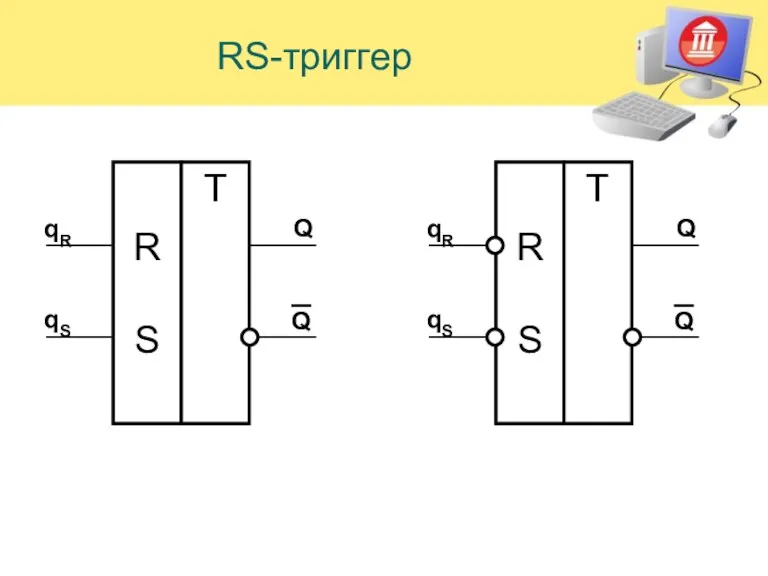

RS-триггер

R

S

T

qR

qS

Q

Q

R

S

T

qR

qS

Q

Q

Слайд 32

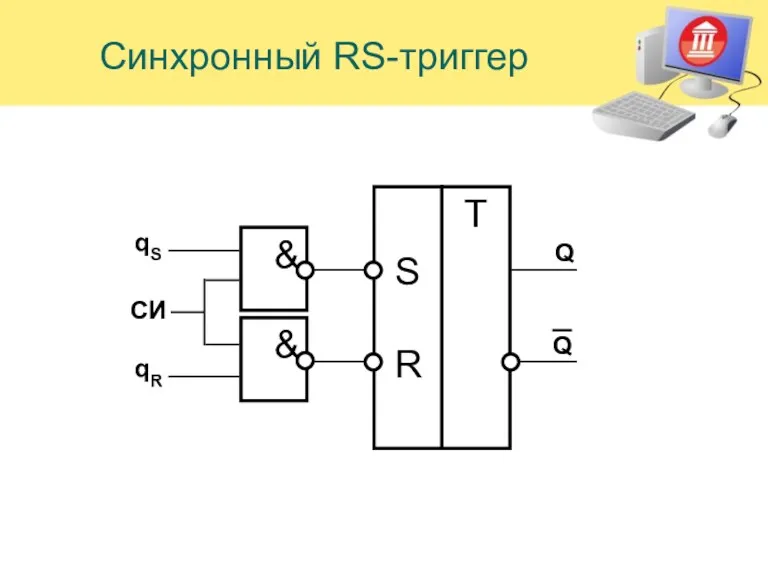

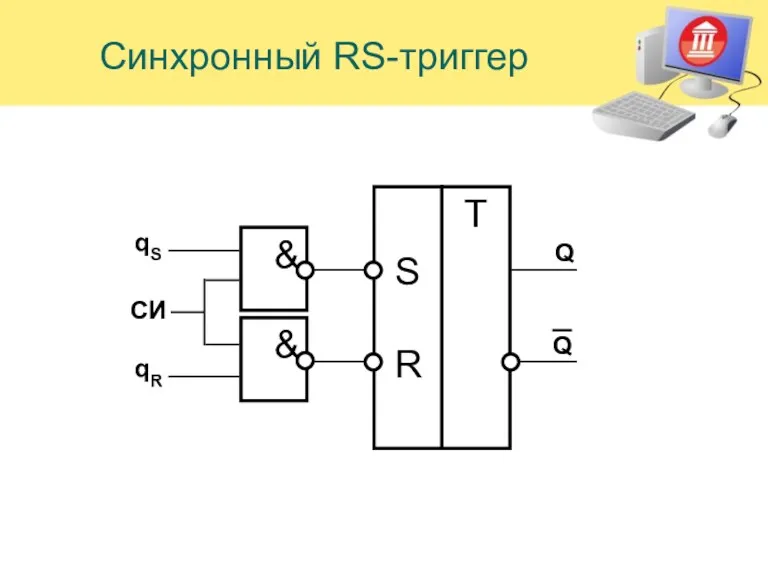

Синхронный RS-триггер

S

R

T

Q

Q

&

&

qS

qR

СИ

Слайд 33

Двухтактный RS-триггер

S

С

R

T

2

Q2

S

С

R

T

1

Q1

qS1

qR1

qS2

qR2

СИ

&

Слайд 34

Двухтактный RS-триггер

S

С

R

TT

Q

qS

qR

СИ

Q

Слайд 35

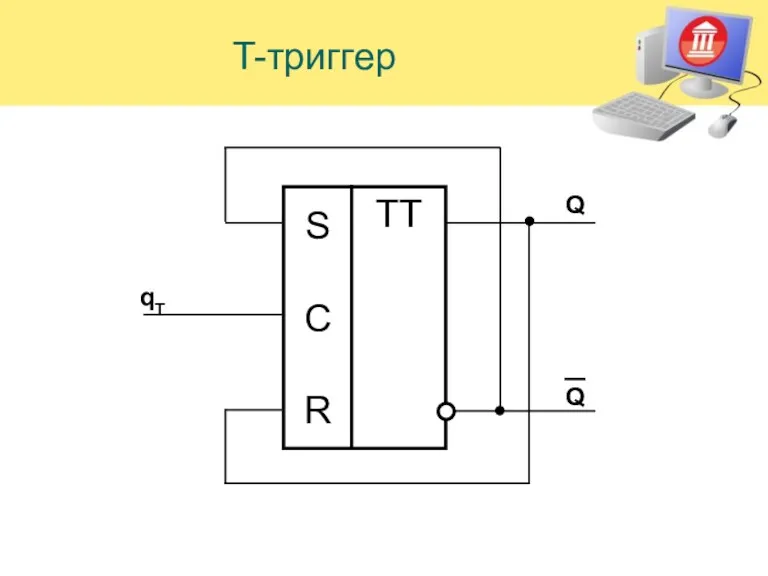

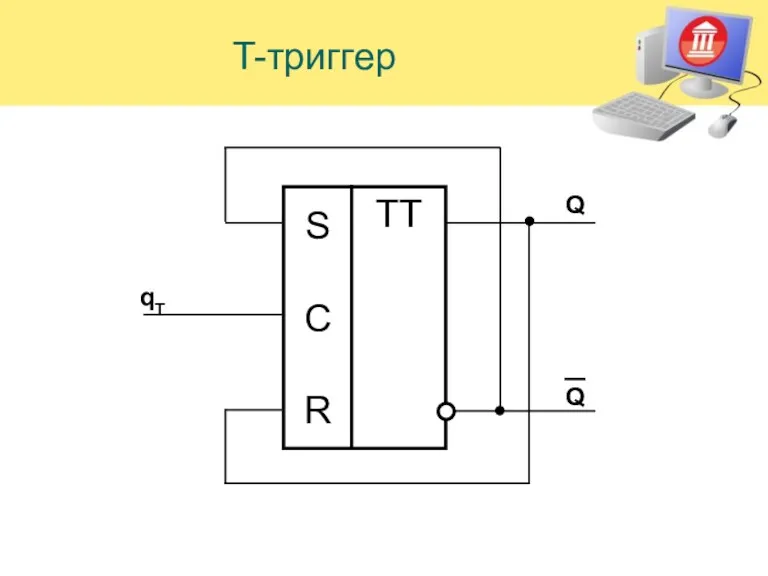

T-триггер

Один управляющий вход:

единичный сигнал на входе переводит T-триггер

в противоположное состояние.

Слайд 36

Слайд 37

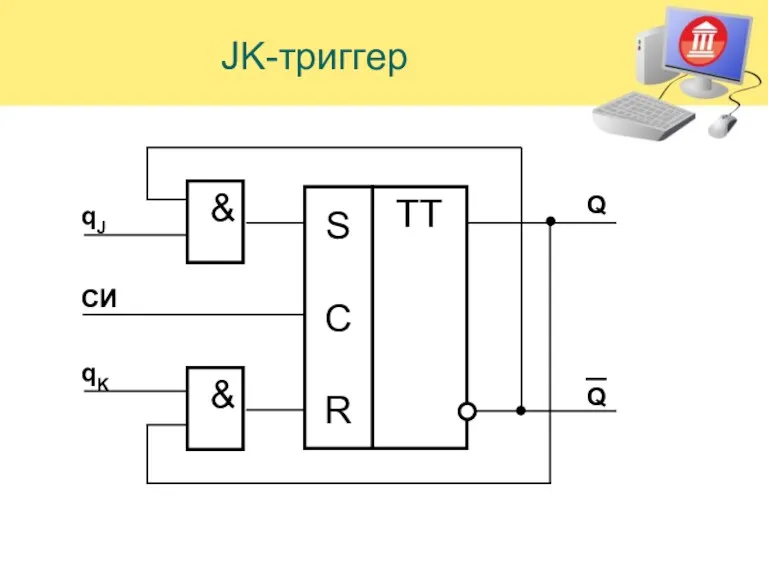

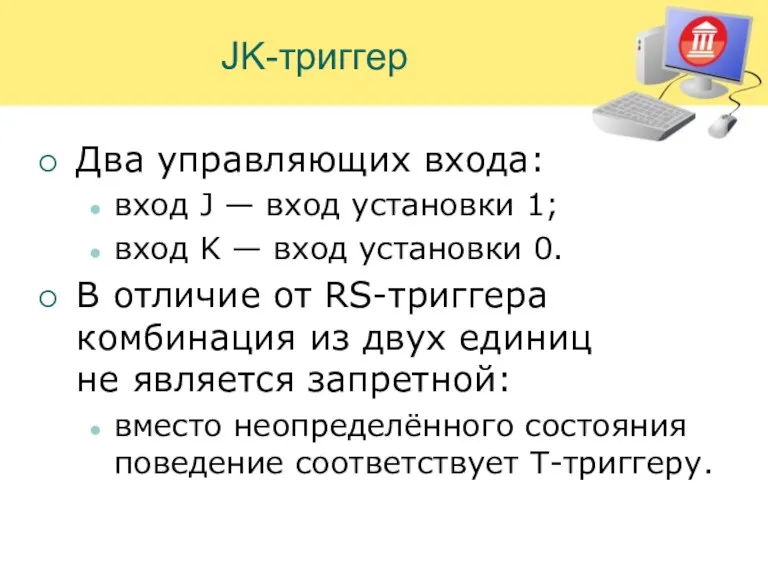

JK-триггер

Два управляющих входа:

вход J — вход установки 1;

вход K — вход установки 0.

В

отличие от RS-триггера комбинация из двух единиц

не является запретной:

вместо неопределённого состояния поведение соответствует T-триггеру.

Слайд 38

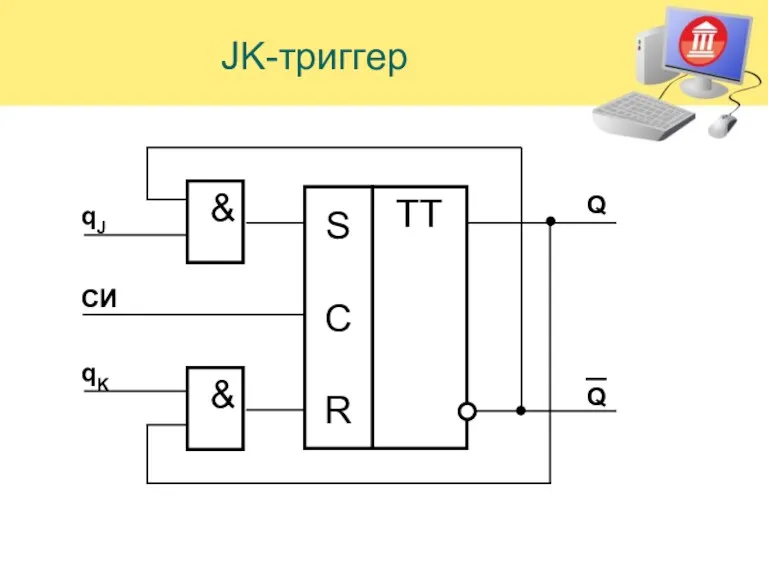

JK-триггер

S

С

R

TT

Q

qJ

Q

&

СИ

&

qK

Слайд 39

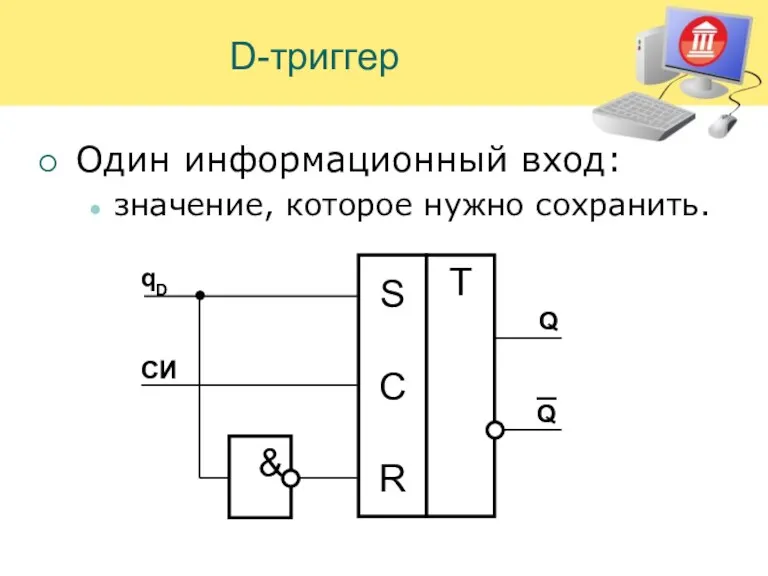

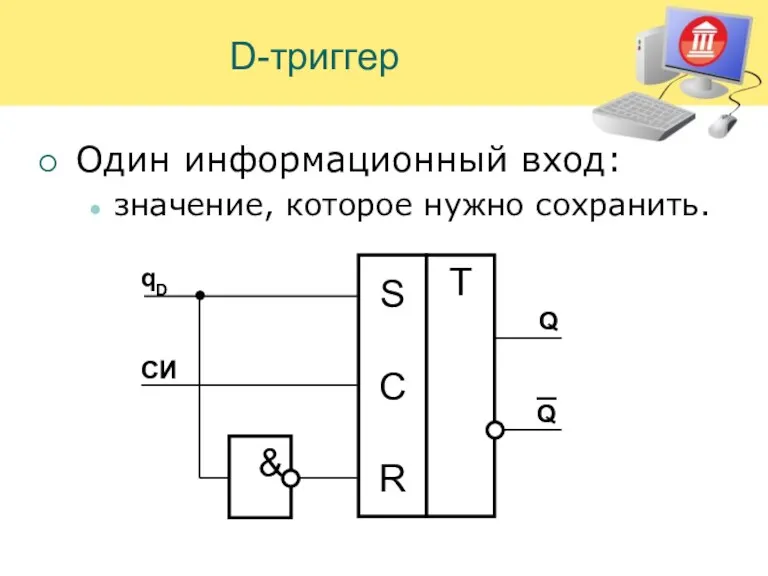

D-триггер

Один информационный вход:

значение, которое нужно сохранить.

S

C

R

T

СИ

qD

Q

Q

&

Слайд 40

Регистры и счётчики

Регистр — устройство хранения многоразрядных значений.

Счётчик — устройство хранения,

которое по каждому

сигналу

изменяет хранимый код

(как правило, многоразрядный).

Моря как крупные природные комплексы

Моря как крупные природные комплексы Заучивание стихов, скороговорок, потешек с детьми дошкольного возраста с ОНР и ЗПР

Заучивание стихов, скороговорок, потешек с детьми дошкольного возраста с ОНР и ЗПР Астраханское ханство

Астраханское ханство Проектная деятельность учащихся на уроках музыки

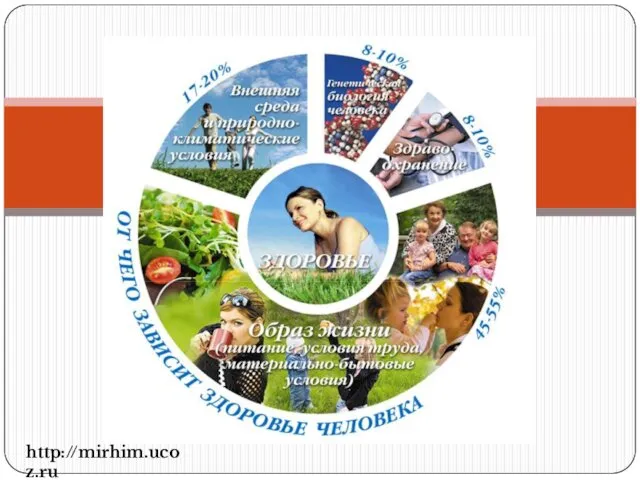

Проектная деятельность учащихся на уроках музыки От чего зависит здоровье человека. Блиц-опрос. Мы за здоровый образ жизни!

От чего зависит здоровье человека. Блиц-опрос. Мы за здоровый образ жизни! Применение активных методов обучения в начальной школе

Применение активных методов обучения в начальной школе Школьный кружок Комнатное цветоводство. О чем рассказали листья комнатных растений

Школьный кружок Комнатное цветоводство. О чем рассказали листья комнатных растений Вороний день ( Вурна хатл ) - праздник встречи весны у народов Севера

Вороний день ( Вурна хатл ) - праздник встречи весны у народов Севера Этапы становления Российского государства

Этапы становления Российского государства Моңғолдар мемлекеттілік деңгейге қалайша жетті?

Моңғолдар мемлекеттілік деңгейге қалайша жетті? Георгий Победоносец, великомученик. День памяти: 6 мая

Георгий Победоносец, великомученик. День памяти: 6 мая Развивающая игра Что лишнее?

Развивающая игра Что лишнее? Поливинилхлоридтің алынуы мен қолданылуы

Поливинилхлоридтің алынуы мен қолданылуы Урок по светской этике Терпимость и терпение

Урок по светской этике Терпимость и терпение Урал. Путешествие по России

Урал. Путешествие по России Спартакиада муниципальных образований Малопургинского района

Спартакиада муниципальных образований Малопургинского района Где находится/ находятся …?

Где находится/ находятся …? презентация к педагогическому совету

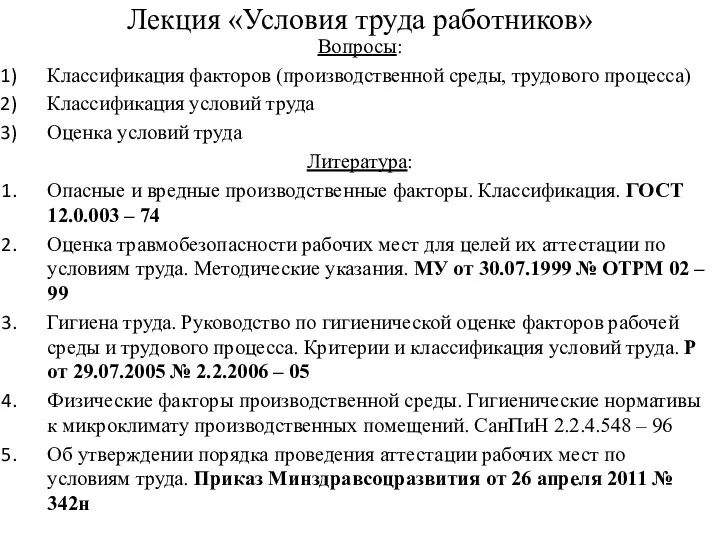

презентация к педагогическому совету Условия труда работников

Условия труда работников Людвиг ван Бетховен

Людвиг ван Бетховен Виды пластических искусств

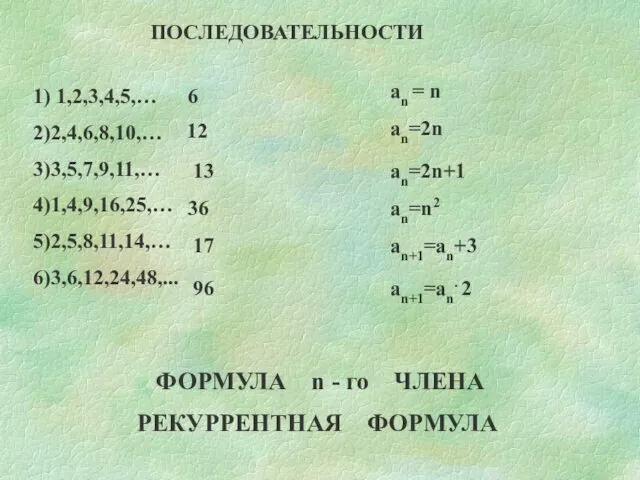

Виды пластических искусств Арифметическая прогрессия. 9 класс

Арифметическая прогрессия. 9 класс Обмен веществ и энергии

Обмен веществ и энергии Альдегиды и кетоны

Альдегиды и кетоны Геологиялық барлау кәсіпорнының қосалқы өндірістері мен қызмет көрсетуші шаруашылықтарын ұйымдастыру

Геологиялық барлау кәсіпорнының қосалқы өндірістері мен қызмет көрсетуші шаруашылықтарын ұйымдастыру Проблема коммуникативности и ситуативности в современной методической науке

Проблема коммуникативности и ситуативности в современной методической науке Система управления морально-психологическим обеспечением личного состава подразделения. (Тема 18.2)

Система управления морально-психологическим обеспечением личного состава подразделения. (Тема 18.2) Туманности и их виды

Туманности и их виды