Содержание

- 2. Кварцевый резонатор

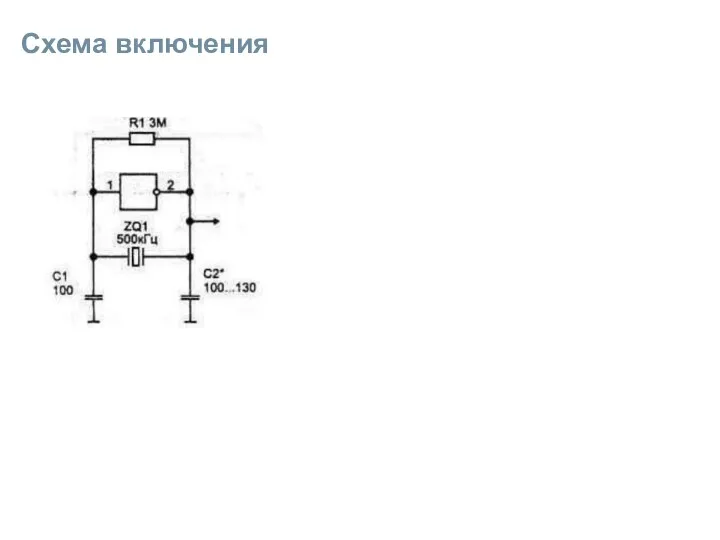

- 3. Схема включения

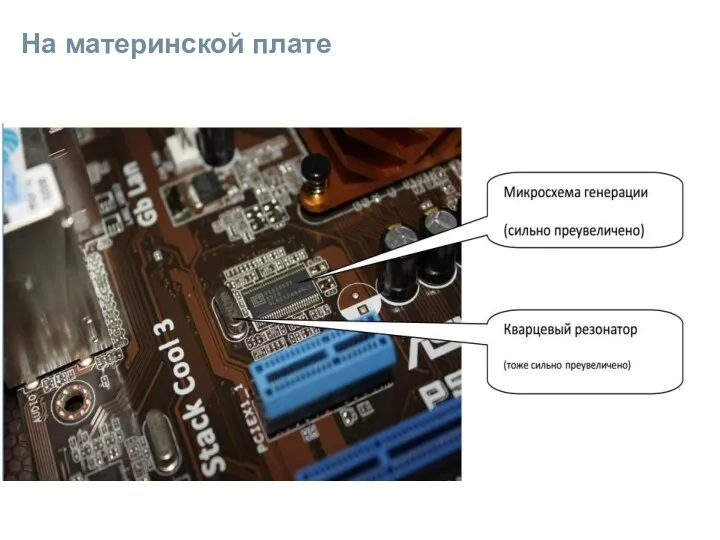

- 4. На материнской плате

- 5. План лекции Обобщенная структура цифровых устройств Классификация управляющих автоматов Управляющий автомат Мили. Управляющий автомат Мура. Микропрограммный

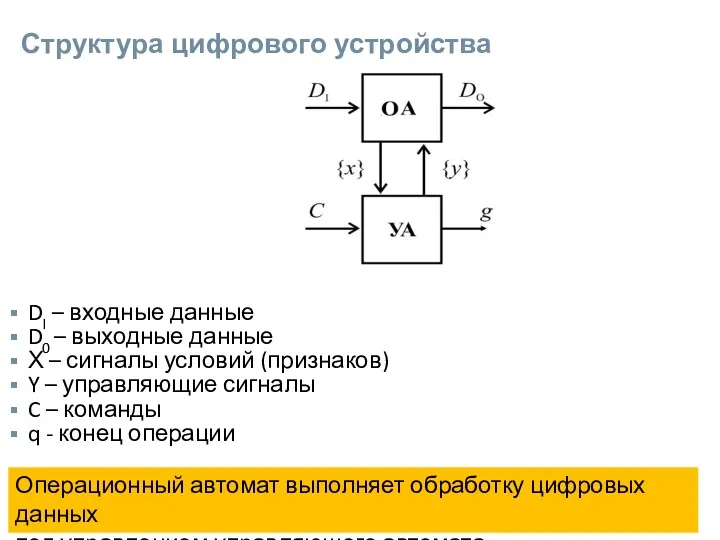

- 6. Структура цифрового устройства DI – входные данные D0 – выходные данные Х – сигналы условий (признаков)

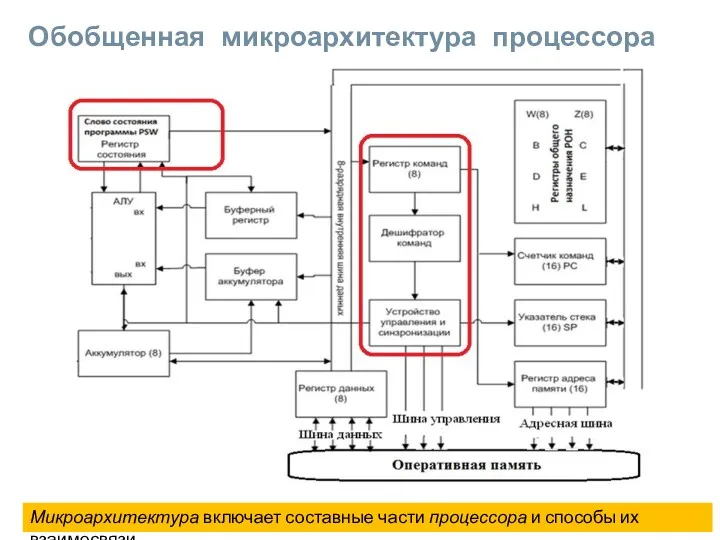

- 7. Обобщенная микроархитектура процессора Микроархитектура включает составные части процессора и способы их взаимосвязи

- 8. Уровневая модель компьютера

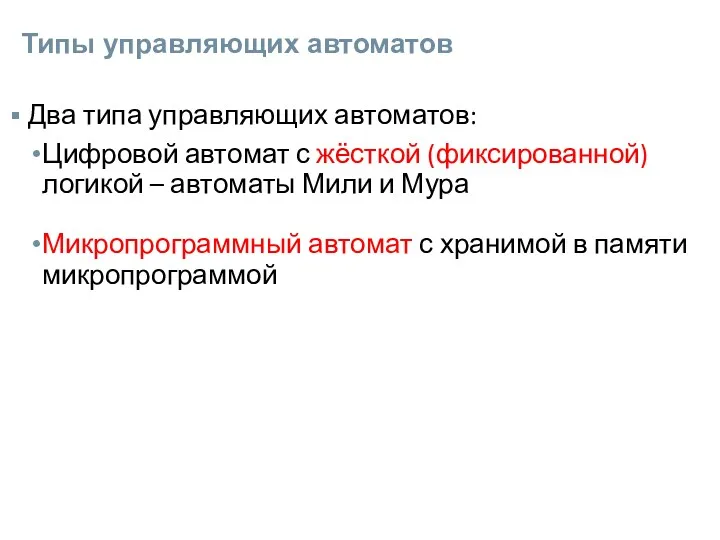

- 9. Типы управляющих автоматов Два типа управляющих автоматов: Цифровой автомат с жёсткой (фиксированной) логикой – автоматы Мили

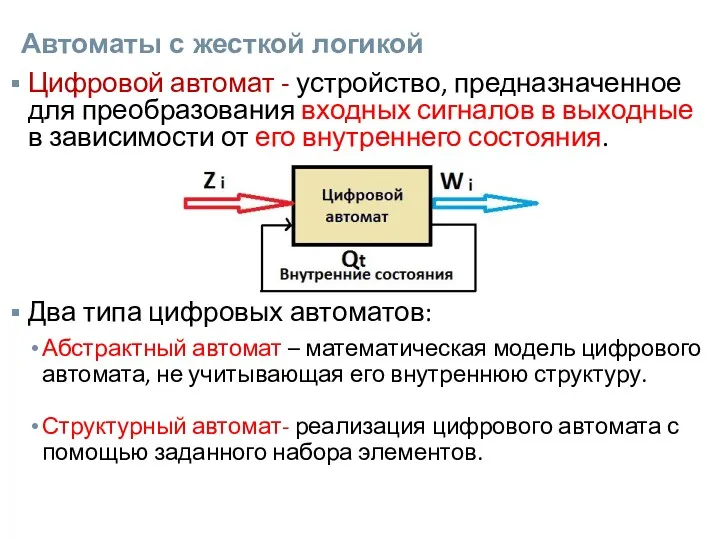

- 10. Автоматы с жесткой логикой Цифровой автомат - устройство, предназначенное для преобразования входных сигналов в выходные в

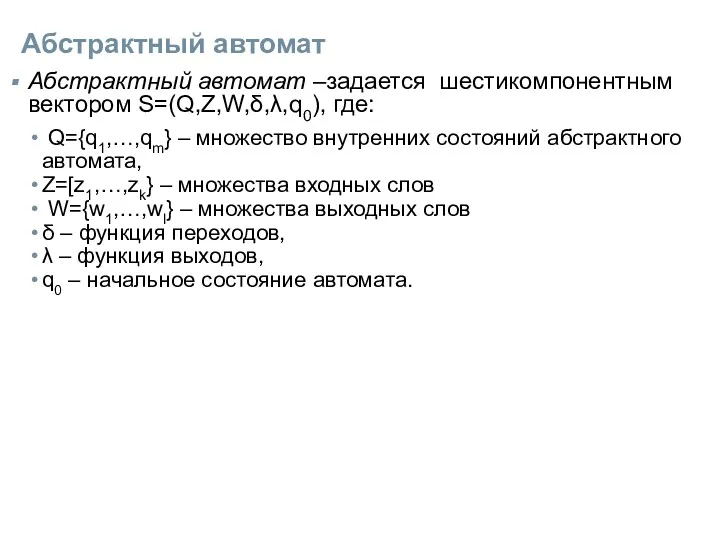

- 11. Абстрактный автомат Абстрактный автомат –задается шестикомпонентным вектором S=(Q,Z,W,δ,λ,q0), где: Q={q1,…,qm} – множество внутренних состояний абстрактного автомата,

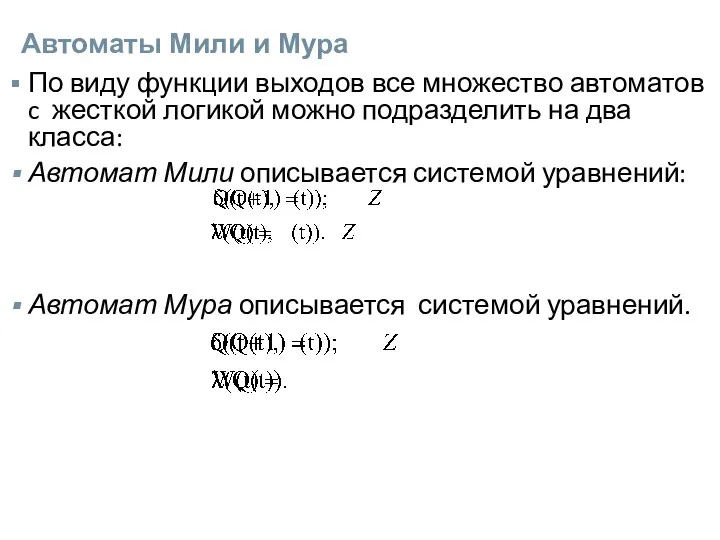

- 12. Автоматы Мили и Мура По виду функции выходов все множество автоматов c жесткой логикой можно подразделить

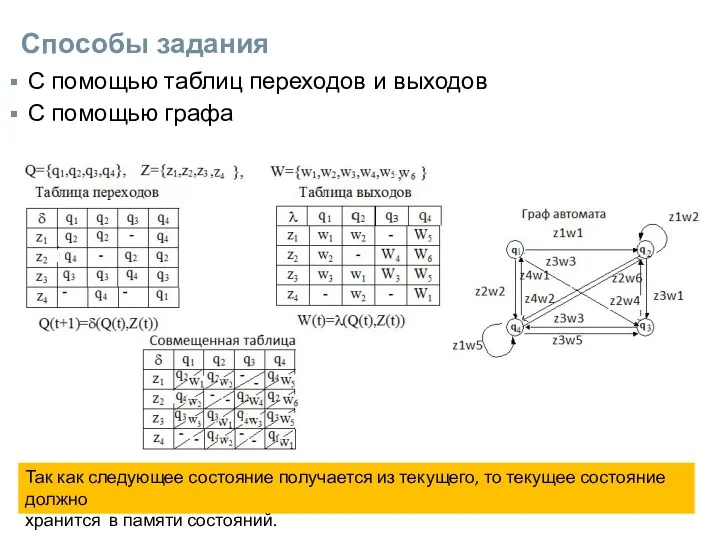

- 13. Способы задания С помощью таблиц переходов и выходов С помощью графа Так как следующее состояние получается

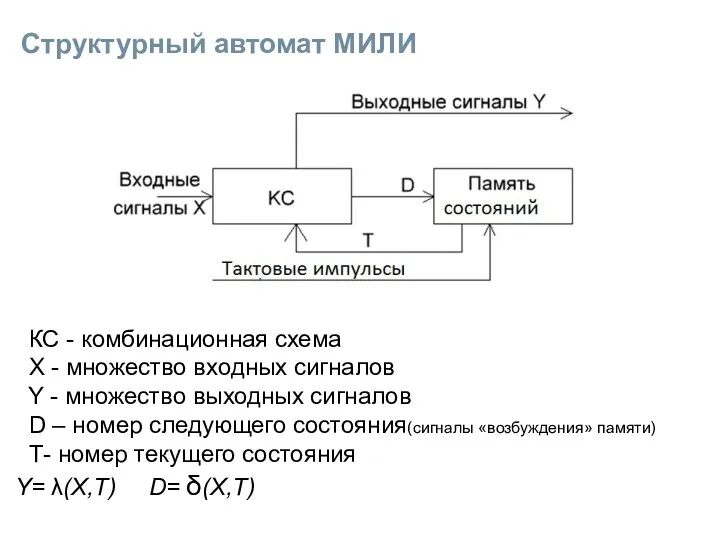

- 14. Структурный автомат МИЛИ КС - комбинационная схема Х - множество входных сигналов Y - множество выходных

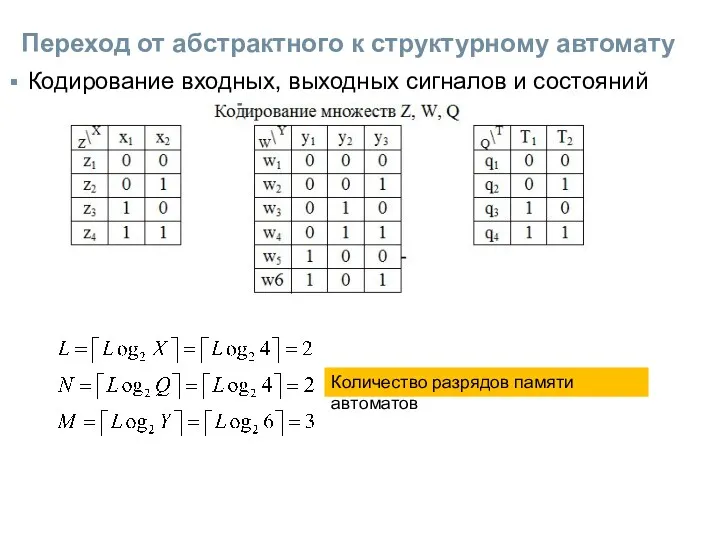

- 15. Переход от абстрактного к структурному автомату Кодирование входных, выходных сигналов и состояний Количество разрядов памяти автоматов

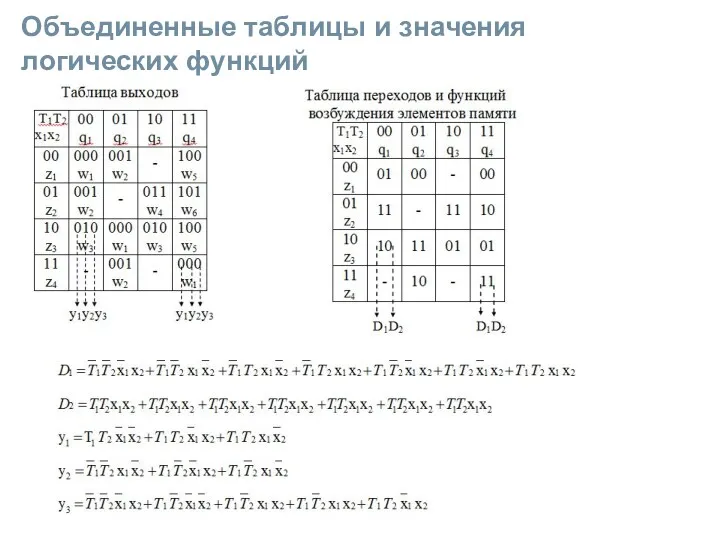

- 16. Объединенные таблицы и значения логических функций

- 17. Пример синтеза УА Разработать устройство суммирования двух чисел . Одно из слагаемых может быть положительным или

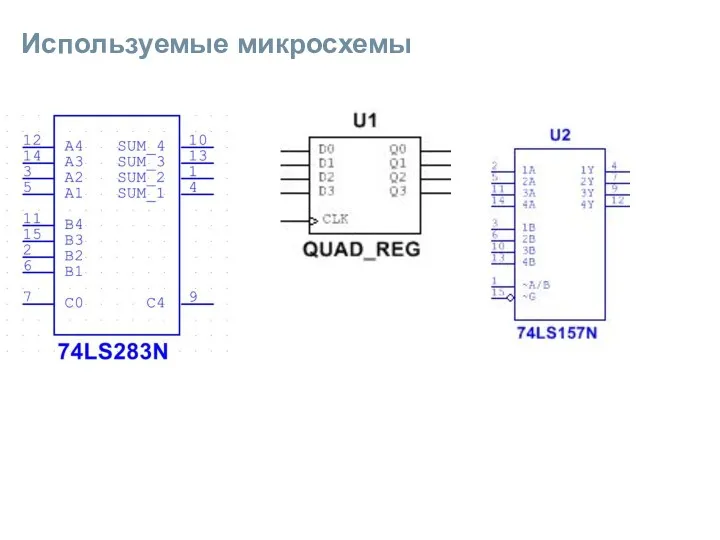

- 18. Используемые микросхемы

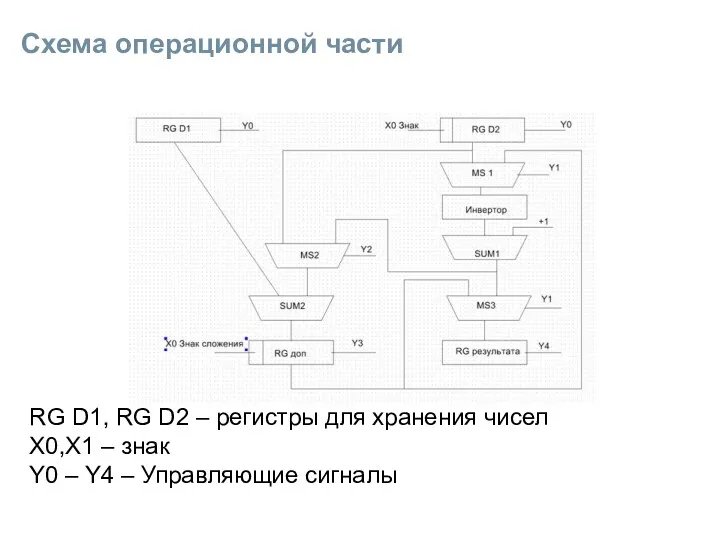

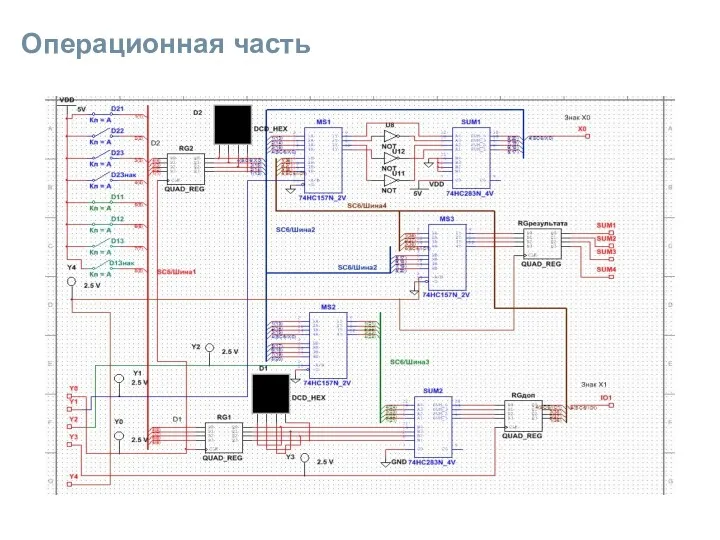

- 19. Схема операционной части RG D1, RG D2 – регистры для хранения чисел X0,X1 – знак Y0

- 20. Операционная часть

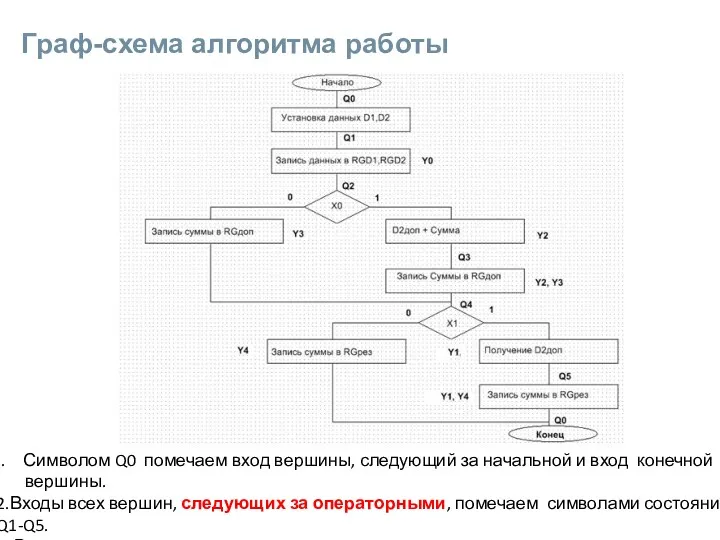

- 21. Граф-схема алгоритма работы Символом Q0 помечаем вход вершины, следующий за начальной и вход конечной вершины. 2.Входы

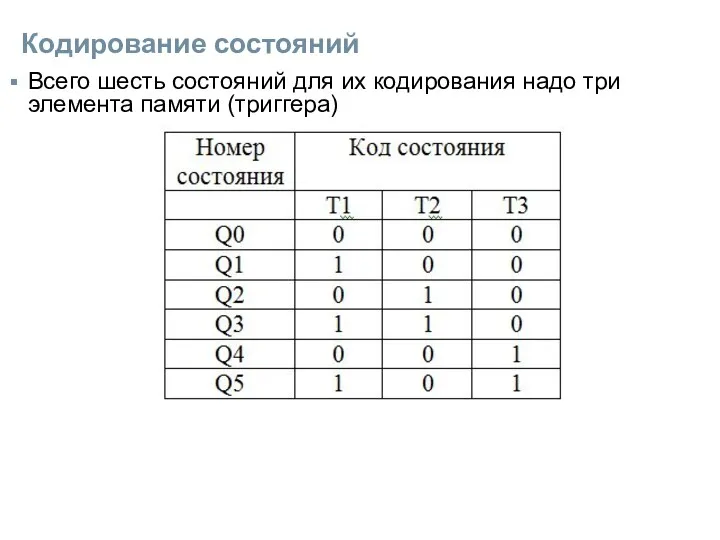

- 22. Кодирование состояний Всего шесть состояний для их кодирования надо три элемента памяти (триггера)

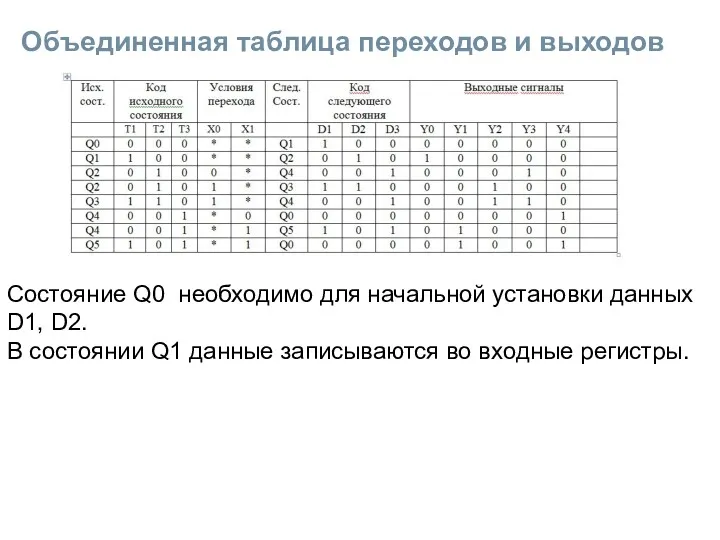

- 23. Объединенная таблица переходов и выходов Состояние Q0 необходимо для начальной установки данных D1, D2. В состоянии

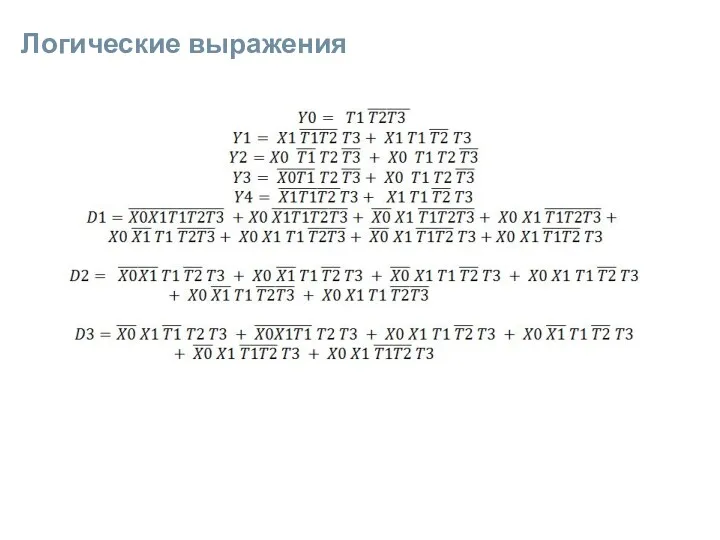

- 24. Логические выражения

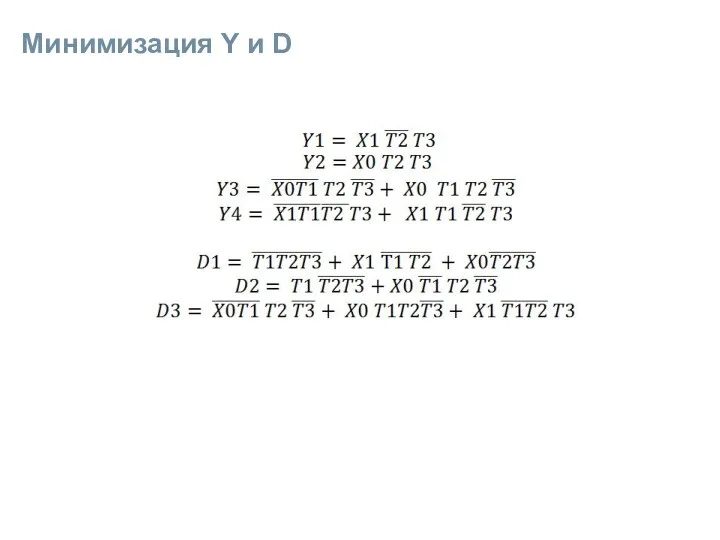

- 25. Минимизация Y и D

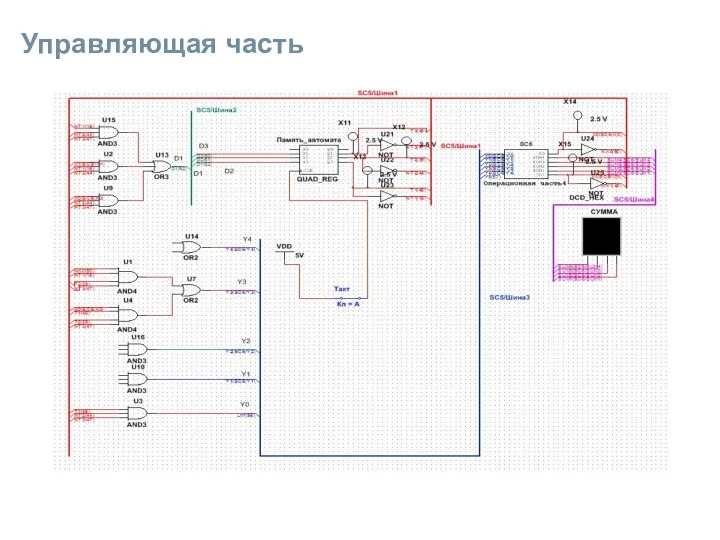

- 26. Управляющая часть

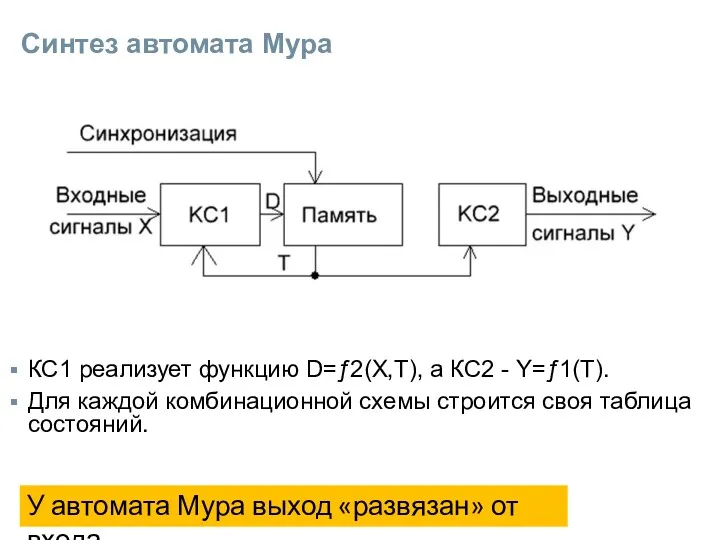

- 27. Синтез автомата Мура КС1 реализует функцию D=ƒ2(X,T), а КС2 - Y=ƒ1(T). Для каждой комбинационной схемы строится

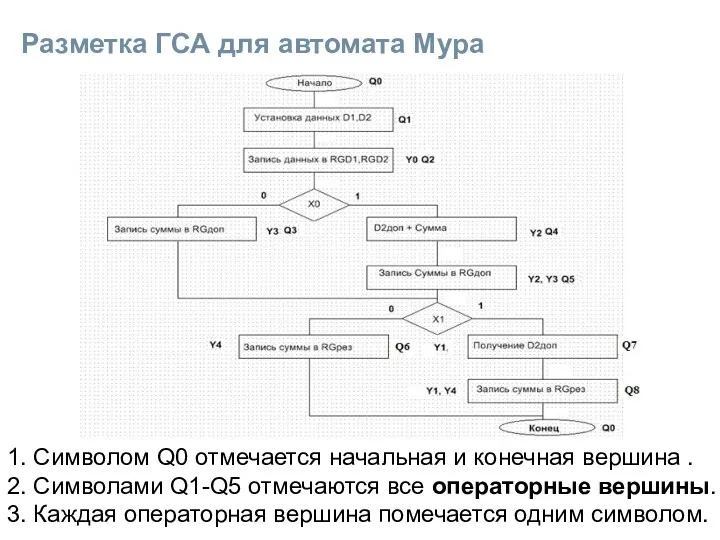

- 28. Разметка ГСА для автомата Мура 1. Символом Q0 отмечается начальная и конечная вершина . 2. Символами

- 29. Кодирование состояний и таблицы выходов для КС2 Всего 9 состояний – надо 4 триггера

- 30. Кодирование состояний и таблица переходов для КС1

- 31. Запись СДНФ и минимизация выражений По таблицам записываем СДНФ – для Y0-Y4 и D1-D4 Например: Минимизируем

- 32. Недостатки УА на основе жесткой логики 1. При необходимости внесения любых, даже небольших изменений алгоритма работы

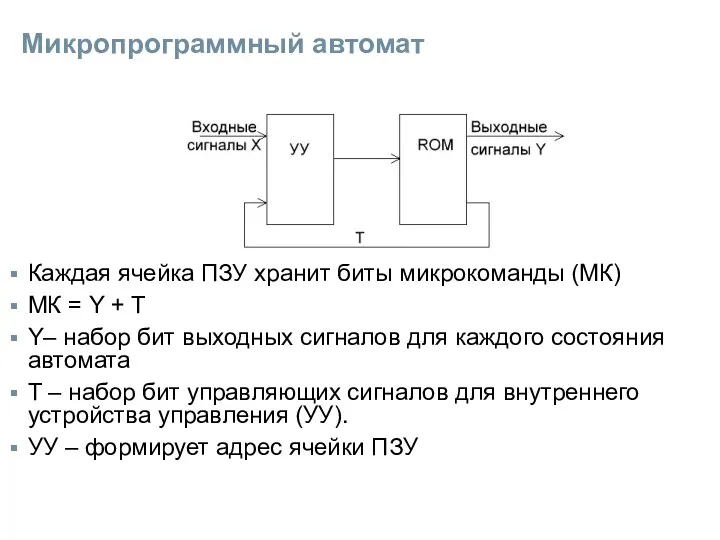

- 33. Микропрограммный автомат Каждая ячейка ПЗУ хранит биты микрокоманды (МК) МК = Y + T Y– набор

- 34. Структура микропрограммного автомата Счётчик-РАМК(регистр адреса микрокоманды) при V=0 выполняет загрузку адреса команды со входов D, при

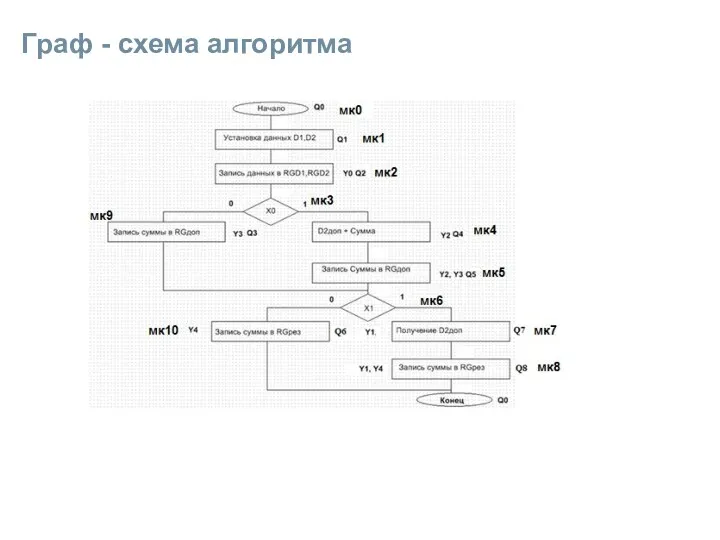

- 35. Граф - схема алгоритма

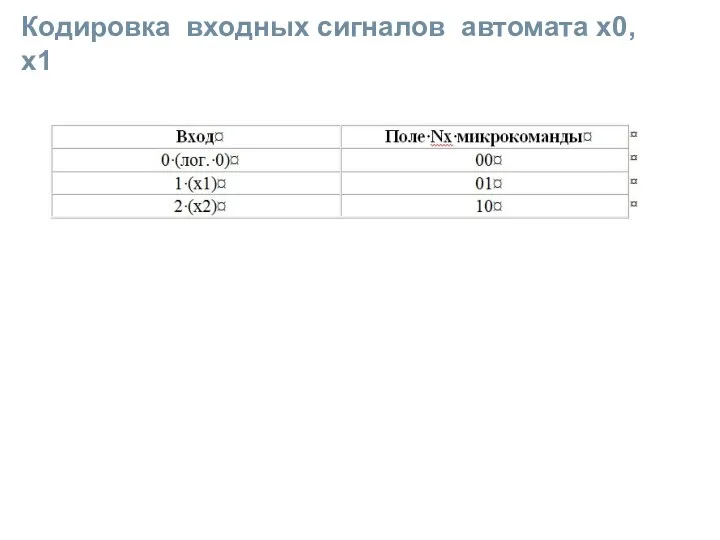

- 36. Кодировка входных сигналов автомата x0, x1

- 37. Таблица переходов Микропрограмма занимает 14 ячеек памяти. Разрядность выходных данных ПЗУ определяется: V+Nx+A+Y=1+2+4+5=12.

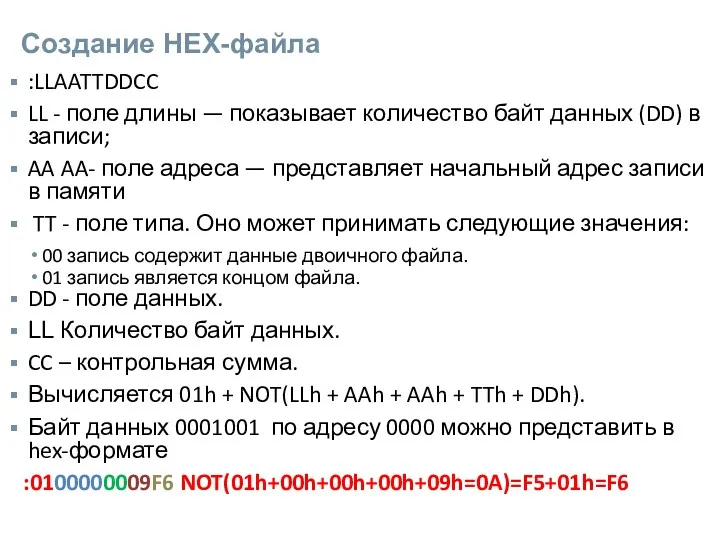

- 38. Создание HEX-файла :LLAATTDDCC LL - поле длины — показывает количество байт данных (DD) в записи; AA

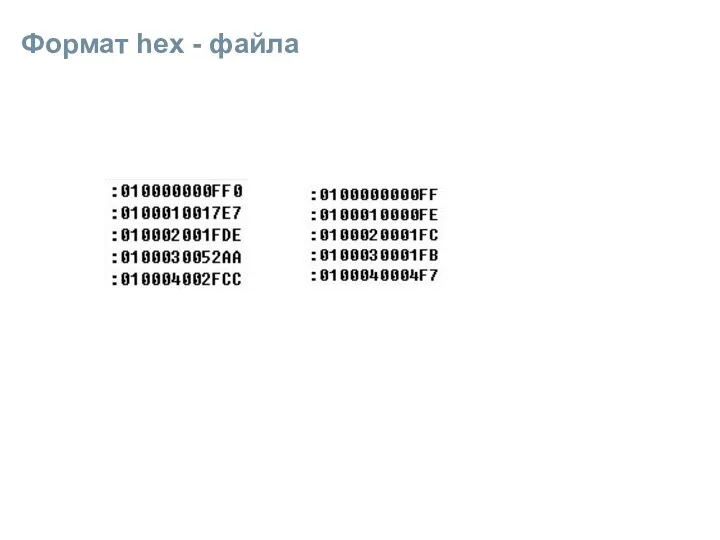

- 39. Формат hex - файла

- 41. Скачать презентацию

Лечебная физическая культура

Лечебная физическая культура КВН по сказкам А. С. Пушкина

КВН по сказкам А. С. Пушкина ПДД для Особого ребенка

ПДД для Особого ребенка Комплексная программа инновационного развития холдинга РЖД

Комплексная программа инновационного развития холдинга РЖД Создание собственного медиа-пространства на всех платформах социальных сетей

Создание собственного медиа-пространства на всех платформах социальных сетей Столетняя война 1337-1453

Столетняя война 1337-1453 Игры для развития мелкой моторики своими руками.

Игры для развития мелкой моторики своими руками. Таблица умножения и деления на 3

Таблица умножения и деления на 3 Женские образы, в романе М.А. Шолохова Тихий Дон

Женские образы, в романе М.А. Шолохова Тихий Дон презентация месяца и дни недели

презентация месяца и дни недели Мужские половые органы

Мужские половые органы Областной молодежный форум Достижение

Областной молодежный форум Достижение Company confidential Lenovo S660 Service Manual

Company confidential Lenovo S660 Service Manual Скорость химических реакций

Скорость химических реакций Исследовательская работа Моё здоровье

Исследовательская работа Моё здоровье Эксплуатация и ремонт аппаратов защиты

Эксплуатация и ремонт аппаратов защиты Город Севастополь

Город Севастополь День рождения

День рождения Угольная промышленность России

Угольная промышленность России Обработка мяса. Полуфабрикаты из мяса

Обработка мяса. Полуфабрикаты из мяса ЛИЧНОСТНО-ОРИЕНТИРОВАННАЯ ТЕХНОЛОГИЯ

ЛИЧНОСТНО-ОРИЕНТИРОВАННАЯ ТЕХНОЛОГИЯ Деятельность психолого-медико-педагогических комиссий в современных условиях

Деятельность психолого-медико-педагогических комиссий в современных условиях Художественные и телевизионные фильмы о жизни А.С Пушкина

Художественные и телевизионные фильмы о жизни А.С Пушкина Prezentatsia_Ruzina

Prezentatsia_Ruzina Классный час Радуга безопасности

Классный час Радуга безопасности Futur simple

Futur simple Полтавщина – мій рідний край. 75-річчю утворення Полтавської області присвячується

Полтавщина – мій рідний край. 75-річчю утворення Полтавської області присвячується Математика. 3 класс. Таблица умножения. Игра-тренажёр Собери ананас

Математика. 3 класс. Таблица умножения. Игра-тренажёр Собери ананас