Содержание

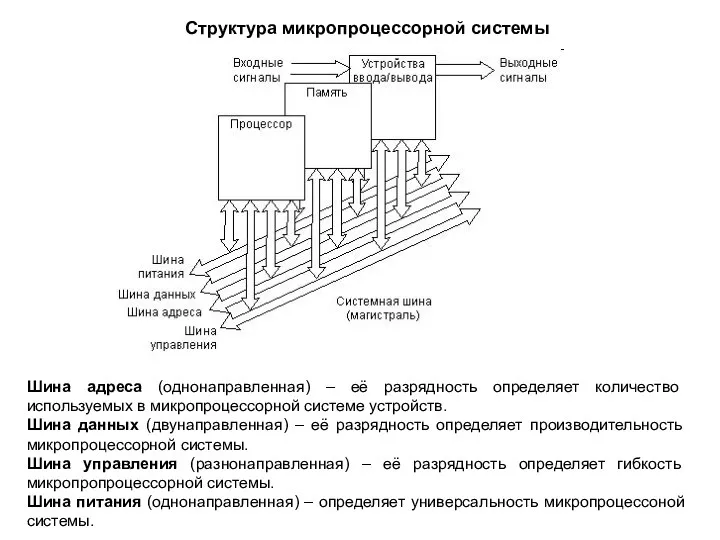

- 2. Структура микропроцессорной системы Шина адреса (однонаправленная) – её разрядность определяет количество используемых в микропроцессорной системе устройств.

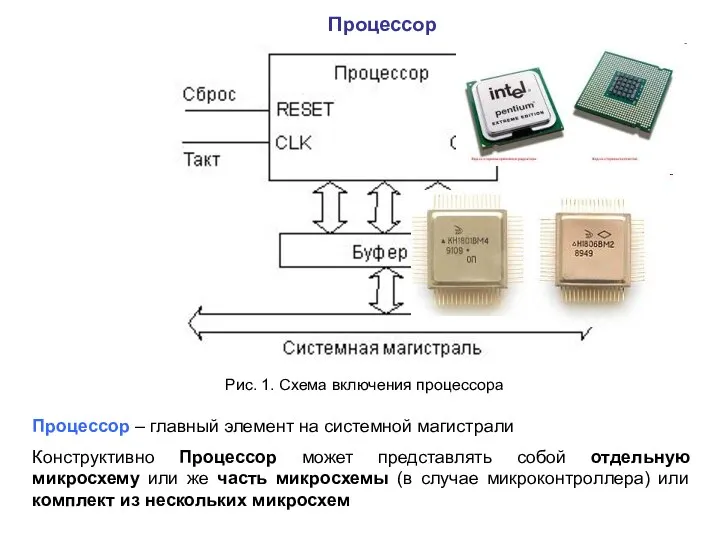

- 3. Процессор Рис. 1. Схема включения процессора Процессор – главный элемент на системной магистрали Конструктивно Процессор может

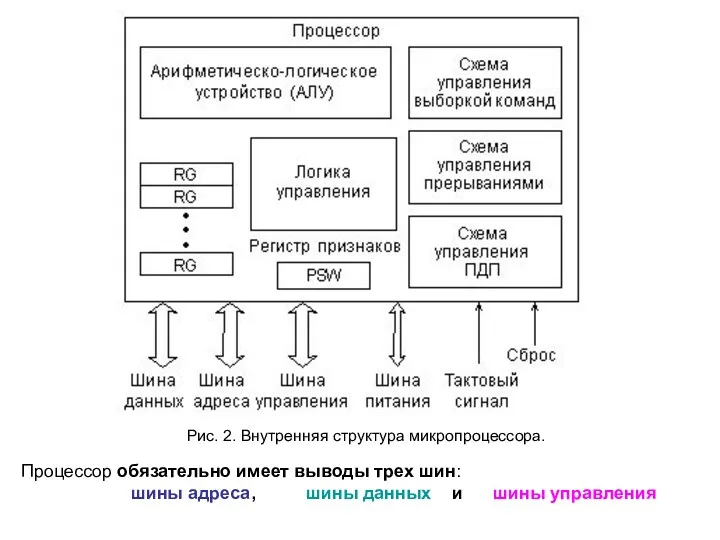

- 4. Процессор обязательно имеет выводы трех шин: шины адреса, шины данных и шины управления Рис. 2. Внутренняя

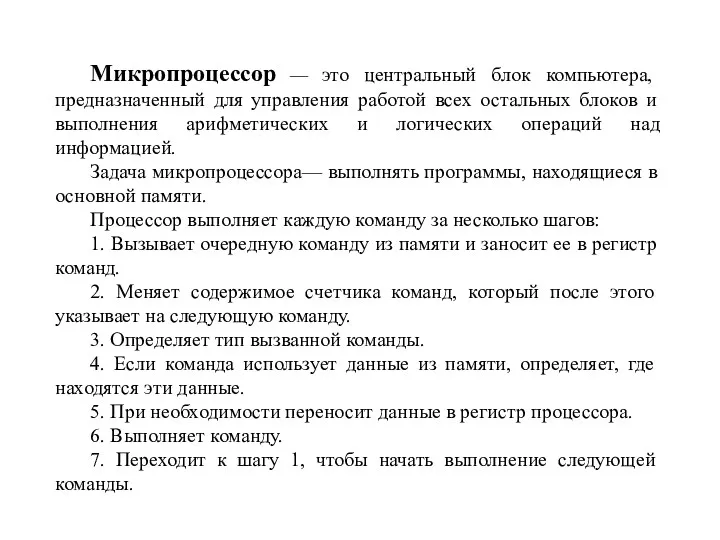

- 5. Микропроцессор — это центральный блок компьютера, предназначенный для управления работой всех остальных блоков и выполнения арифметических

- 6. В состав микропроцессора входят следующие устройства: 1. Арифметико-логическое устройство предназначено для выполнения всех арифметических и логических

- 7. Режимы работы процессора: Реальный режим — это режим, в котором работали старые процессоры. Обработка прерываний производится

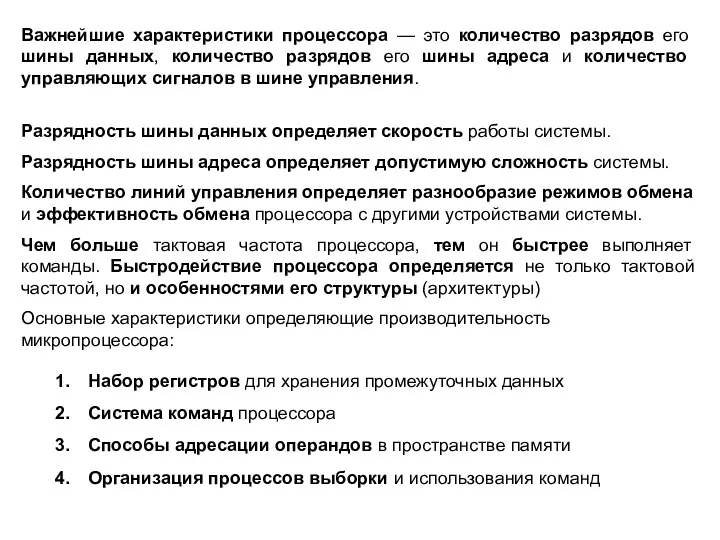

- 8. Разрядность шины данных определяет скорость работы системы. Разрядность шины адреса определяет допустимую сложность системы. Количество линий

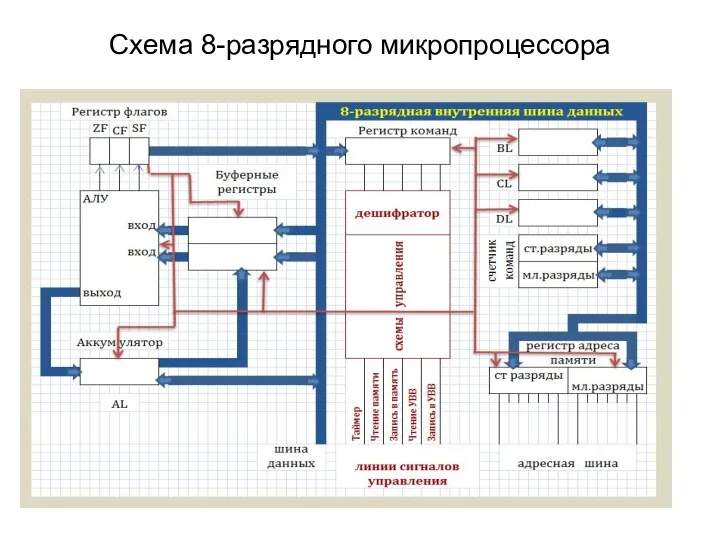

- 9. Схема 8-разрядного микропроцессора

- 10. Микропроцессор состоит из трех основных блоков: -АЛУ, -регистров, -устройства управления. Для передачи данных между ними используется

- 11. 3.Счетчик команд отвечает за то, какая команда выполняется, а какая будет выполняться следующей. Перед выполнением программы

- 12. 6.Буферные регистры АЛУ предназначены для временного хранения одного байта данных. Один из этих регистров (ближайший к

- 13. Основные функции любого микропроцессора: выборка (чтение) выполняемых команд; ввод (чтение) данных из памяти или устройства ввода/вывода;

- 14. Система команд может быть: Ортогональная – все команды фиксированной длины, имеют одинаковое время исполнения (преимущественно за

- 15. В микропроцессорах с полным набором команд (CISC микропроцессоры) используется уровень микропрограммирования для того, чтобы декодировать и

- 16. В микропроцессорах с сокращённым набором команд (RISC процессоры) декодирование и исполнение команды производится аппаратно, поэтому количество

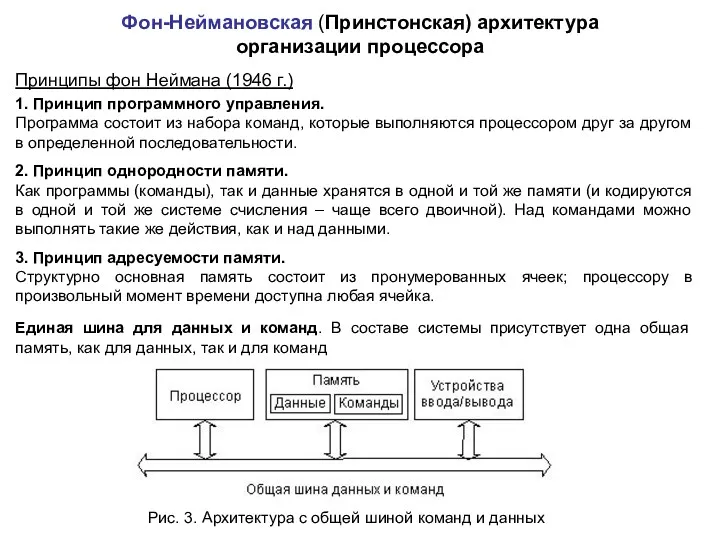

- 17. Рис. 3. Архитектура с общей шиной команд и данных Фон-Неймановская (Принстонская) архитектура организации процессора Единая шина

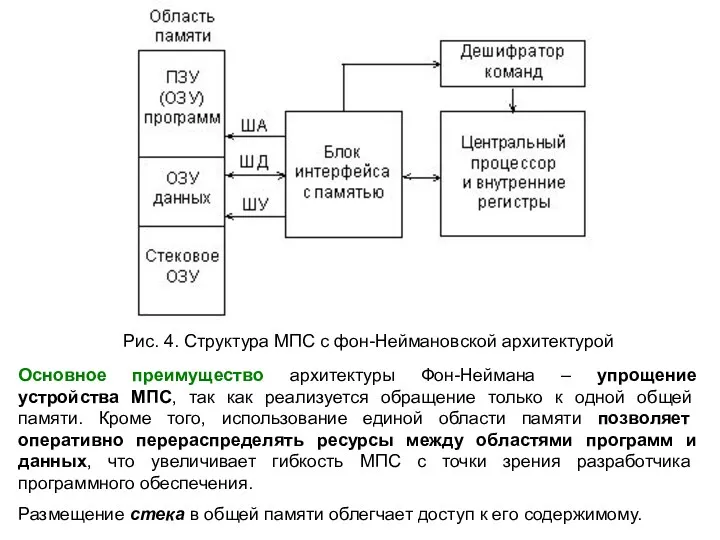

- 18. Основное преимущество архитектуры Фон-Неймана – упрощение устройства МПС, так как реализуется обращение только к одной общей

- 19. Гарвардская архитектура организации процессора Рис. 5. Архитектура с раздельными шинами данных и команд Гарвардская архитектура (разработана

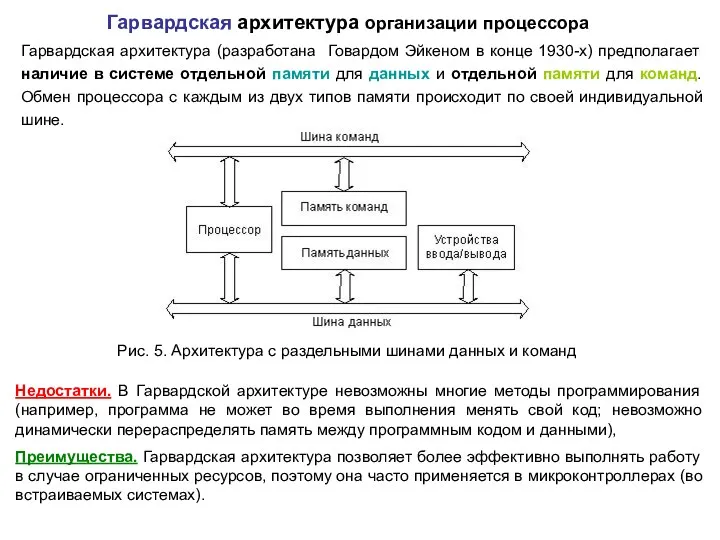

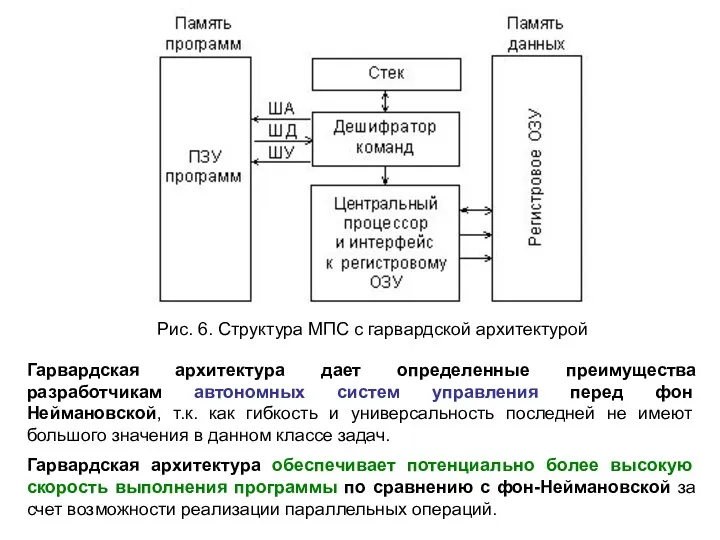

- 20. Рис. 6. Структура МПС с гарвардской архитектурой Гарвардская архитектура дает определенные преимущества разработчикам автономных систем управления

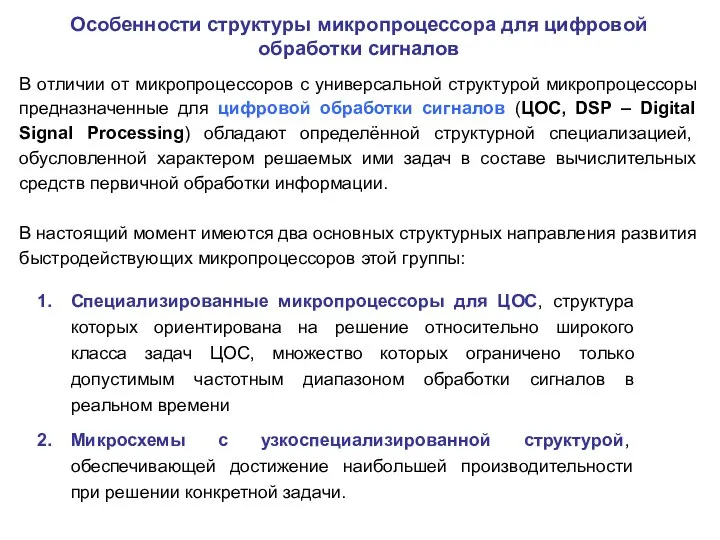

- 21. Особенности структуры микропроцессора для цифровой обработки сигналов В отличии от микропроцессоров с универсальной структурой микропроцессоры предназначенные

- 22. Особенности архитектуры ЦПОС программы выполняются, как правило, в реальном масштабе времени - по мере поступления входного

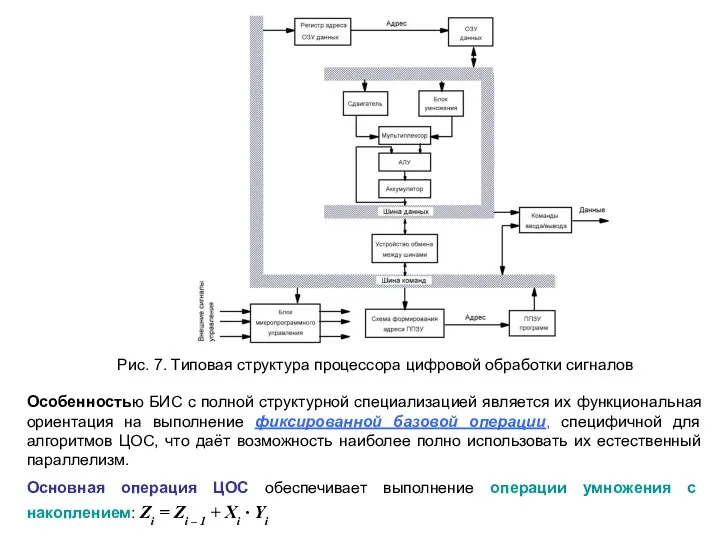

- 23. Рис. 7. Типовая структура процессора цифровой обработки сигналов Особенностью БИС с полной структурной специализацией является их

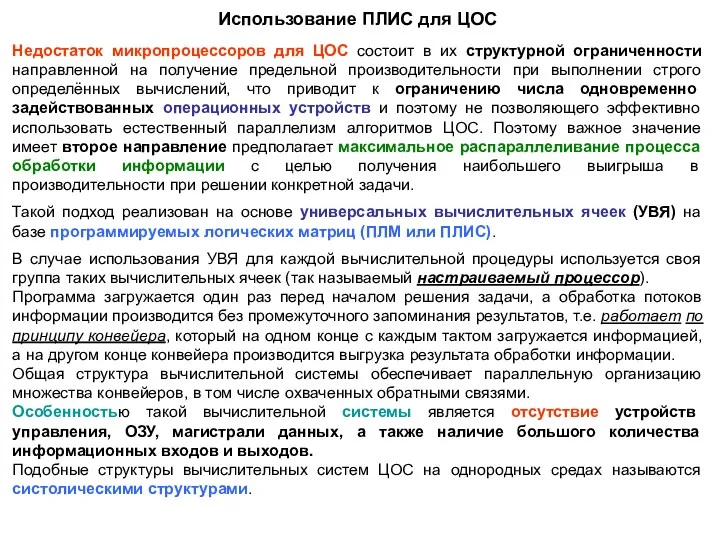

- 24. Недостаток микропроцессоров для ЦОС состоит в их структурной ограниченности направленной на получение предельной производительности при выполнении

- 25. Функции памяти Память микропроцессорной системы выполняет функцию временного или постоянного хранения данных и команд. Объем памяти

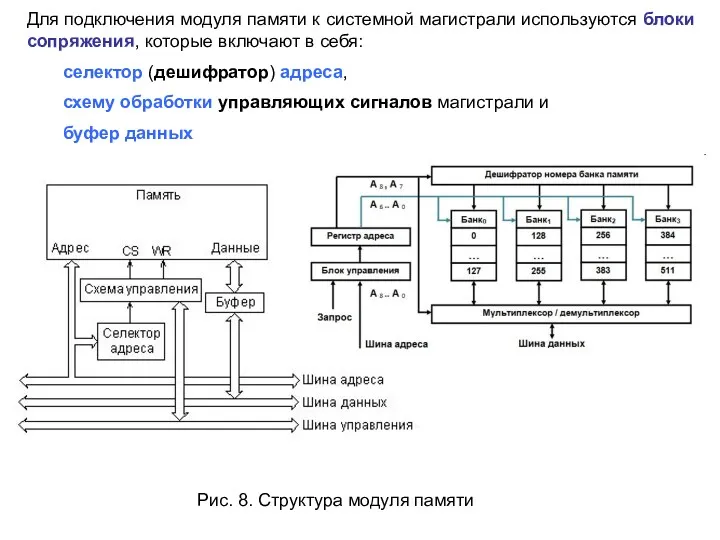

- 26. Для подключения модуля памяти к системной магистрали используются блоки сопряжения, которые включают в себя: селектор (дешифратор)

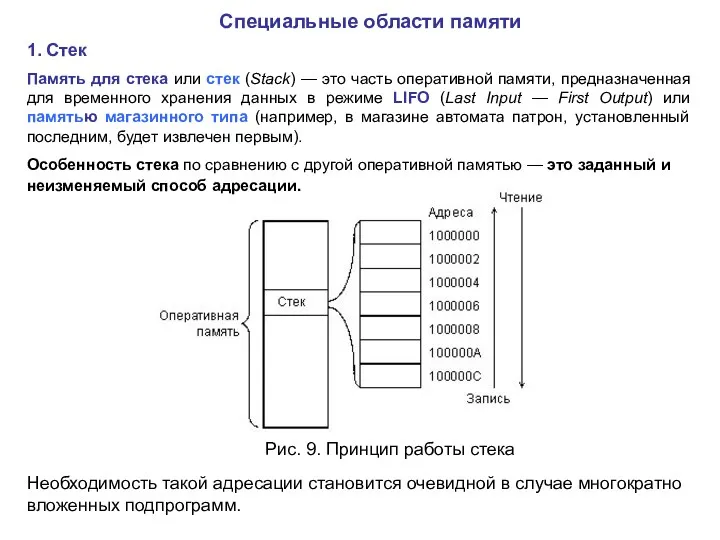

- 27. Специальные области памяти 1. Стек Память для стека или стек (Stack) — это часть оперативной памяти,

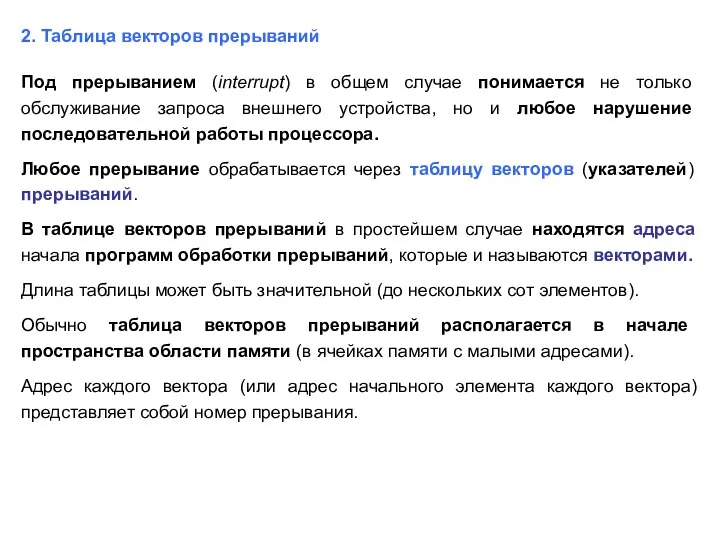

- 28. 2. Таблица векторов прерываний Под прерыванием (interrupt) в общем случае понимается не только обслуживание запроса внешнего

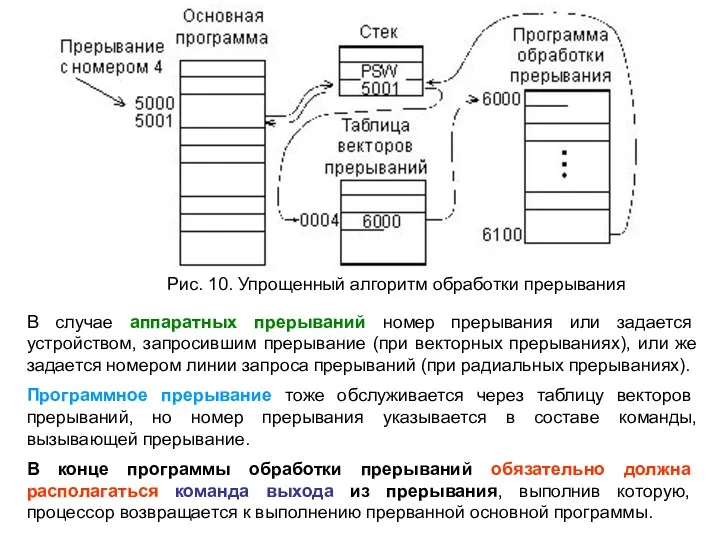

- 29. Рис. 10. Упрощенный алгоритм обработки прерывания В случае аппаратных прерываний номер прерывания или задается устройством, запросившим

- 30. 3. Память устройств (ввода/вывода), подключенных к системной шине. Процессор получает возможность обращаться к внутренней памяти устройств

- 31. Функции устройств ввода/вывода Устройства ввода/вывода обмениваются информацией с магистралью по тем же принципам, что и память.

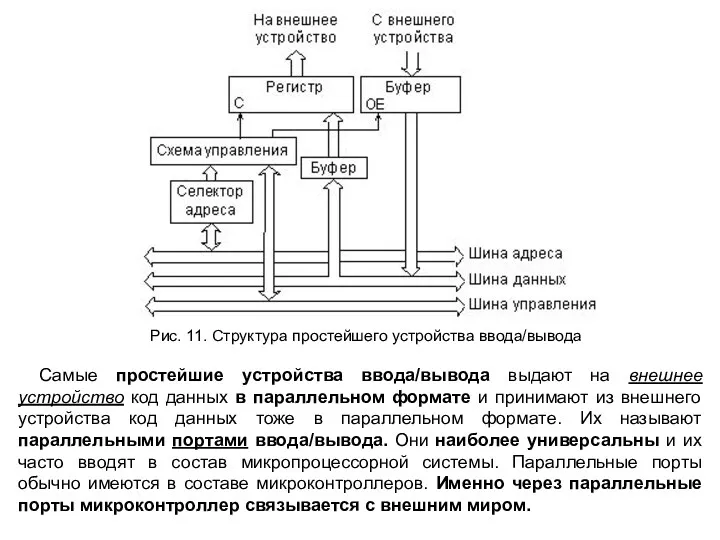

- 32. Рис. 11. Структура простейшего устройства ввода/вывода Самые простейшие устройства ввода/вывода выдают на внешнее устройство код данных

- 33. Более сложные устройства ввода/вывода (устройства сопряжения) имеют в своем составе внутреннюю буферную оперативную память и даже

- 35. Скачать презентацию

Изотерапия, как одна из граней арттерапии.

Изотерапия, как одна из граней арттерапии. Раствор. Типы растворов. Способы выражения концентрации растворов. Теория электролитической диссоциации

Раствор. Типы растворов. Способы выражения концентрации растворов. Теория электролитической диссоциации Креативное программирование. Погружение в мир программирования и создание креативных проектов

Креативное программирование. Погружение в мир программирования и создание креативных проектов 275-летие со дня рождения русского полководца М.И. Кутузова (1745-1813). НТБ Люблинское

275-летие со дня рождения русского полководца М.И. Кутузова (1745-1813). НТБ Люблинское Развитие географических знаний о Земле. 6 кл.

Развитие географических знаний о Земле. 6 кл. Проект Виртуальный музей

Проект Виртуальный музей Расчёт блока вакуумной перегонки мазута, производительностью 2700000 т/год

Расчёт блока вакуумной перегонки мазута, производительностью 2700000 т/год Схема выдачи мощности Новоазовской ВЭС

Схема выдачи мощности Новоазовской ВЭС презентация к уроку Мы изучаем Японию

презентация к уроку Мы изучаем Японию Електробезпека

Електробезпека Механизированные способы добычи нефти

Механизированные способы добычи нефти Классификация химических реакций

Классификация химических реакций Старинная ярмарка.

Старинная ярмарка. Сера. Презентация к уроку химии в 9 классе.

Сера. Презентация к уроку химии в 9 классе. Оплодотворение

Оплодотворение Схема поверхностных течений

Схема поверхностных течений Проект Как погладить ёжика?

Проект Как погладить ёжика? Titania SlidesCarnival

Titania SlidesCarnival презентация проекта Встреча с будущим Диск

презентация проекта Встреча с будущим Диск Проводники, непроводники и полупроводники электричества

Проводники, непроводники и полупроводники электричества Международный женский день

Международный женский день урок с позиции здоровьесбережения

урок с позиции здоровьесбережения Карбоновые кислоты

Карбоновые кислоты презентация кружка оригами

презентация кружка оригами Духовная культура общества

Духовная культура общества Характеристики трещиностойкости фибробетона

Характеристики трещиностойкости фибробетона Отчет о прохождении учебной практики по профессиональному модулю

Отчет о прохождении учебной практики по профессиональному модулю Вес тела. Невесомость

Вес тела. Невесомость