Слайд 2

Двоичный сумматор

Двоичный сумматор (SM) служит для формирования арифметической суммы n-разрядных

двоичных чисел А и В. Результатом сложения (при n = 4) является четырехразрядная сумма S и выход переноса Р, который можно рассматривать как пятый разряд суммы.

Слайд 3

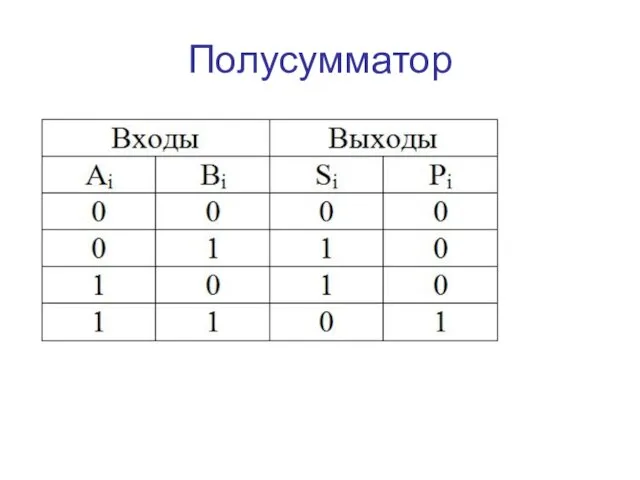

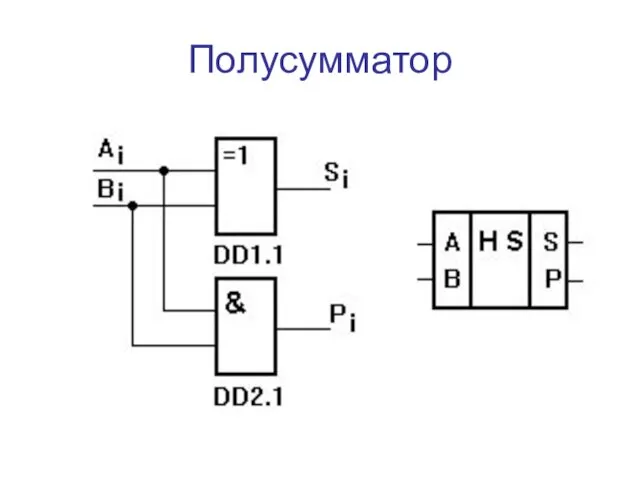

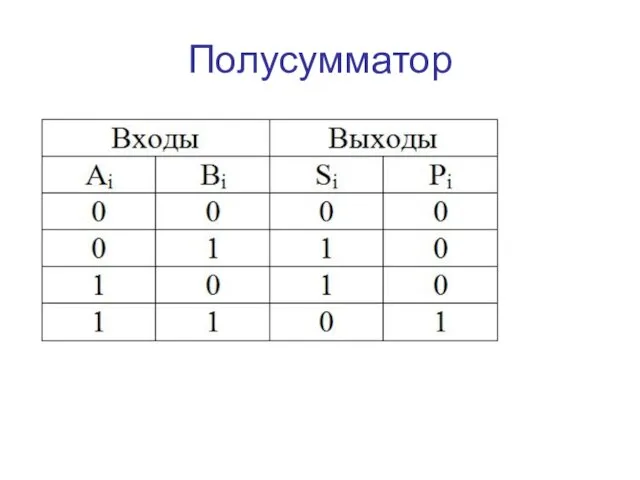

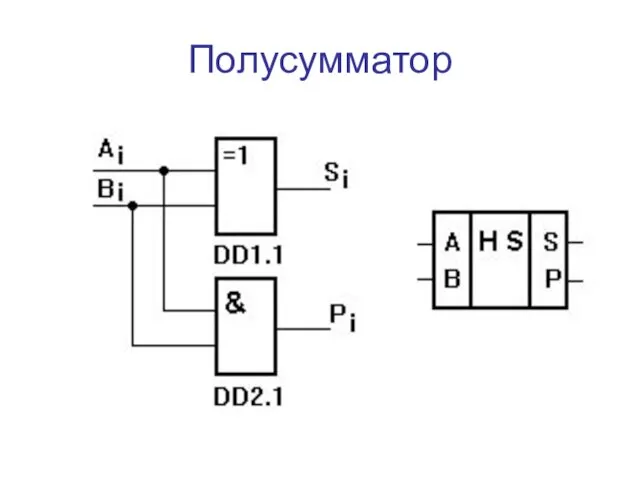

Полусумматор

Полусумматор (HS - HalfSum - полусумма), - это устройство, производящее

сложение двух одноразрядных двоичных чисел без учета переноса предыдущего разряда.

Слайд 4

Слайд 5

Слайд 6

Полный одноразрядный сумматор

Полный одноразрядный сумматор суммирует биты соответствующих разрядов двух

двоичных чисел с учетом переноса и вырабатывает перенос в следующий разряд.

Слайд 7

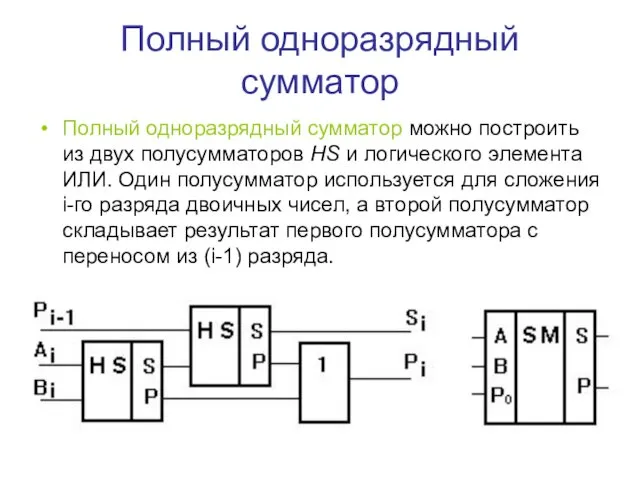

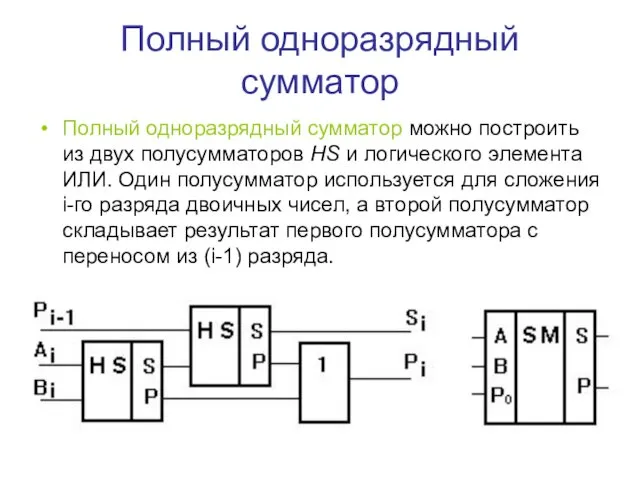

Полный одноразрядный сумматор

Полный одноразрядный сумматор можно построить из двух полусумматоров HS

и логического элемента ИЛИ. Один полусумматор используется для сложения i-го разряда двоичных чисел, а второй полусумматор складывает результат первого полусумматора с переносом из (i-1) разряда.

Слайд 8

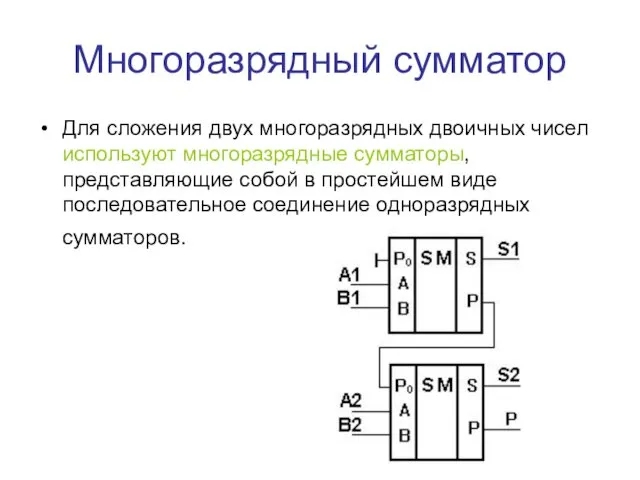

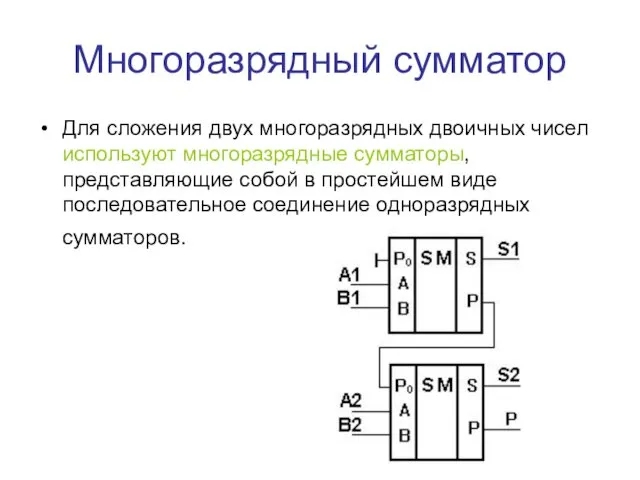

Многоразрядный сумматор

Для сложения двух многоразрядных двоичных чисел используют многоразрядные сумматоры, представляющие

собой в простейшем виде последовательное соединение одноразрядных сумматоров.

Слайд 9

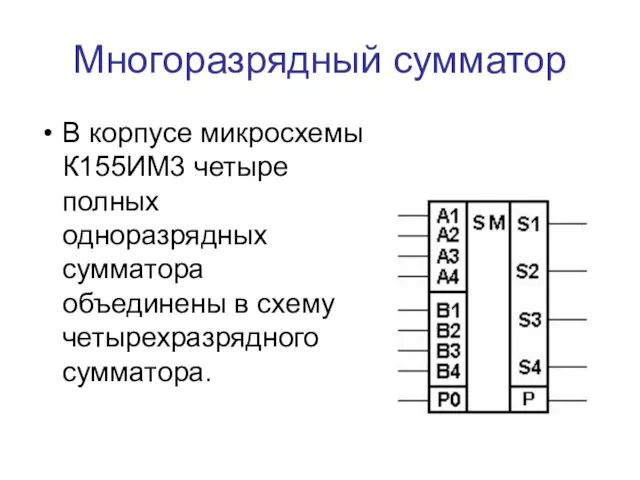

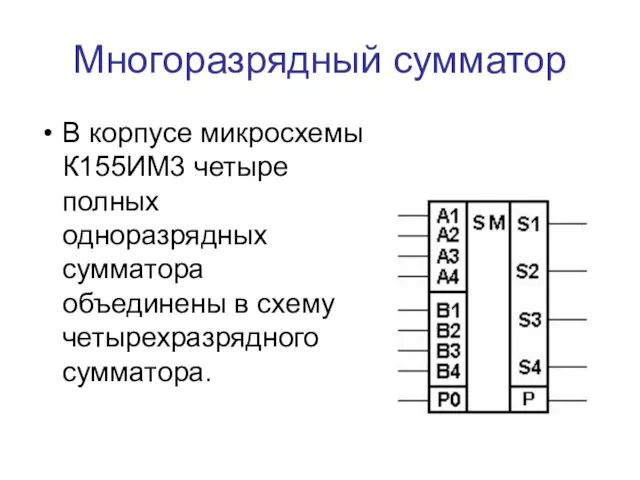

Многоразрядный сумматор

В корпусе микросхемы К155ИМ3 четыре полных одноразрядных сумматора объединены в

схему четырехразрядного сумматора.

Слайд 10

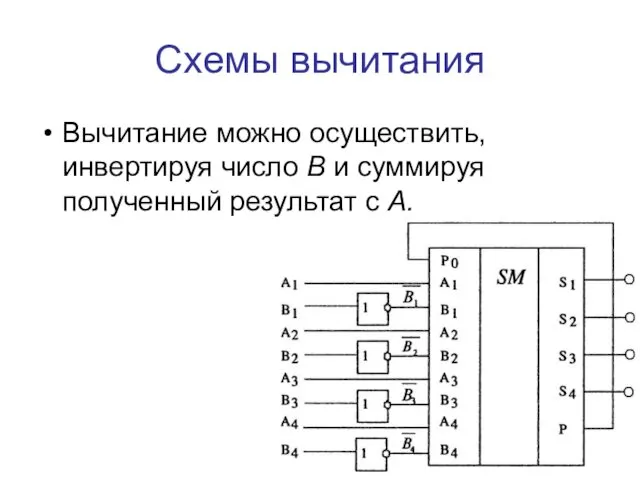

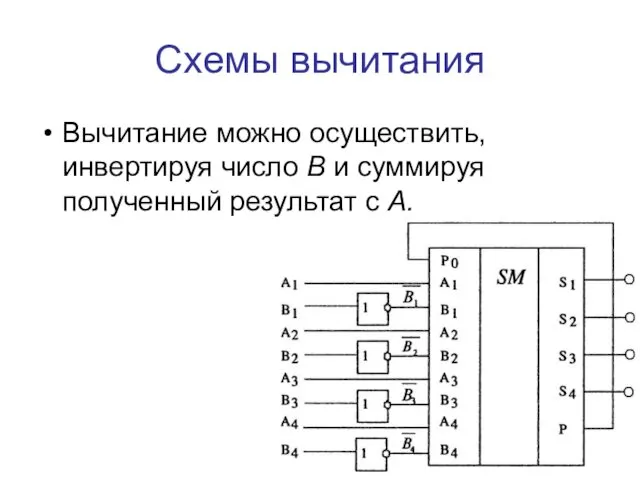

Схемы вычитания

Вычитание можно осуществить, инвертируя число В и суммируя полученный результат

с А.

Слайд 11

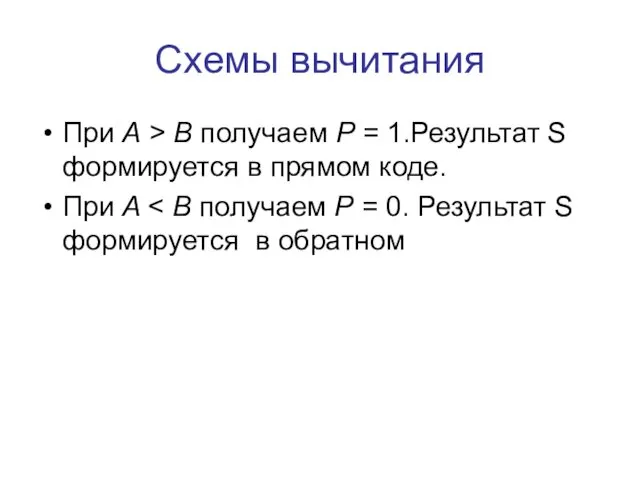

Схемы вычитания

При А > В получаем Р = 1.Результат S формируется

в прямом коде.

При A < B получаем Р = 0. Результат S формируется в обратном

Слайд 12

При С=0 устройство работает как сумматор.

При С=1 – как вычитатель.

Слайд 13

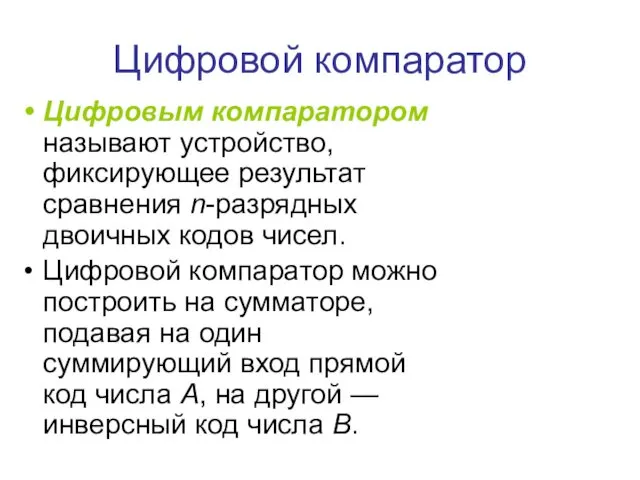

Цифровой компаратор

Цифровым компаратором называют устройство, фиксирующее результат сравнения n-разрядных двоичных кодов

чисел.

Цифровой компаратор можно построить на сумматоре, подавая на один суммирующий вход прямой код числа А, на другой — инверсный код числа В.

Слайд 14

Национальная идея и реальная политика в области качества в России

Национальная идея и реальная политика в области качества в России Итоговое родительское собрание в 4 классе.

Итоговое родительское собрание в 4 классе. Презентация Бурятский национальный костюм

Презентация Бурятский национальный костюм Политика как предмет политологии

Политика как предмет политологии Родительское собрание на тему:Здоровье детей в наших руках

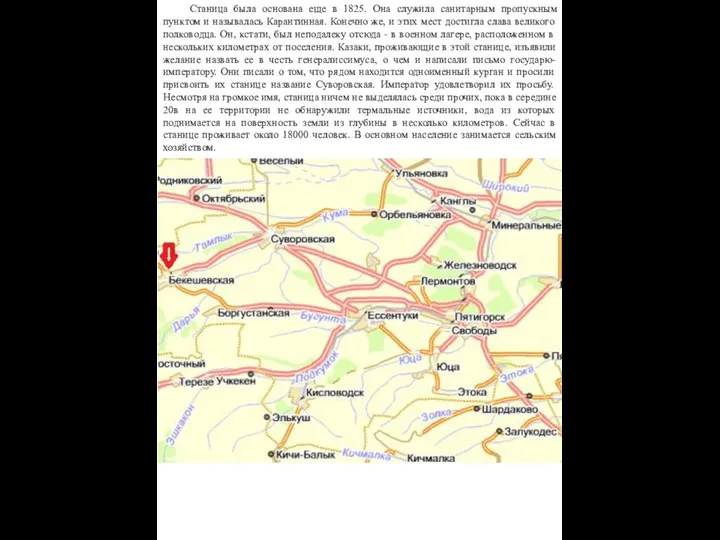

Родительское собрание на тему:Здоровье детей в наших руках Суворовские источники

Суворовские источники Курсы подготовки вэб-разработчиков

Курсы подготовки вэб-разработчиков Теоретико-практическая система Галена и ее влияние на развитие медицины во II в. – XVI в

Теоретико-практическая система Галена и ее влияние на развитие медицины во II в. – XVI в Модель компетенций персонала ООО Евросеть

Модель компетенций персонала ООО Евросеть Слова с удвоенными согласными

Слова с удвоенными согласными урок 3 класс. месяцы

урок 3 класс. месяцы Ноосферное образование: теория и практика

Ноосферное образование: теория и практика Непосредственное, прямое народовластие. (Тема 7)

Непосредственное, прямое народовластие. (Тема 7) Тренинг: Азбука предпринимателя. День 3

Тренинг: Азбука предпринимателя. День 3 Технология изготовления окантовочного шва

Технология изготовления окантовочного шва Презентация Витамины наши друзья

Презентация Витамины наши друзья Свидетель эпохи. Жак-Луи Давид

Свидетель эпохи. Жак-Луи Давид Команда присаивания

Команда присаивания Жизнь и творчество Дмитрия Ивановича Менделеева.

Жизнь и творчество Дмитрия Ивановича Менделеева. Кирилл и Мефодий. Гимн и Величание

Кирилл и Мефодий. Гимн и Величание презентация Масленица

презентация Масленица Конспект занятия по теме: Изготовление открытки Розы для мамы

Конспект занятия по теме: Изготовление открытки Розы для мамы Презентация Наша Родина

Презентация Наша Родина Быт и обычаи России в 19 веке. 2 часть

Быт и обычаи России в 19 веке. 2 часть Современный урок. Методические требования к современному уроку

Современный урок. Методические требования к современному уроку Патриотическое воспитание как одна из задач воспитания подрастающего поколения

Патриотическое воспитание как одна из задач воспитания подрастающего поколения Птицы Волгоградской области. Семейство утиных

Птицы Волгоградской области. Семейство утиных Мышкинский муниципальный район. Волонтерский отряд Вместе - мы сила!

Мышкинский муниципальный район. Волонтерский отряд Вместе - мы сила!