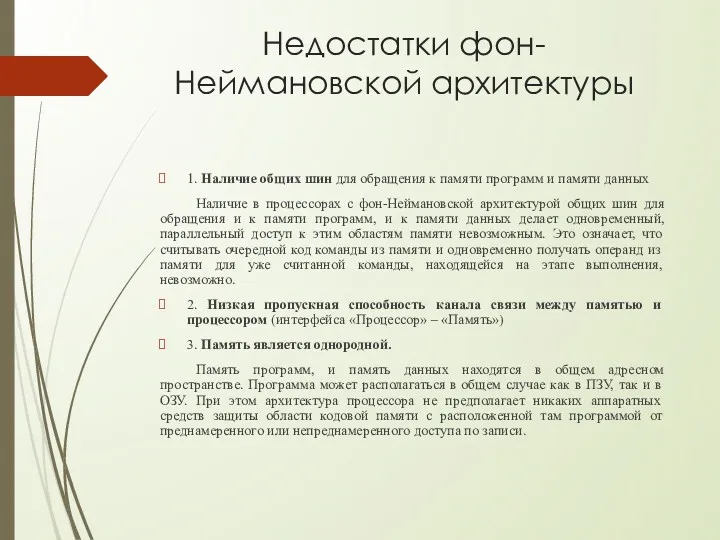

1. Наличие общих шин для обращения к памяти программ и памяти

данных

Наличие в процессорах с фон-Неймановской архитектурой общих шин для обращения и к памяти программ, и к памяти данных делает одновременный, параллельный доступ к этим областям памяти невозможным. Это означает, что считывать очередной код команды из памяти и одновременно получать операнд из памяти для уже считанной команды, находящейся на этапе выполнения, невозможно.

2. Низкая пропускная способность канала связи между памятью и процессором (интерфейса «Процессор» – «Память»)

3. Память является однородной.

Память программ, и память данных находятся в общем адресном пространстве. Программа может располагаться в общем случае как в ПЗУ, так и в ОЗУ. При этом архитектура процессора не предполагает никаких аппаратных средств защиты области кодовой памяти с расположенной там программой от преднамеренного или непреднамеренного доступа по записи.

Недостатки фон-Неймановской архитектуры

Качество товаров

Качество товаров Презентация к сказке Колосок

Презентация к сказке Колосок Westfälische Wilhelms-Universität Münster

Westfälische Wilhelms-Universität Münster Экономический кризис 1998 года

Экономический кризис 1998 года Морские волны, возникающие при подводных и прибрежных землетрясениях - цунами

Морские волны, возникающие при подводных и прибрежных землетрясениях - цунами Студенческая футбольная лига

Студенческая футбольная лига Бассүйек-ми жарақаты

Бассүйек-ми жарақаты Признаки делимости натуральных чисел от 2 до 25 и на 50

Признаки делимости натуральных чисел от 2 до 25 и на 50 Замена пролетных строений консольными кранами

Замена пролетных строений консольными кранами Автоматическая установка умягчения воды непрерывного действия Passion for Progress © BMA

Автоматическая установка умягчения воды непрерывного действия Passion for Progress © BMA Новый Год шагает по планете. Викторина

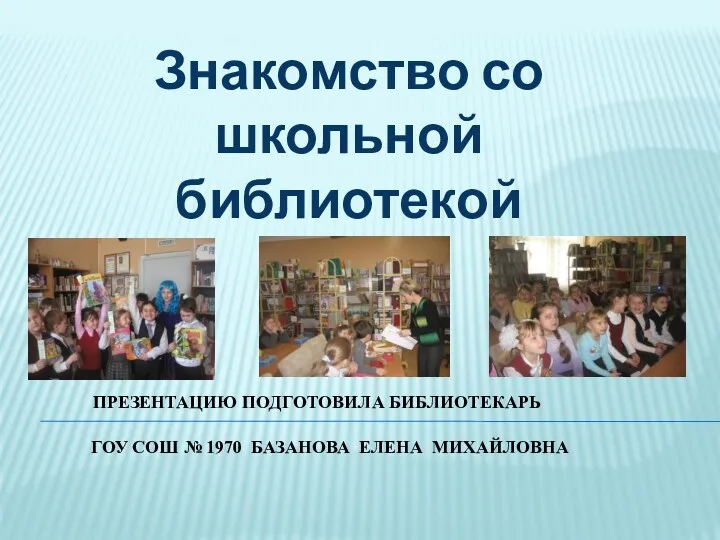

Новый Год шагает по планете. Викторина Презентация Школьная библиотека

Презентация Школьная библиотека Профессии, связанные с созданием изделий из древесины и древесных материалов

Профессии, связанные с созданием изделий из древесины и древесных материалов Слюна и ротовая жидкость

Слюна и ротовая жидкость Информационные технологии как система. Лекция 1

Информационные технологии как система. Лекция 1 Ароматические углеводороды

Ароматические углеводороды Знакомьтесь. Геометрия

Знакомьтесь. Геометрия 20230612_algebra_9_klass_presentatsia_generalnai_sovokupnost_i_viborka

20230612_algebra_9_klass_presentatsia_generalnai_sovokupnost_i_viborka Проект Скоро в школу!

Проект Скоро в школу! Полномочия прокурора возбужденным по делам в виду новых или вновь открывшихся обстоятельств

Полномочия прокурора возбужденным по делам в виду новых или вновь открывшихся обстоятельств Введение в Delphi. (Лекция 2)

Введение в Delphi. (Лекция 2) ФЗ О бухгалтерском учете

ФЗ О бухгалтерском учете Шарик улетел.

Шарик улетел. Бактериофагия, бактериофаги

Бактериофагия, бактериофаги Шкільна форма

Шкільна форма Ярославская область. Основные социально-экономические показатели

Ярославская область. Основные социально-экономические показатели творчество В.М. Васнецова Наши сказки

творчество В.М. Васнецова Наши сказки Звук Ль Диск Диск Диск

Звук Ль Диск Диск Диск