Содержание

- 2. Системы счисления Изначально число – способ выражения количества предметов или количественного отношения между предметами Можно придумать

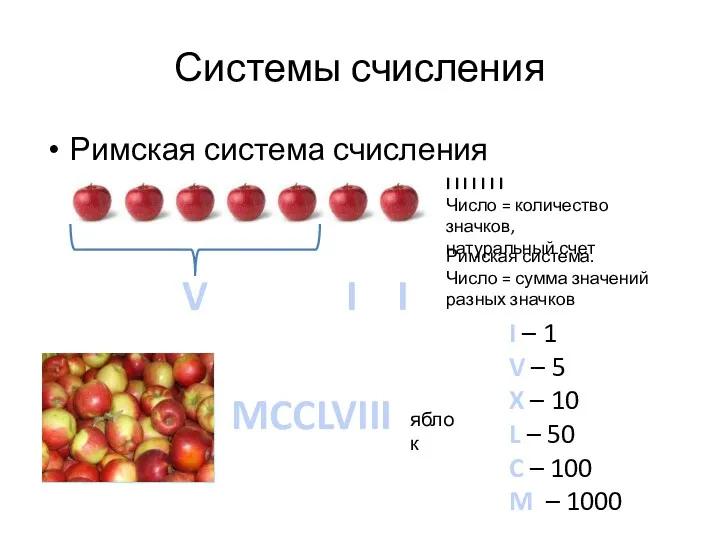

- 3. Римская система счисления Системы счисления V I I I I I I I I I Число

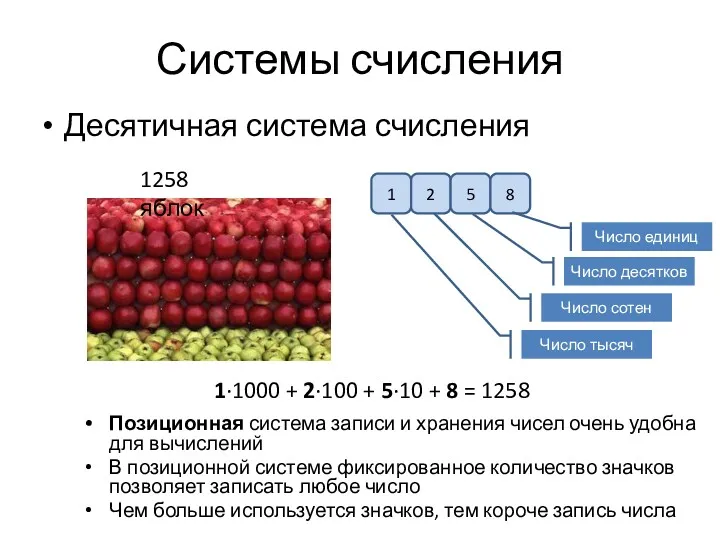

- 4. Системы счисления Десятичная система счисления Позиционная система записи и хранения чисел очень удобна для вычислений В

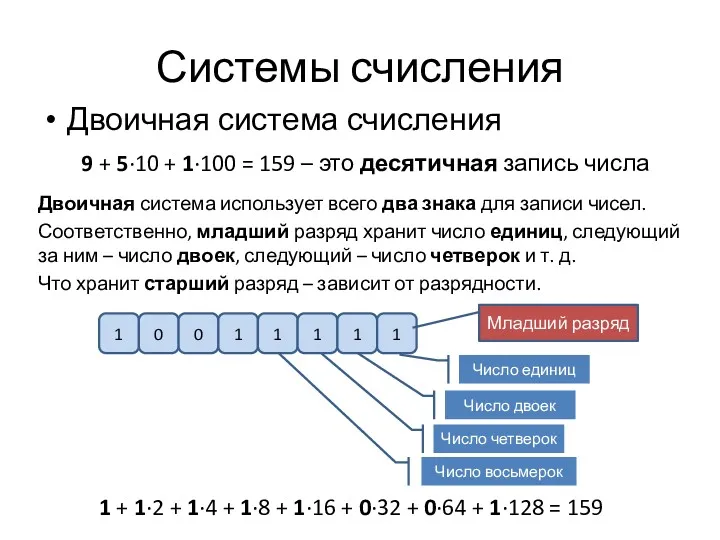

- 5. Системы счисления Двоичная система счисления 9 + 5∙10 + 1∙100 = 159 – это десятичная запись

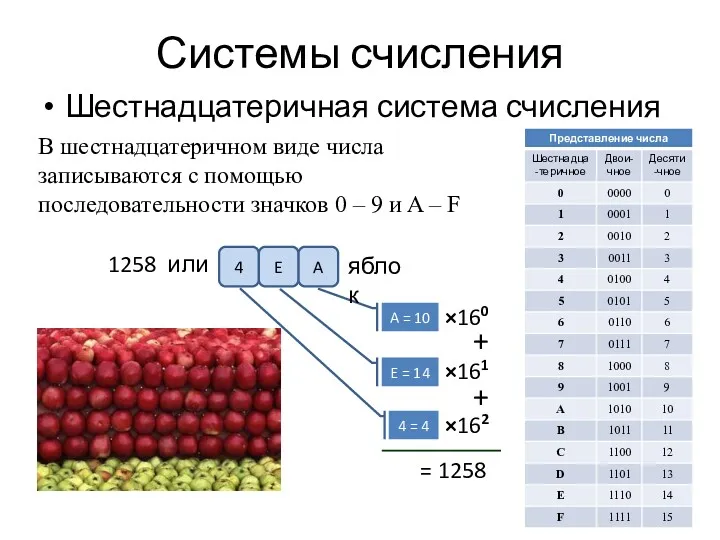

- 6. Системы счисления Шестнадцатеричная система счисления В шестнадцатеричном виде числа записываются с помощью последовательности значков 0 –

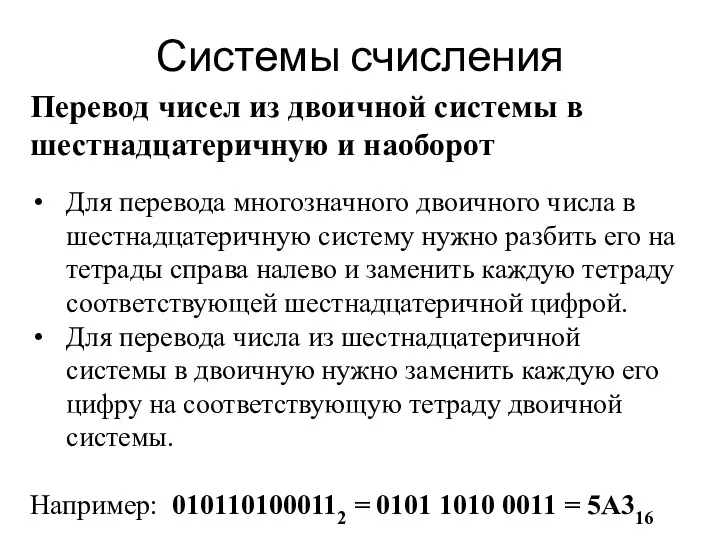

- 7. Системы счисления Перевод чисел из двоичной системы в шестнадцатеричную и наоборот Для перевода многозначного двоичного числа

- 8. Логические устройства Основные положения алгебры логики Переменная величина Х в алгебре логики может принимать: Х =

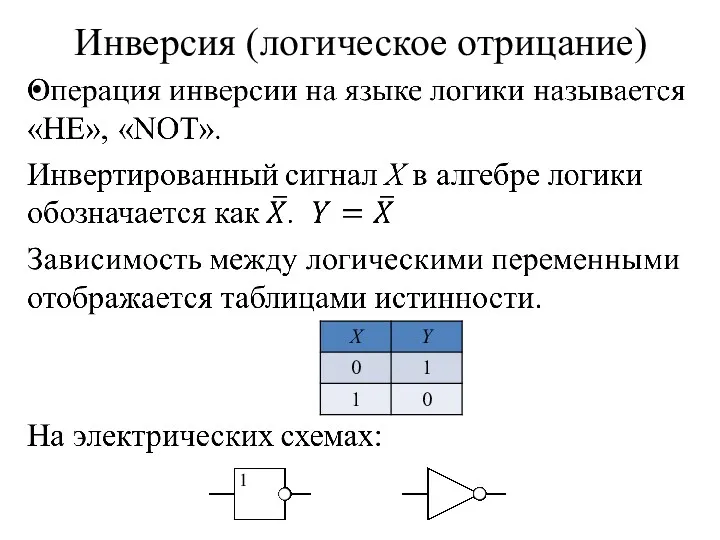

- 9. Инверсия (логическое отрицание)

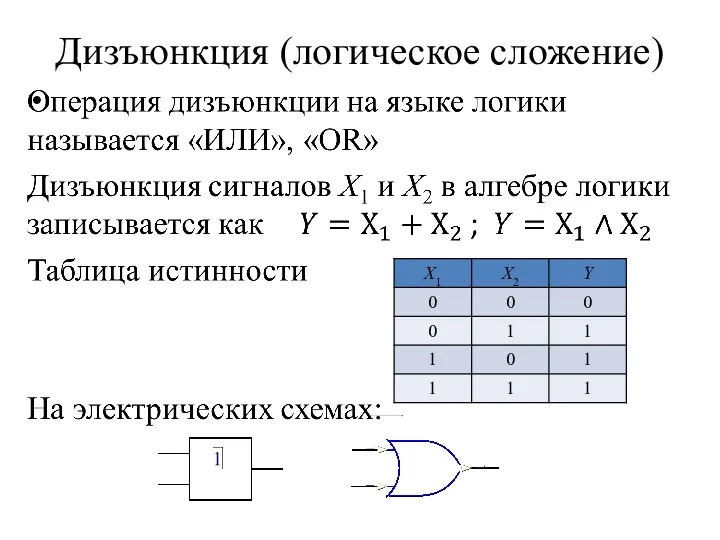

- 10. Дизъюнкция (логическое сложение)

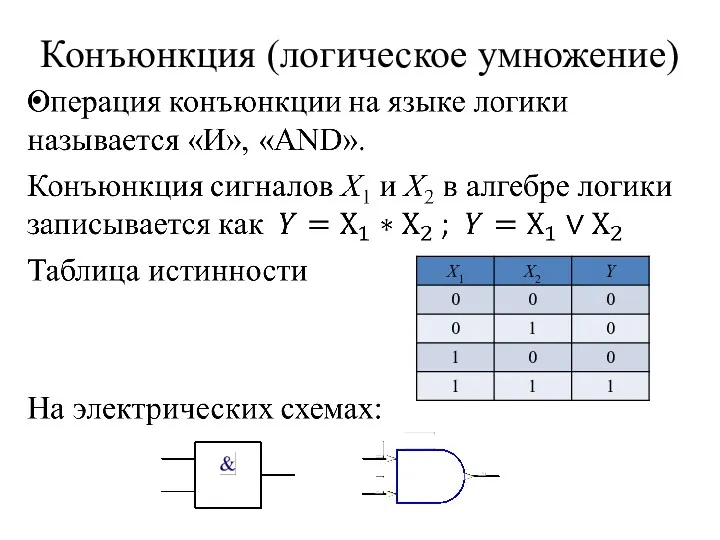

- 11. Конъюнкция (логическое умножение)

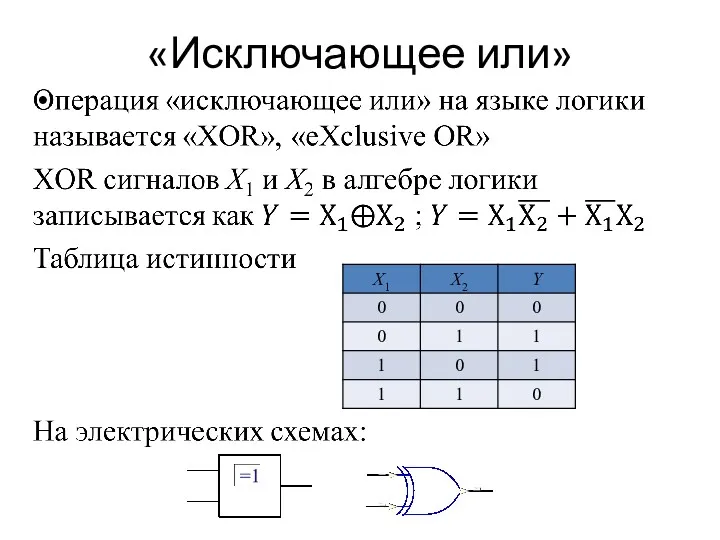

- 12. «Исключающее или»

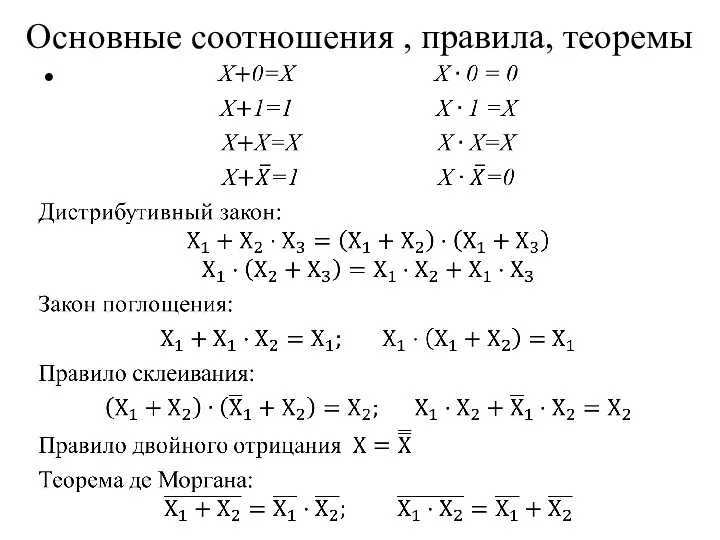

- 13. Основные соотношения , правила, теоремы

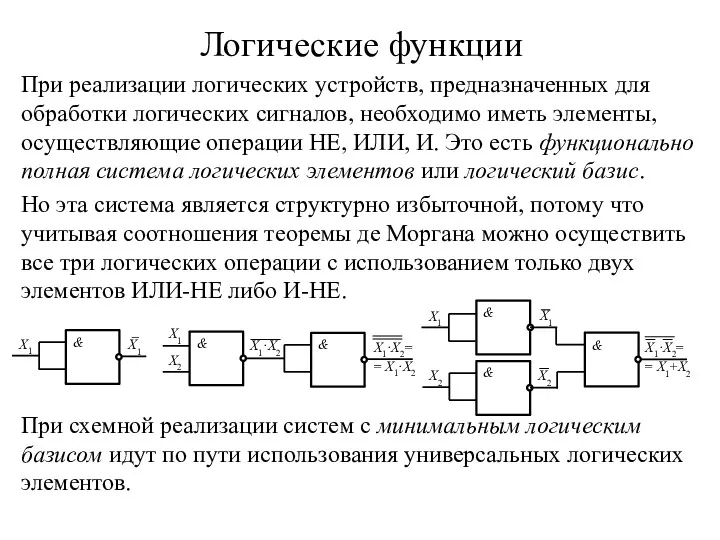

- 14. Логические функции При реализации логических устройств, предназначенных для обработки логических сигналов, необходимо иметь элементы, осуществляющие операции

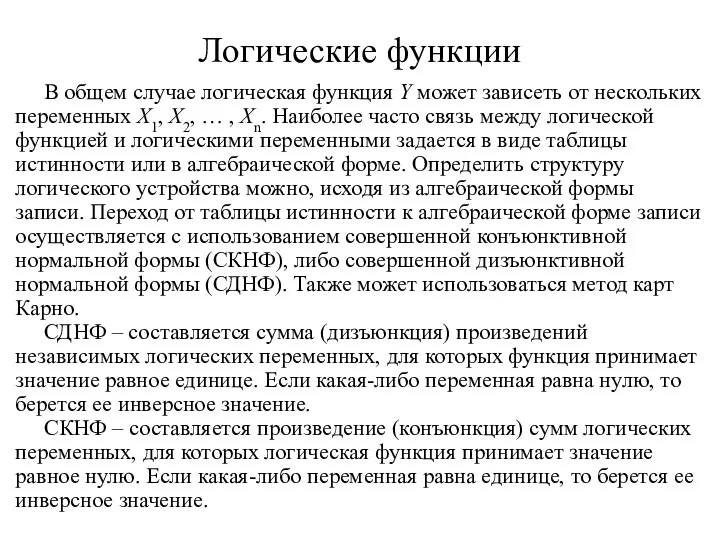

- 15. Логические функции В общем случае логическая функция Y может зависеть от нескольких переменных X1, X2, …

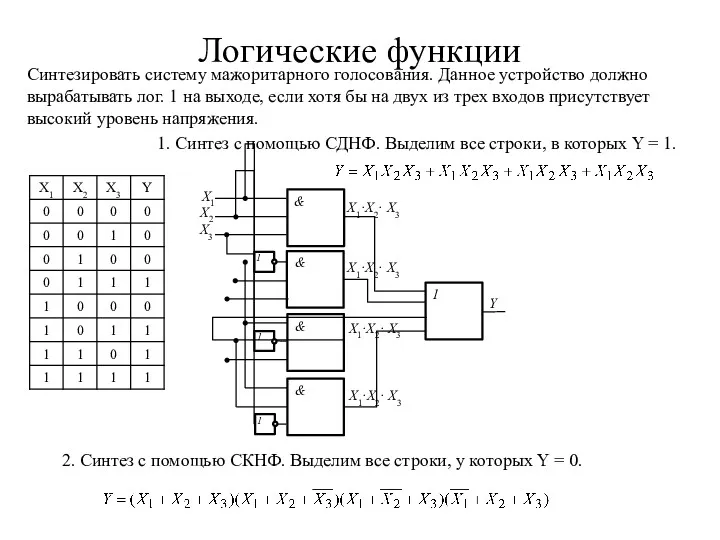

- 16. Логические функции Синтезировать систему мажоритарного голосования. Данное устройство должно вырабатывать лог. 1 на выходе, если хотя

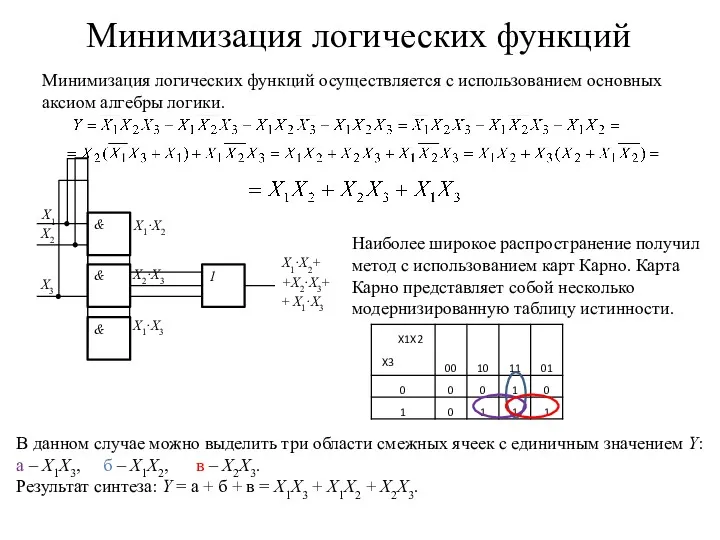

- 17. Минимизация логических функций Минимизация логических функций осуществляется с использованием основных аксиом алгебры логики. Наиболее широкое распространение

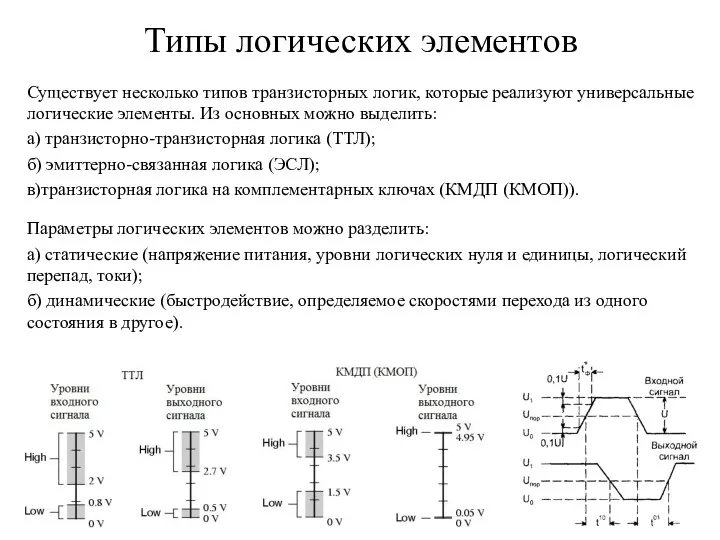

- 18. Типы логических элементов Существует несколько типов транзисторных логик, которые реализуют универсальные логические элементы. Из основных можно

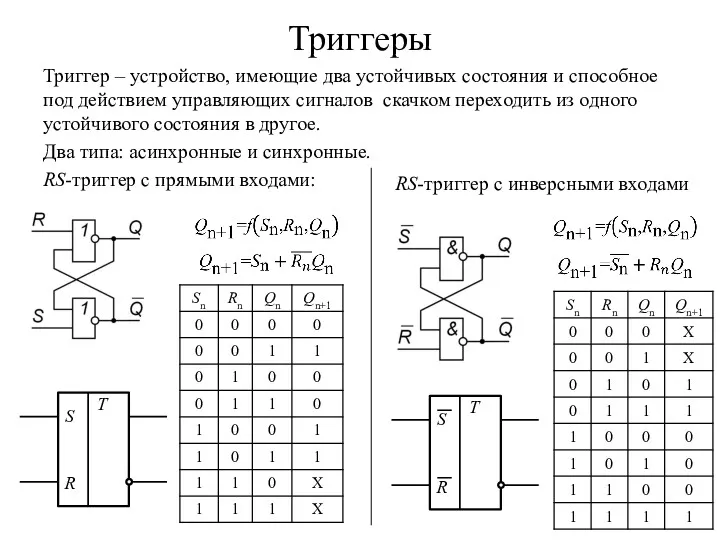

- 19. Триггеры Триггер – устройство, имеющие два устойчивых состояния и способное под действием управляющих сигналов скачком переходить

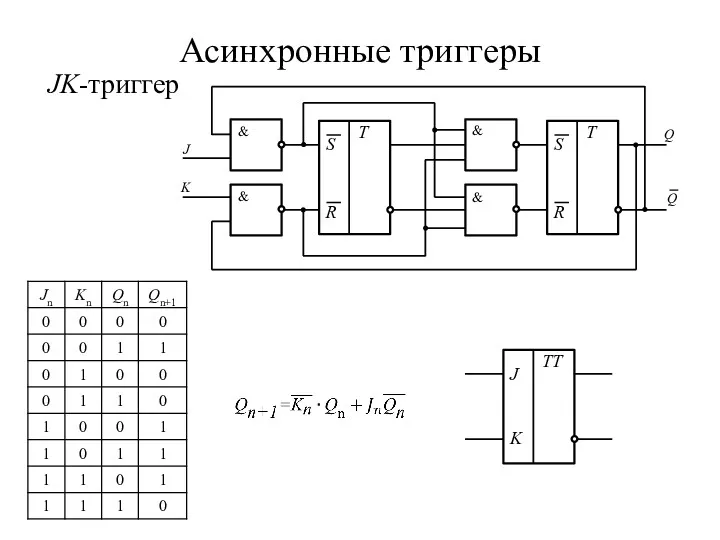

- 20. Асинхронные триггеры JK-триггер

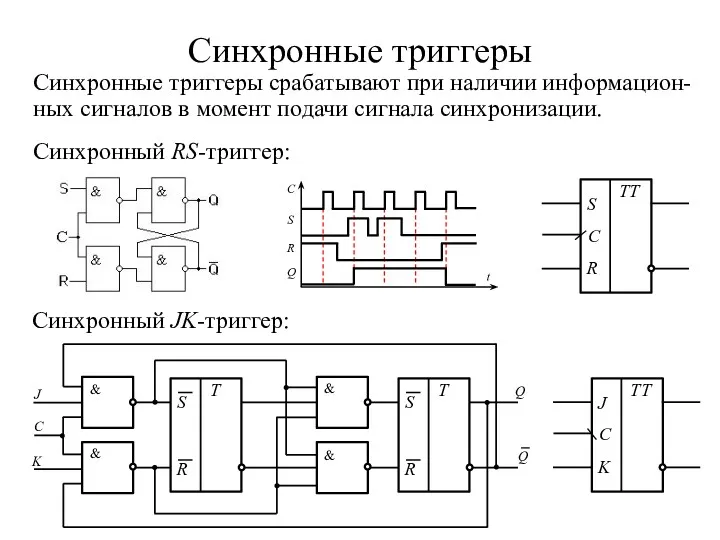

- 21. Синхронные триггеры Синхронные триггеры срабатывают при наличии информацион- ных сигналов в момент подачи сигнала синхронизации. Синхронный

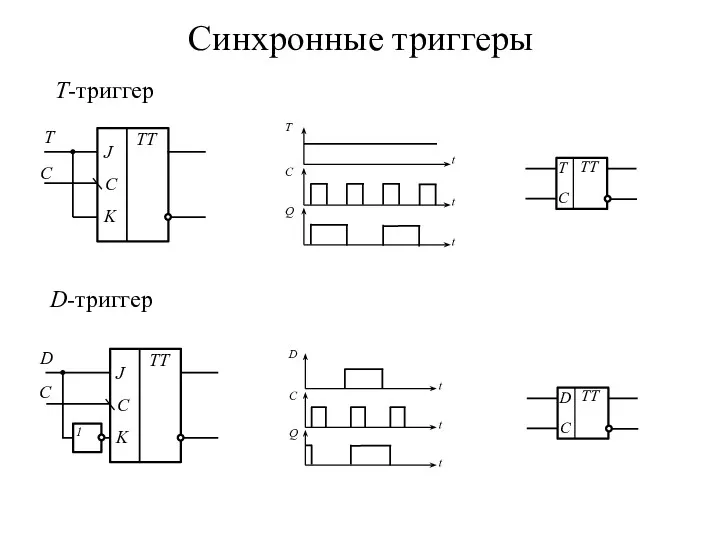

- 22. Синхронные триггеры Т-триггер D-триггер

- 23. Несимметричный триггер

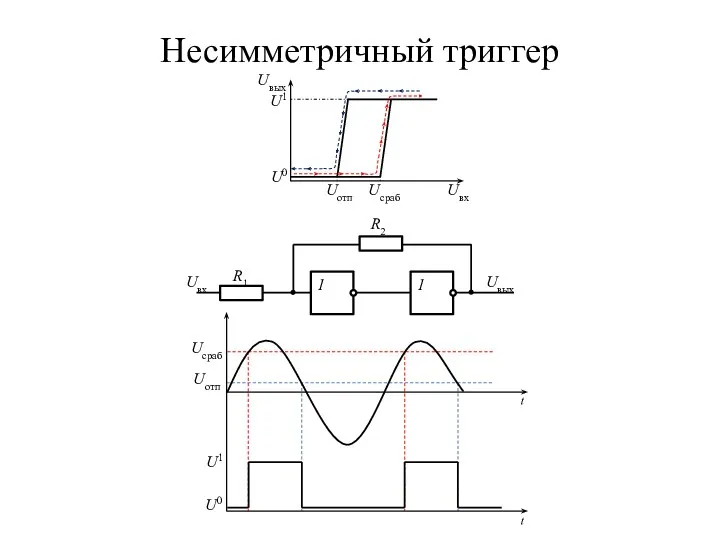

- 24. Цифровые функциональные узлы Это устройство, предназначенное для выполнения определенных действий с двоичными переменными: сложение, преобразование, счет,

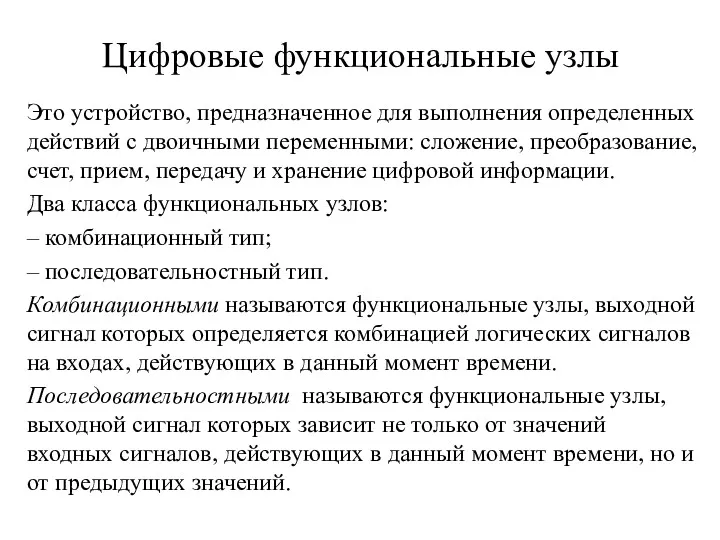

- 25. Шифратор Функциональный узел, предназначенный для преобразования поступающих на его входы управляющих сигналов (команд) в n-разрядный двоичный

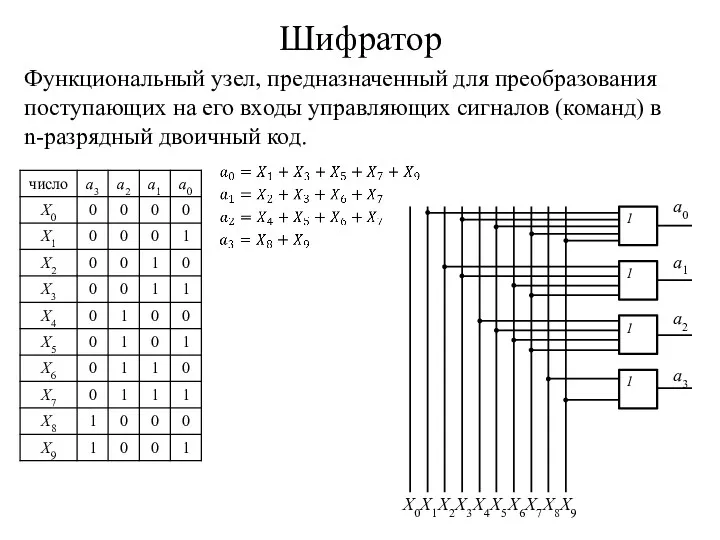

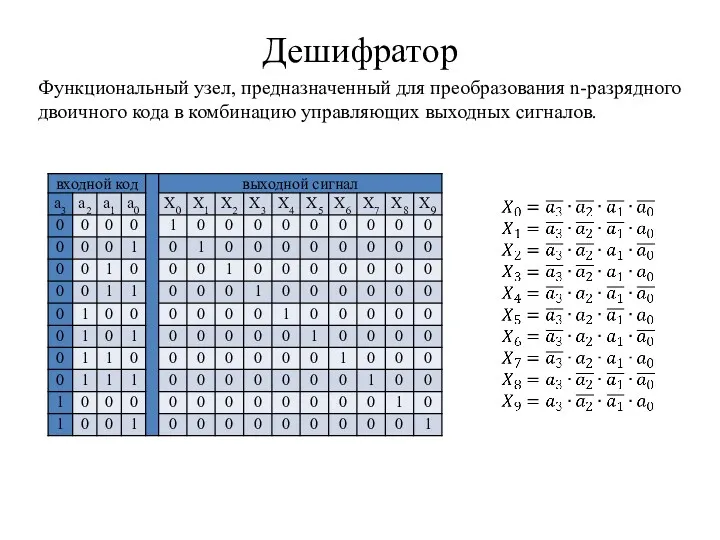

- 26. Дешифратор Функциональный узел, предназначенный для преобразования n-разрядного двоичного кода в комбинацию управляющих выходных сигналов.

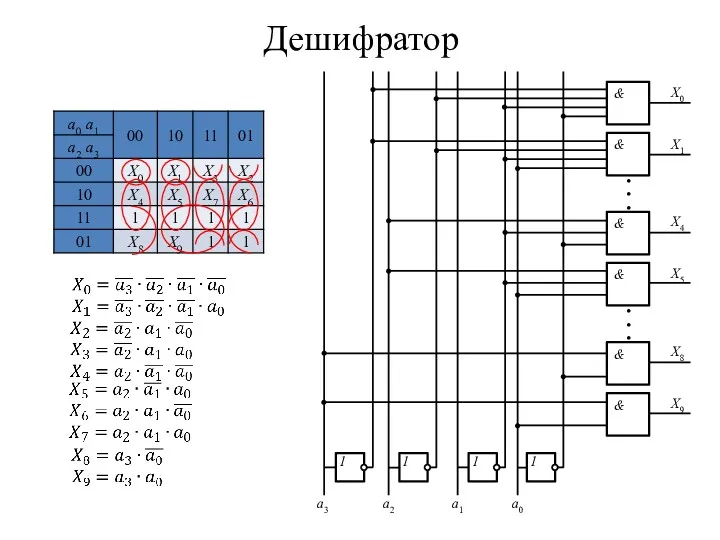

- 27. Дешифратор

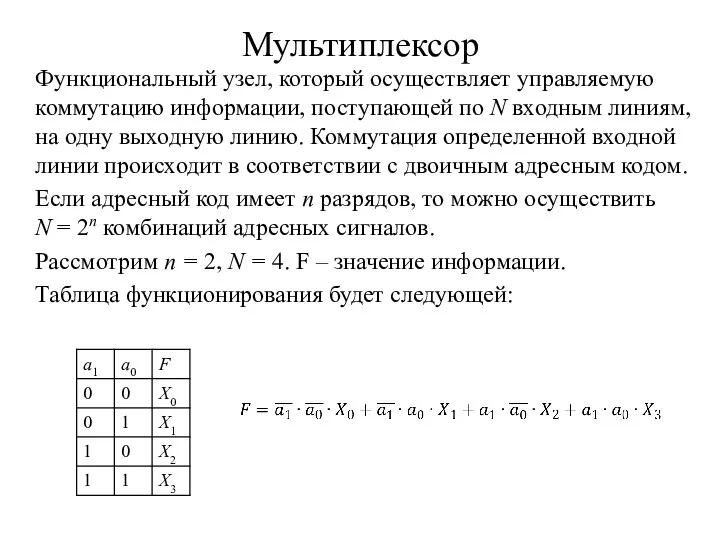

- 28. Мультиплексор Функциональный узел, который осуществляет управляемую коммутацию информации, поступающей по N входным линиям, на одну выходную

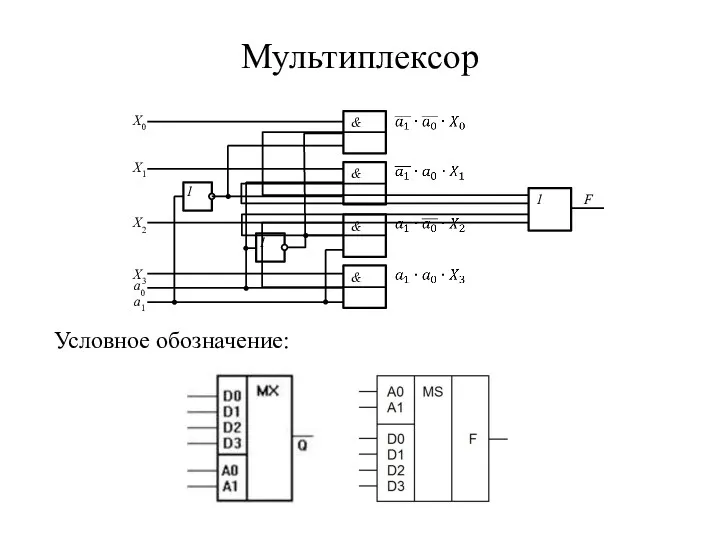

- 29. Мультиплексор Условное обозначение:

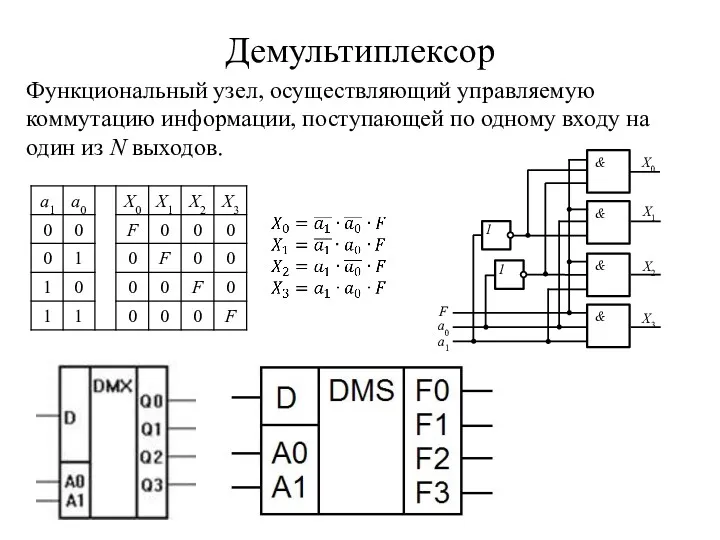

- 30. Демультиплексор Функциональный узел, осуществляющий управляемую коммутацию информации, поступающей по одному входу на один из N выходов.

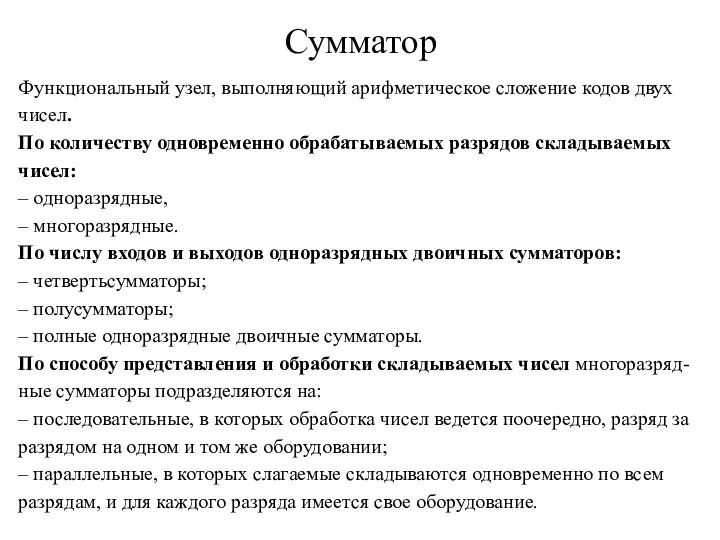

- 31. Сумматор Функциональный узел, выполняющий арифметическое сложение кодов двух чисел. По количеству одновременно обрабатываемых разрядов складываемых чисел:

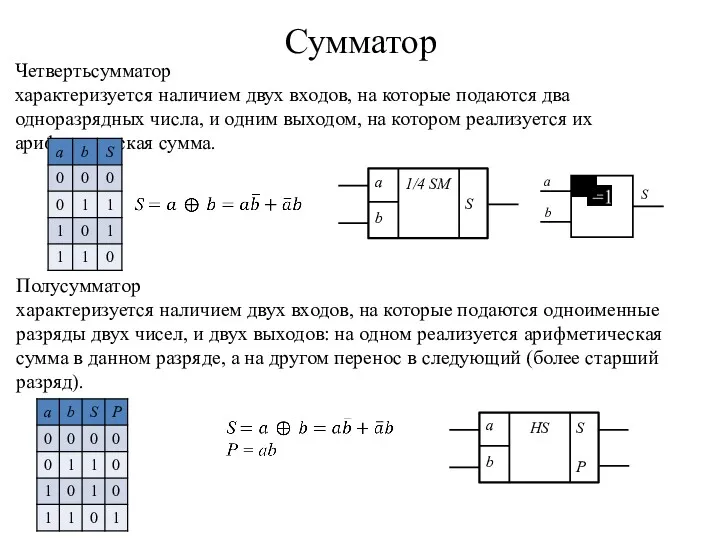

- 32. Сумматор Четвертьсумматор характеризуется наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на

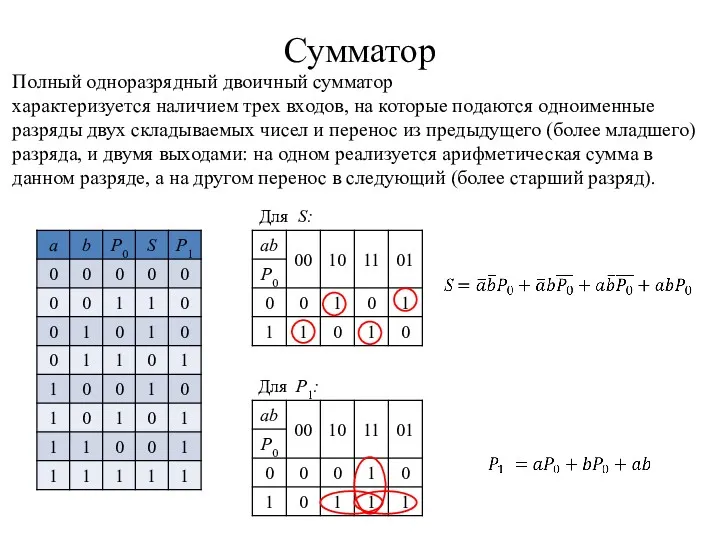

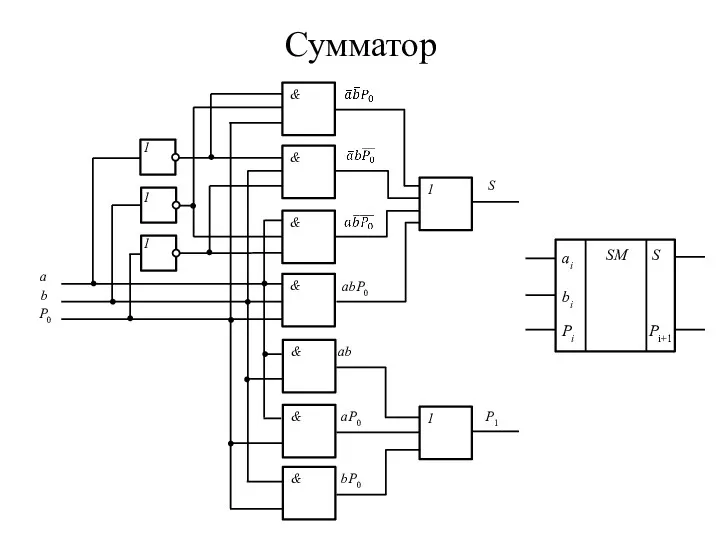

- 33. Сумматор Полный одноразрядный двоичный сумматор характеризуется наличием трех входов, на которые подаются одноименные разряды двух складываемых

- 34. Сумматор

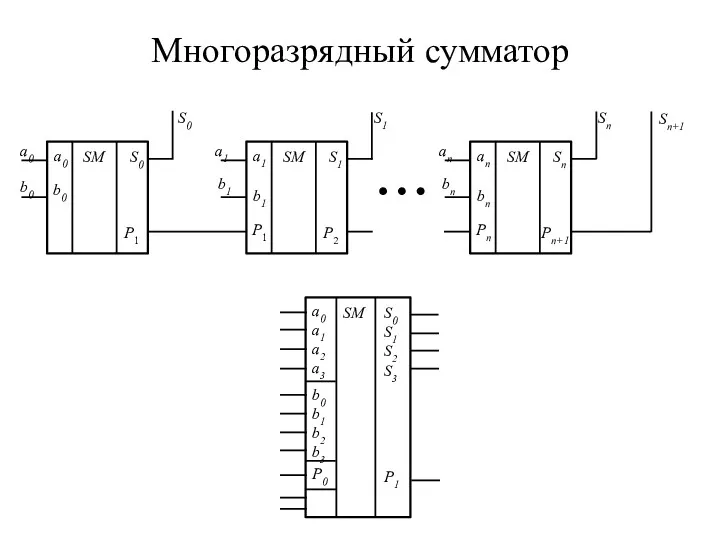

- 35. Многоразрядный сумматор

- 36. Функциональные узлы последовательностного типа Регистры Функциональный узел, осуществляющий прием, хранение и передачу информации. 2 типа регистров:

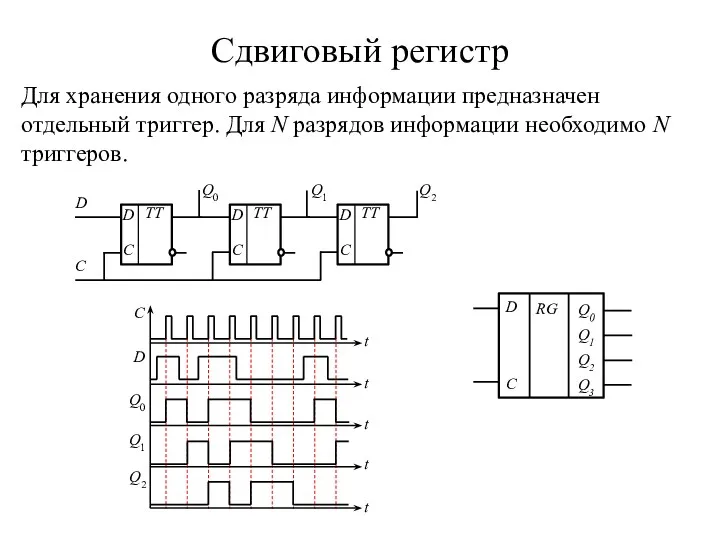

- 37. Сдвиговый регистр Для хранения одного разряда информации предназначен отдельный триггер. Для N разрядов информации необходимо N

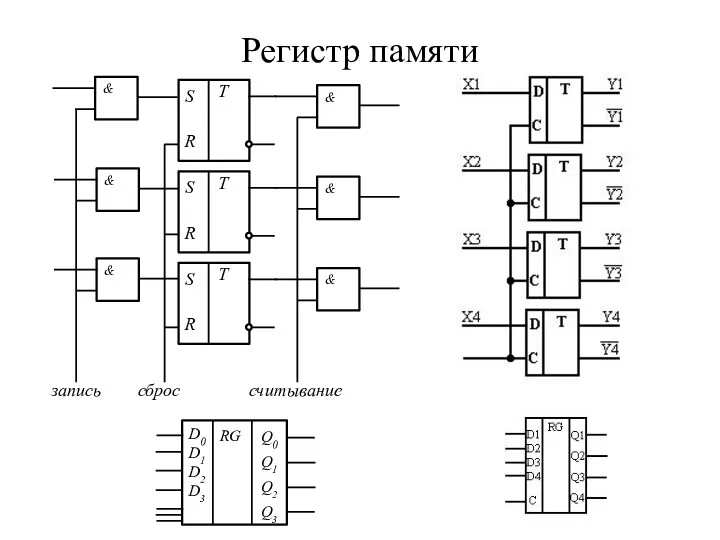

- 38. Регистр памяти

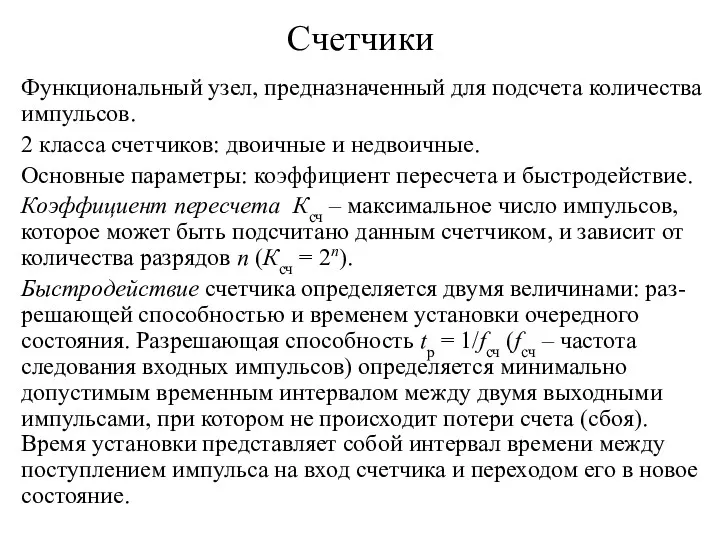

- 39. Счетчики Функциональный узел, предназначенный для подсчета количества импульсов. 2 класса счетчиков: двоичные и недвоичные. Основные параметры:

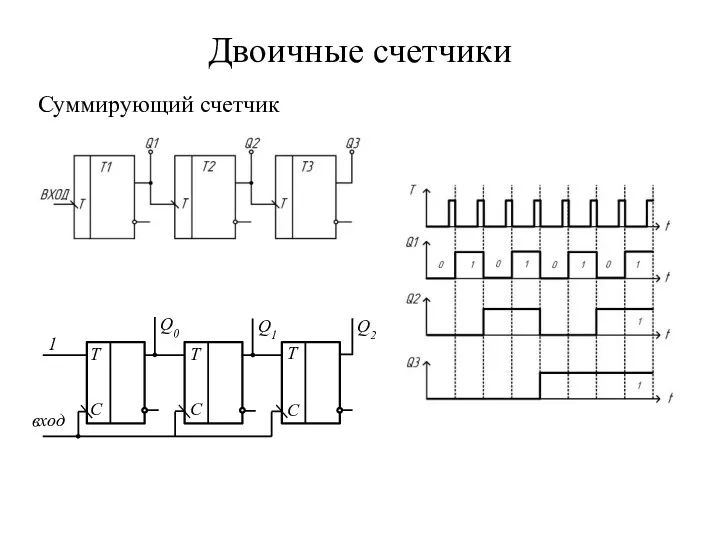

- 40. Двоичные счетчики Суммирующий счетчик

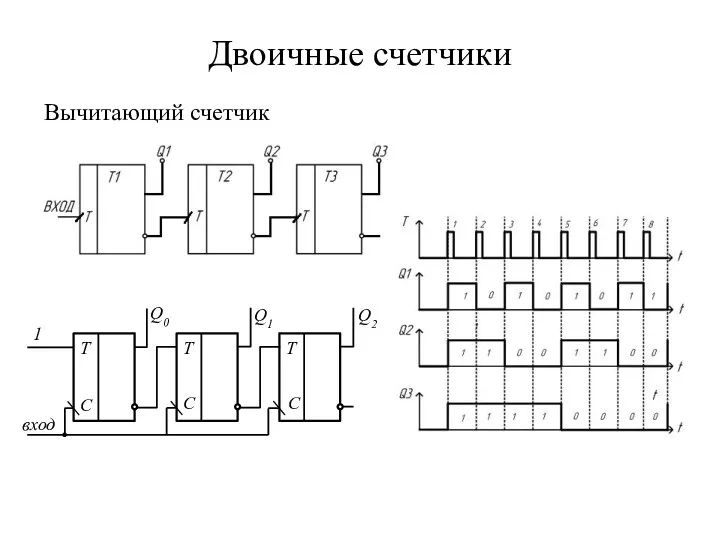

- 41. Двоичные счетчики Вычитающий счетчик

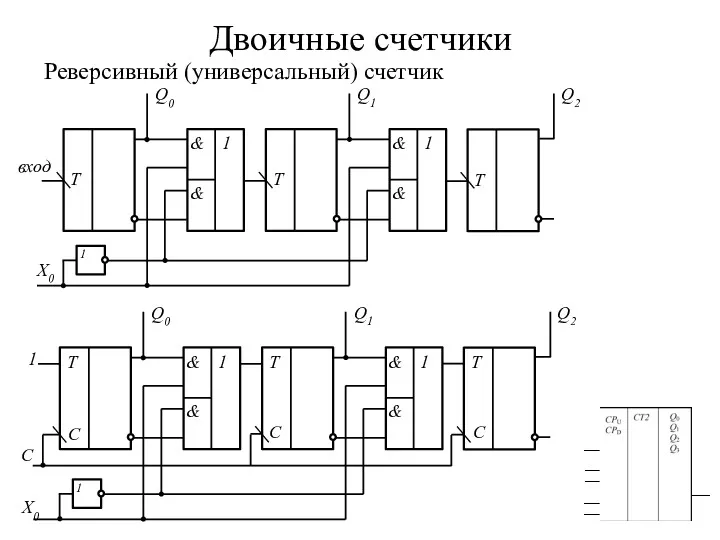

- 42. Двоичные счетчики Реверсивный (универсальный) счетчик

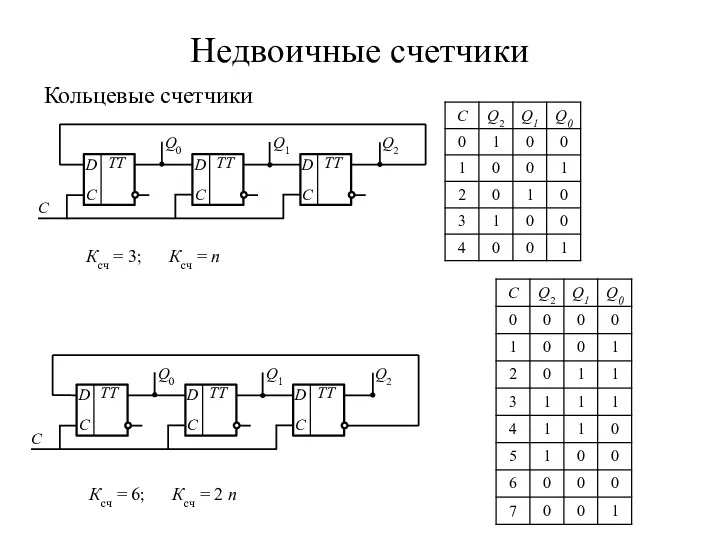

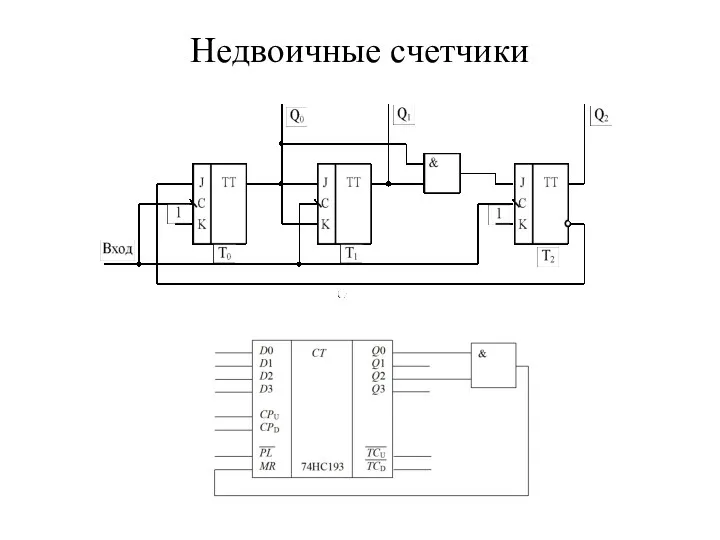

- 43. Недвоичные счетчики Кольцевые счетчики Ксч = 3; Ксч = n Ксч = 6; Ксч = 2

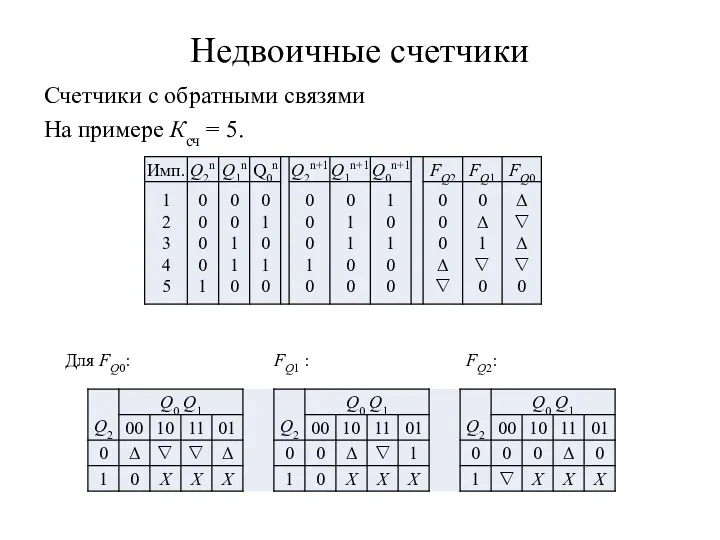

- 44. Недвоичные счетчики Счетчики с обратными связями На примере Ксч = 5. Для FQ0: FQ1 : FQ2:

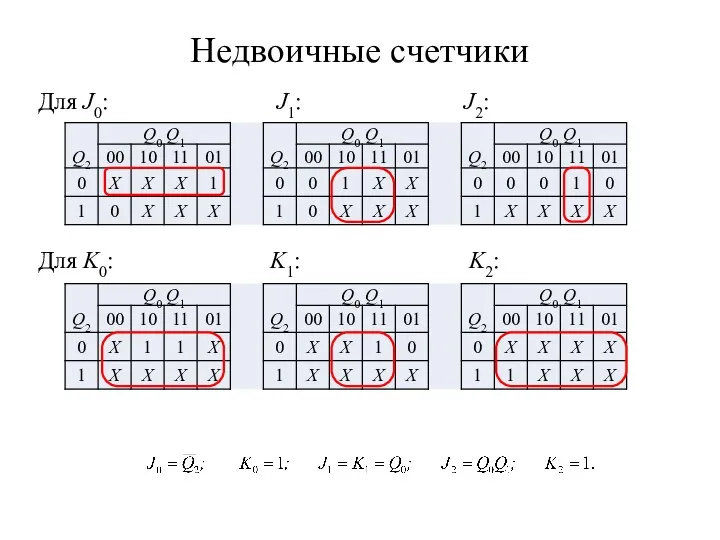

- 45. Недвоичные счетчики Для J0: J1: J2: Для K0: K1: K2:

- 46. Недвоичные счетчики

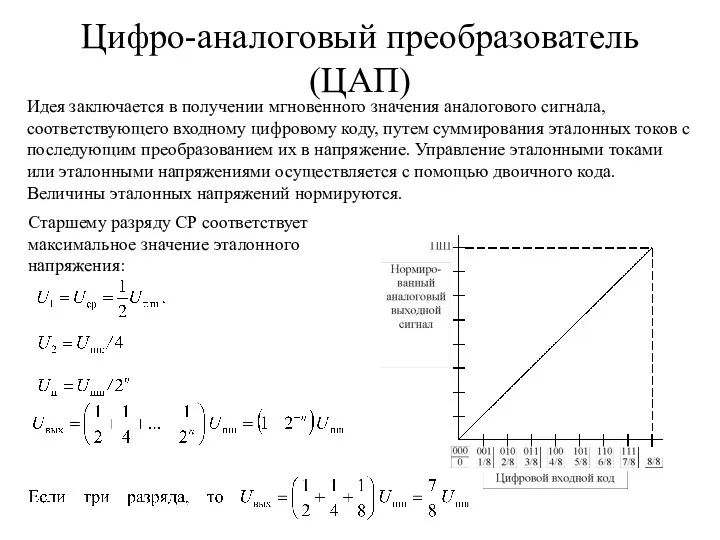

- 47. Цифро-аналоговый преобразователь (ЦАП) Идея заключается в получении мгновенного значения аналогового сигнала, соответствующего входному цифровому коду, путем

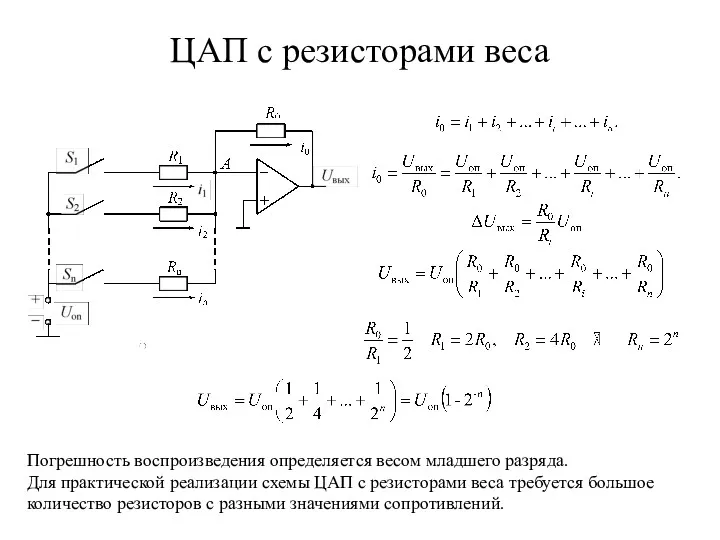

- 48. ЦАП с резисторами веса Погрешность воспроизведения определяется весом младшего разряда. Для практической реализации схемы ЦАП с

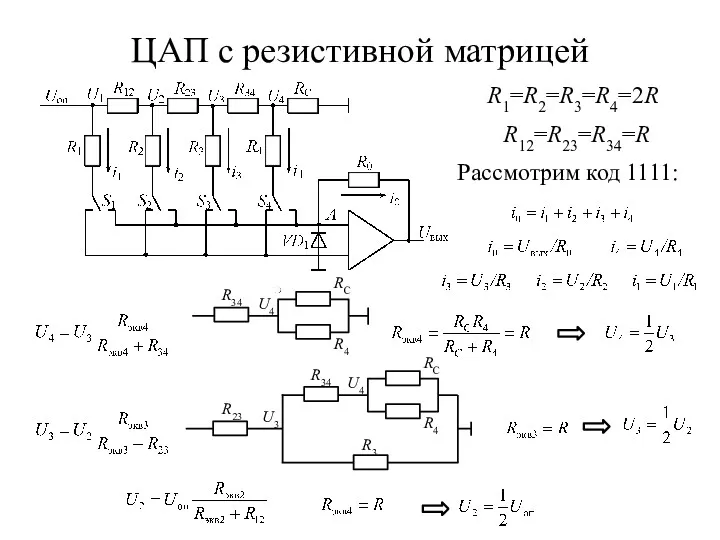

- 49. ЦАП с резистивной матрицей R1=R2=R3=R4=2R R12=R23=R34=R Рассмотрим код 1111:

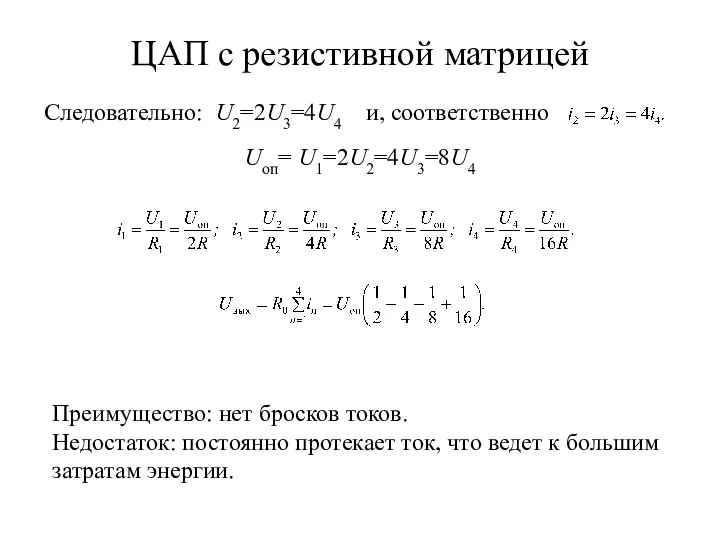

- 50. ЦАП с резистивной матрицей Следовательно: U2=2U3=4U4 и, соответственно Uоп= U1=2U2=4U3=8U4 Преимущество: нет бросков токов. Недостаток: постоянно

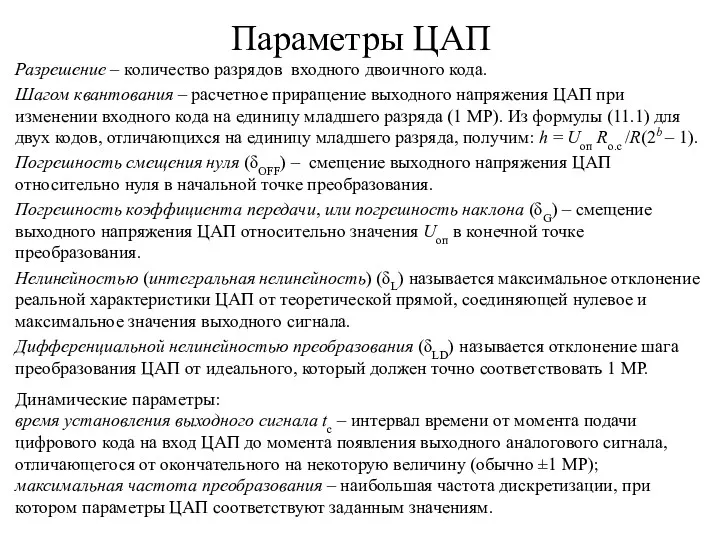

- 51. Параметры ЦАП Разрешение – количество разрядов входного двоичного кода. Шагом квантования – расчетное приращение выходного напряжения

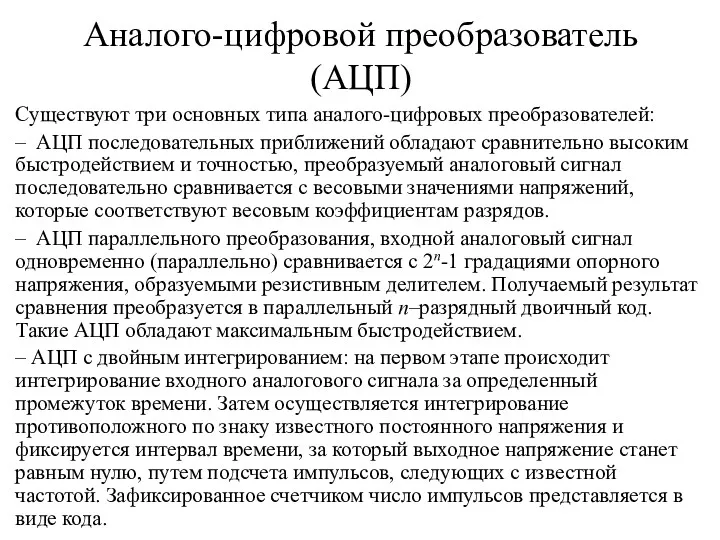

- 52. Аналого-цифровой преобразователь (АЦП) Существуют три основных типа аналого-цифровых преобразователей: – АЦП последовательных приближений обладают сравнительно высоким

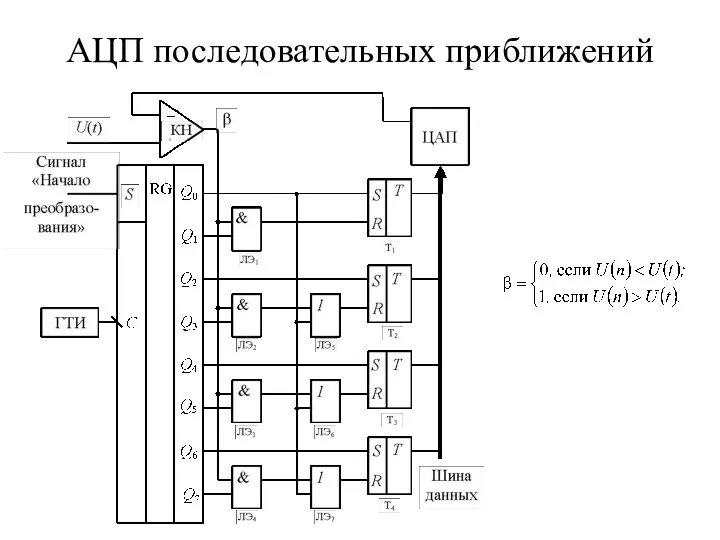

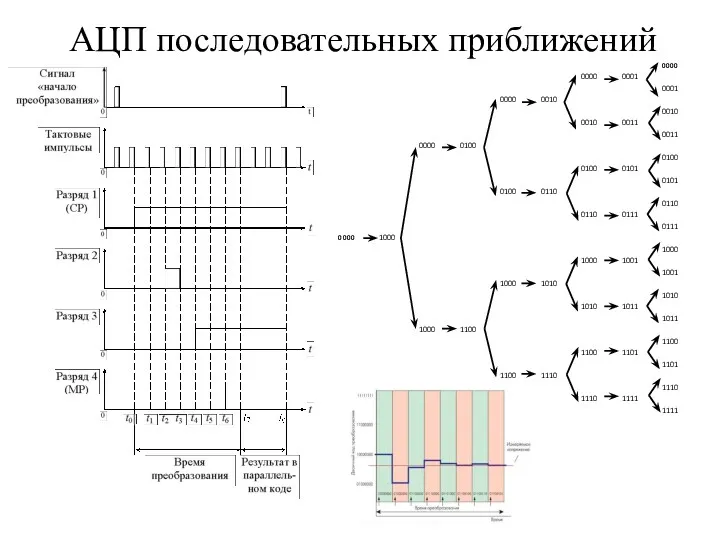

- 53. АЦП последовательных приближений

- 54. АЦП последовательных приближений

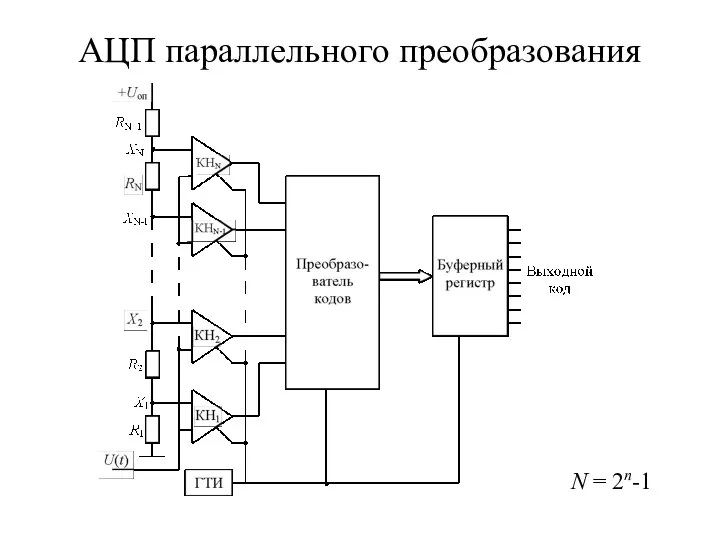

- 55. АЦП параллельного преобразования N = 2n-1

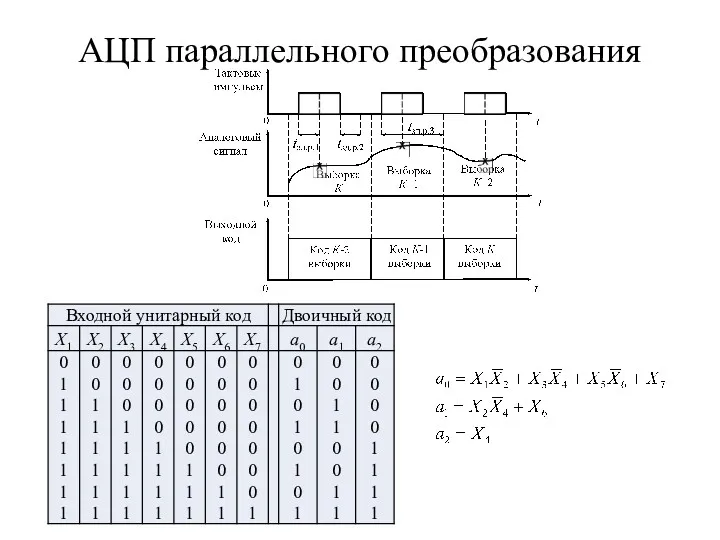

- 56. АЦП параллельного преобразования

- 57. АЦП с двойным интегрированием

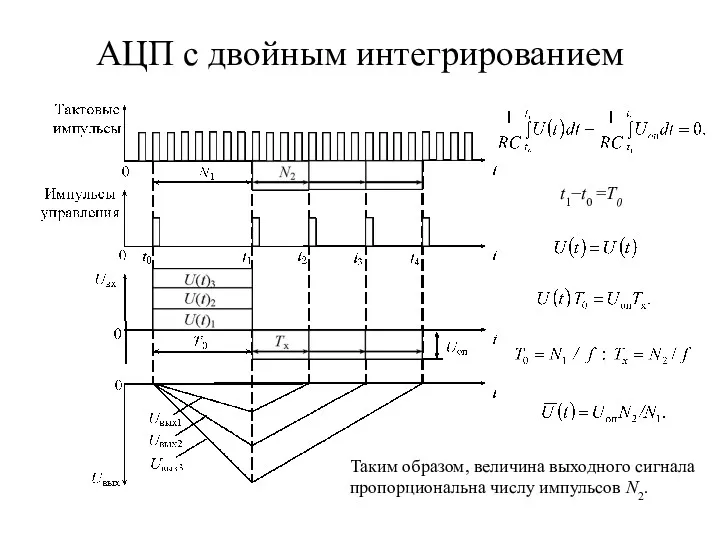

- 58. АЦП с двойным интегрированием t1−t0 =Т0 Таким образом, величина выходного сигнала пропорциональна числу импульсов N2.

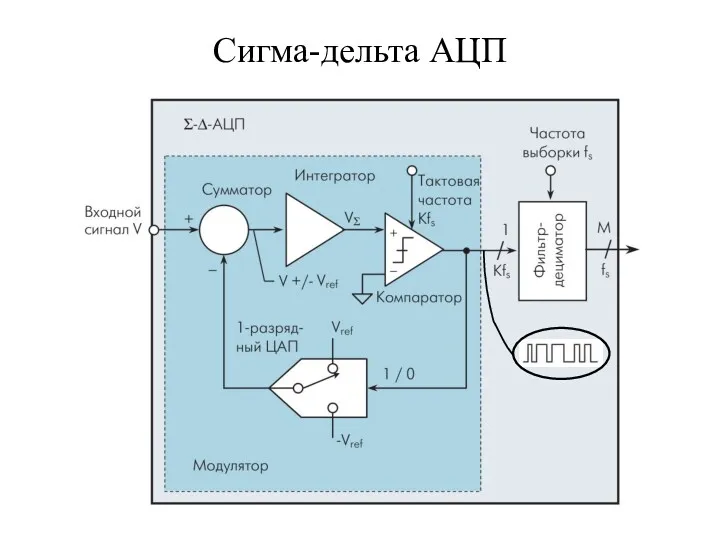

- 59. Сигма-дельта АЦП

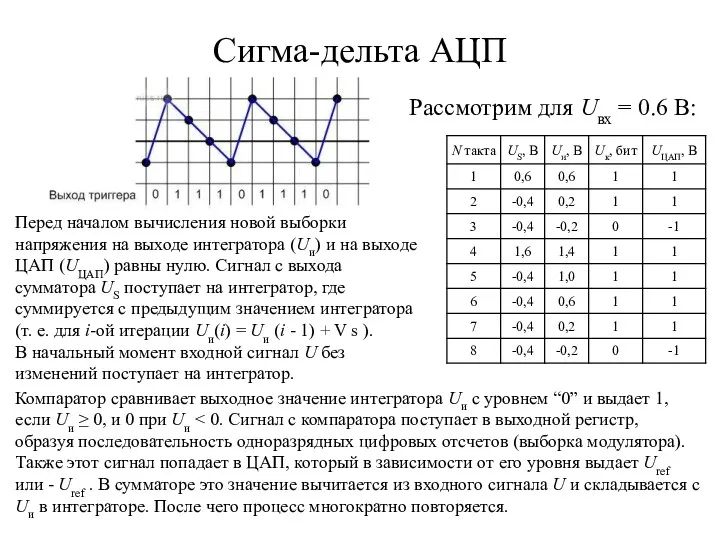

- 60. Сигма-дельта АЦП Рассмотрим для Uвх = 0.6 В: Перед началом вычисления новой выборки напряжения на выходе

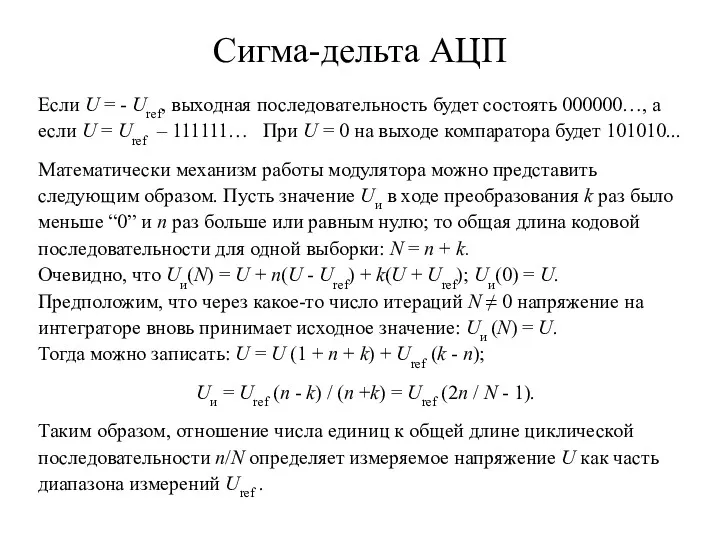

- 61. Сигма-дельта АЦП Если U = - Uref, выходная последовательность будет состоять 000000…, а если U =

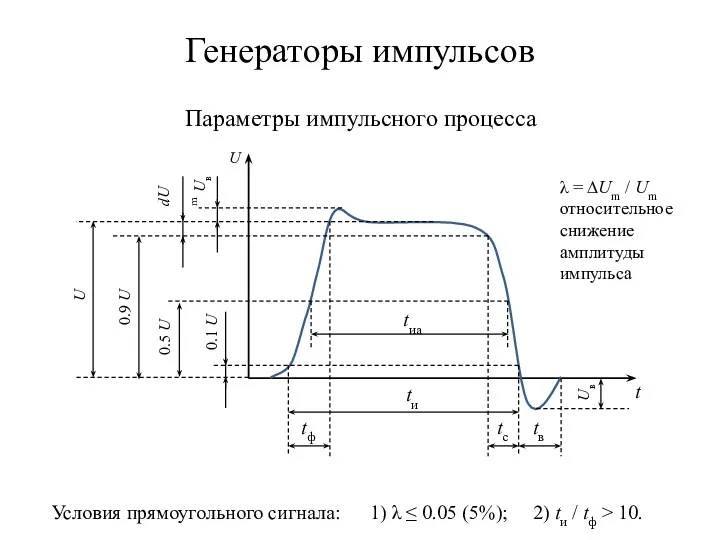

- 62. Генераторы импульсов Параметры импульсного процесса Условия прямоугольного сигнала: 1) λ ≤ 0.05 (5%); 2) tи /

- 63. Параметры импульсного процесса Сигнал — физический процесс, несущий информацию. По природе физического процесса делятся на электромагнитные,

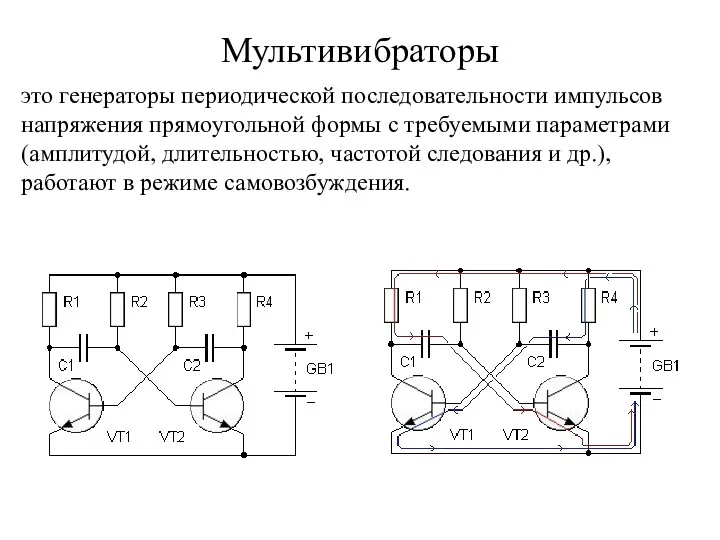

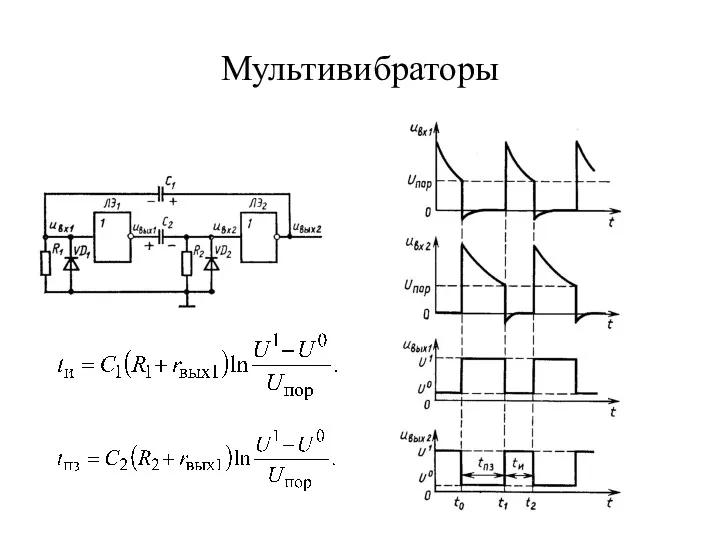

- 64. Мультивибраторы это генераторы периодической последовательности импульсов напряжения прямоугольной формы с требуемыми параметрами (амплитудой, длительностью, частотой следования

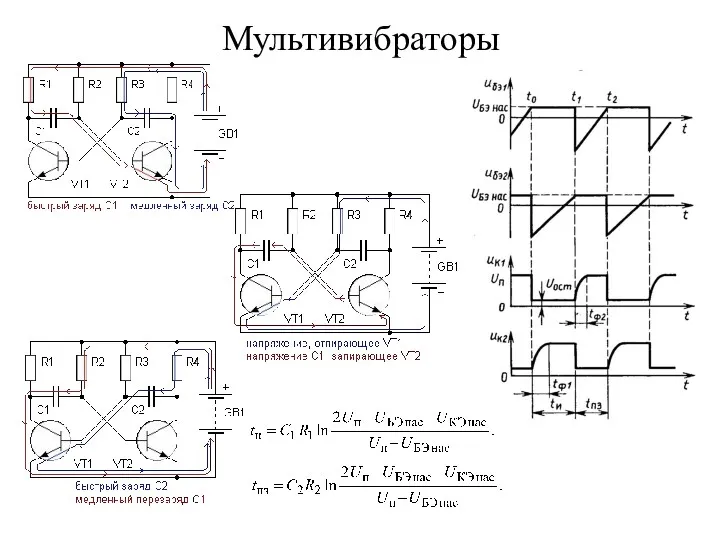

- 65. Мультивибраторы

- 66. Мультивибраторы

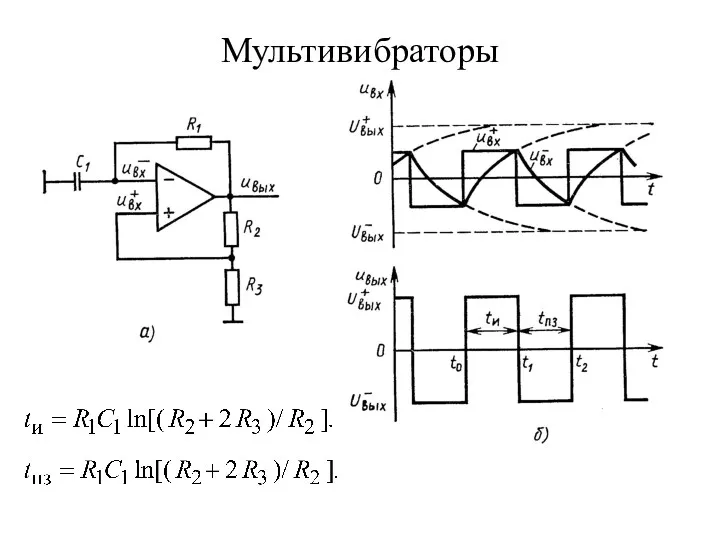

- 67. Мультивибраторы

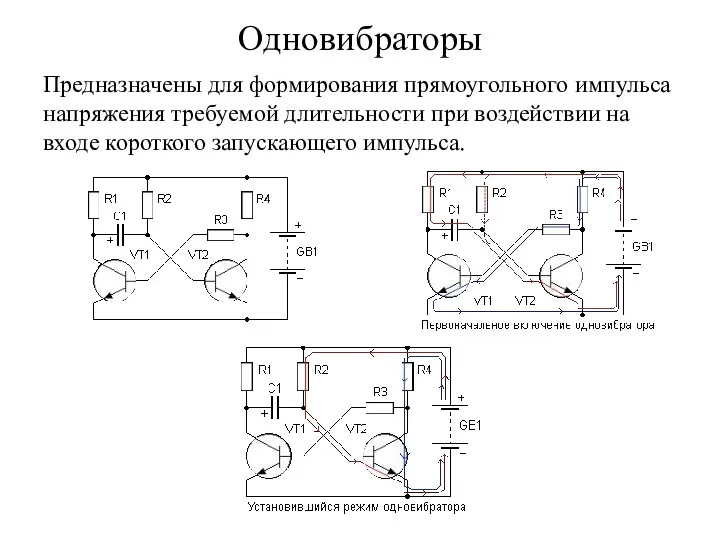

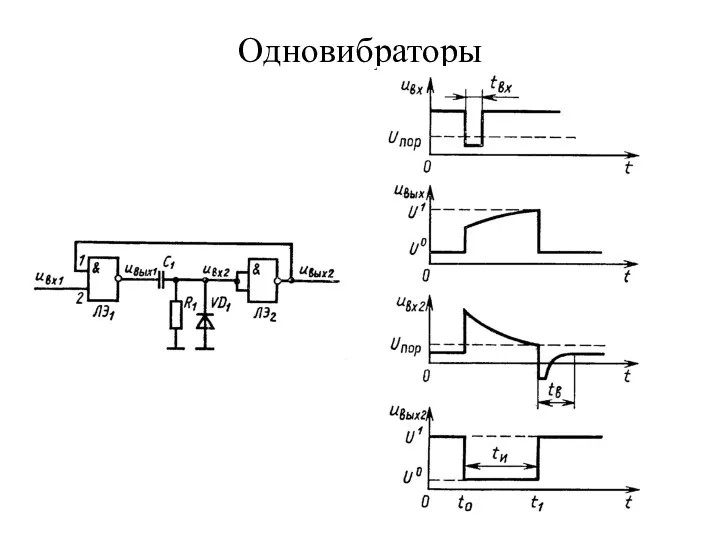

- 68. Одновибраторы Предназначены для формирования прямоугольного импульса напряжения требуемой длительности при воздействии на входе короткого запускающего импульса.

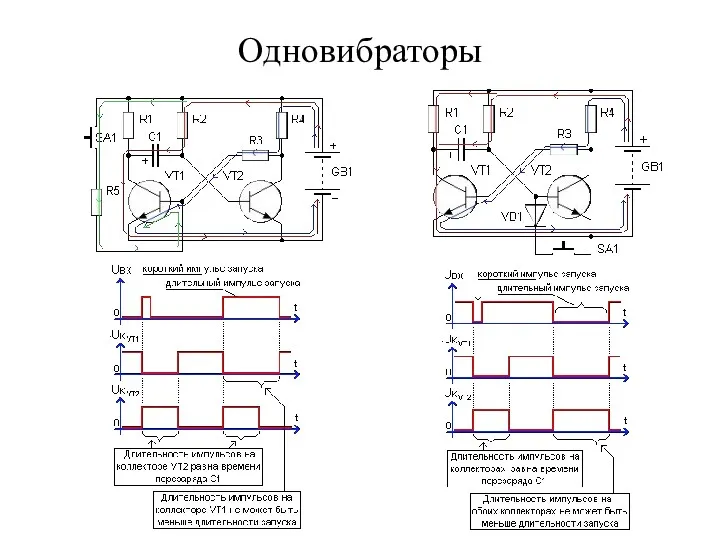

- 69. Одновибраторы

- 70. Одновибраторы

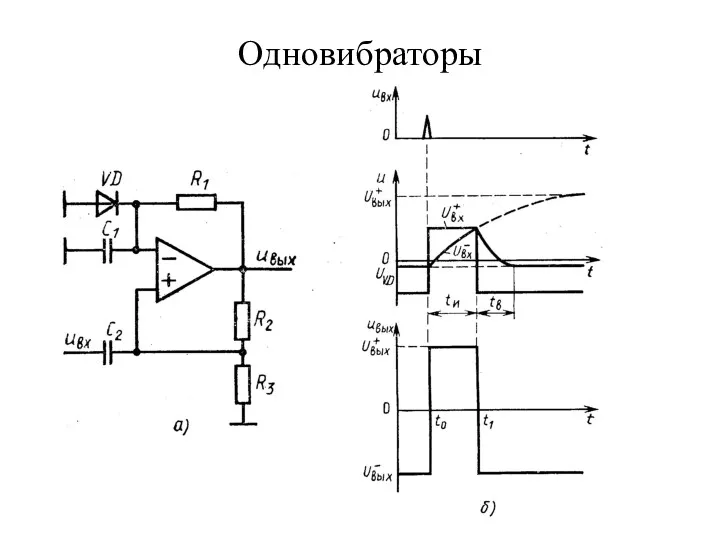

- 71. Одновибраторы

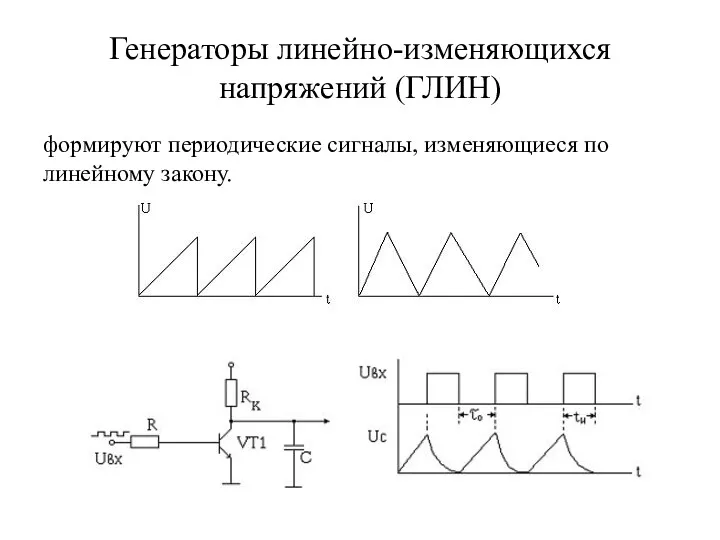

- 72. Генераторы линейно-изменяющихся напряжений (ГЛИН) формируют периодические сигналы, изменяющиеся по линейному закону.

- 74. Скачать презентацию

День народного единства

День народного единства Силы в механике. Виды сил в природе

Силы в механике. Виды сил в природе Вызовы 21-го века. Терроризм

Вызовы 21-го века. Терроризм Творческий проект Семейный калейдоскоп

Творческий проект Семейный калейдоскоп Развитие велопешеходной инфраструктры Петрозаводского городского округа

Развитие велопешеходной инфраструктры Петрозаводского городского округа Особенности проведения лечебно-эвакуационных мероприятий при применении противником отравляющих веществ

Особенности проведения лечебно-эвакуационных мероприятий при применении противником отравляющих веществ Топологические модели электронных схем. Схемы замещения электронных цепей по постоянному и переменному току

Топологические модели электронных схем. Схемы замещения электронных цепей по постоянному и переменному току 4.Презентация к проекту

4.Презентация к проекту Влияние режимов термообработки на свойства сталей

Влияние режимов термообработки на свойства сталей Путешествие по стране Здоровье.

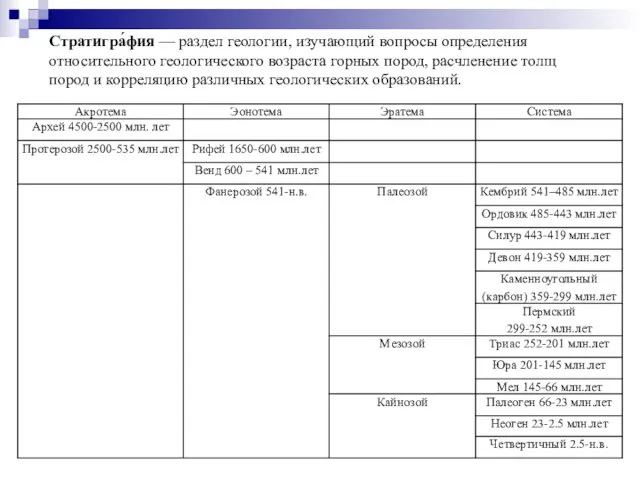

Путешествие по стране Здоровье. Стратигра́фия

Стратигра́фия портфолио

портфолио Гемофилия А, В, С. Классификация по степени тяжести

Гемофилия А, В, С. Классификация по степени тяжести Полупроводниковые диоды. Область применения

Полупроводниковые диоды. Область применения Структура кредитной системы и рынок ссудных капиталов

Структура кредитной системы и рынок ссудных капиталов Итоговый тест по физике

Итоговый тест по физике Теории управления персоналом

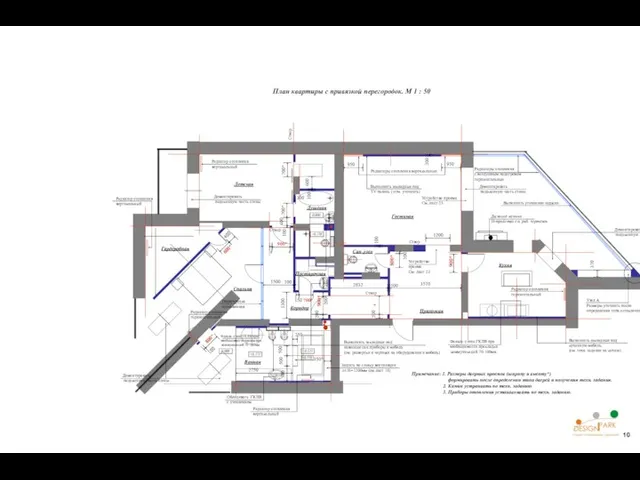

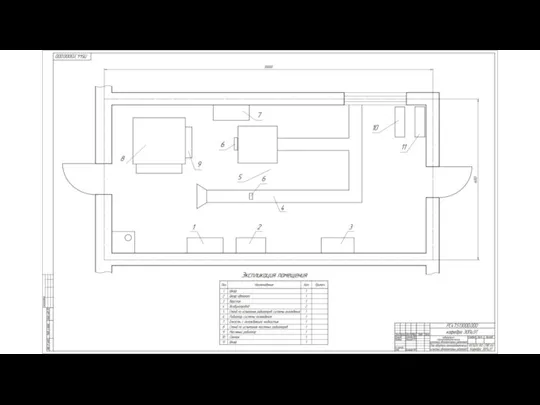

Теории управления персоналом План квартиры с привязкой перегородок

План квартиры с привязкой перегородок Франція. Економіко-географічна характеристика. Історико-культурні особливості

Франція. Економіко-географічна характеристика. Історико-культурні особливості Презентация Загадки от Деда Мороза

Презентация Загадки от Деда Мороза Успешный руководитель

Успешный руководитель Индия - страна чудес. (10 класс)

Индия - страна чудес. (10 класс) Call center operator

Call center operator Экспериментальные исследования в лаборатории теплоаэродинамических испытаний автотракторных радиаторов

Экспериментальные исследования в лаборатории теплоаэродинамических испытаний автотракторных радиаторов Кто в море живет

Кто в море живет Предпринимательская тайна и способы ее защиты. Лекция 8

Предпринимательская тайна и способы ее защиты. Лекция 8 Презентация Синяя лента апреля в МБО УСОШ № 3

Презентация Синяя лента апреля в МБО УСОШ № 3 Физико-химические свойства нефтей и нефтепродуктов

Физико-химические свойства нефтей и нефтепродуктов