Цифровая схемотехника. Энергонезависимая память. Random Access Memory (RAM), Static RAM (SRAM), Dynamic RAM (DRAM) презентация

Содержание

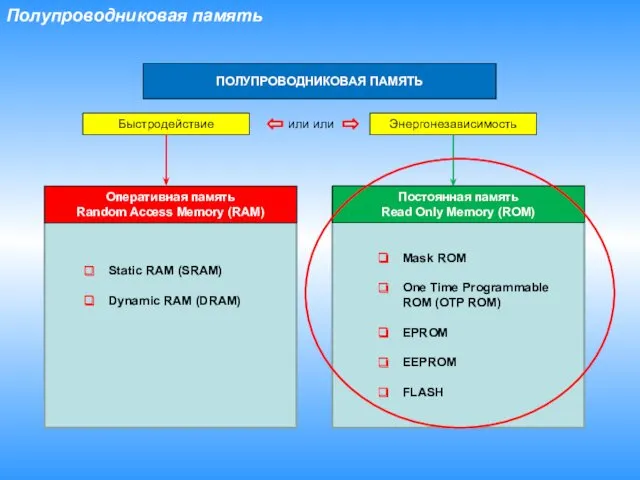

- 2. Полупроводниковая память Быстродействие Энергонезависимость ПОЛУПРОВОДНИКОВАЯ ПАМЯТЬ или или

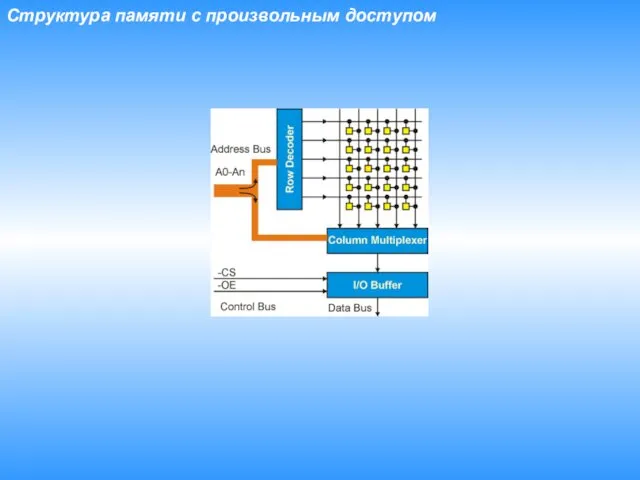

- 3. Структура памяти с произвольным доступом

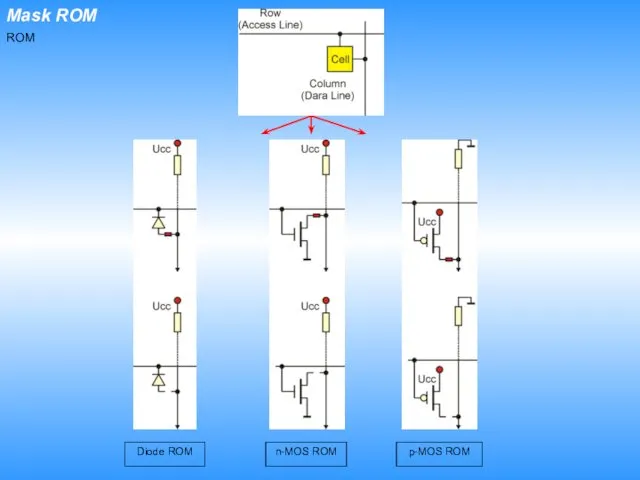

- 4. Mask ROM Diode ROM n-MOS ROM p-MOS ROM ROM

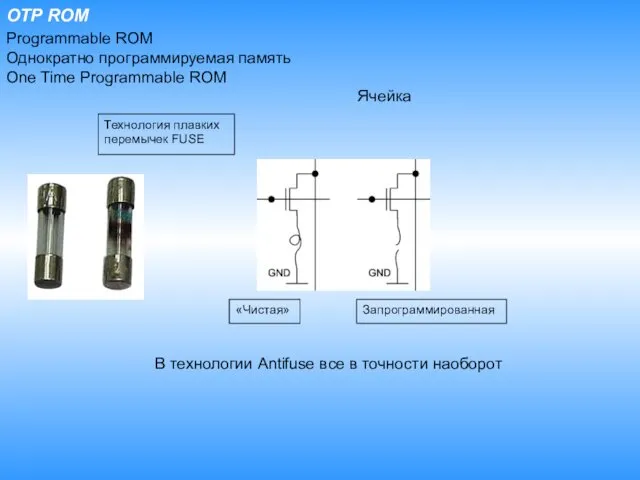

- 5. OTP ROM Programmable ROM Однократно программируемая память One Time Programmable ROM Ячейка «Чистая» Запрограммированная Технология плавких

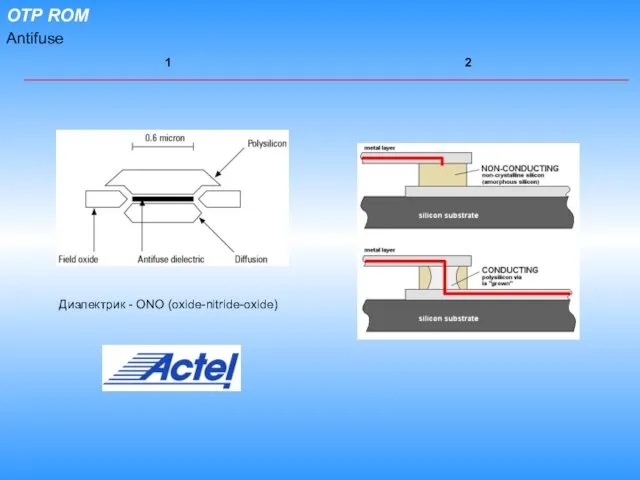

- 6. OTP ROM Antifuse Диэлектрик - ONO (oxide-nitride-oxide) 1 2

- 7. EPROM Erasable Programmable ROM Очень хочется, но как сделать? Полевой транзистор с плавающим затвором

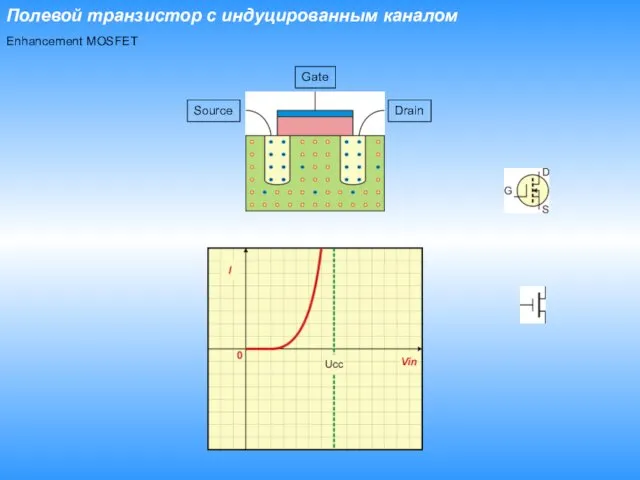

- 8. Полевой транзистор с индуцированным каналом Source Drain Gate Enhancement MOSFET

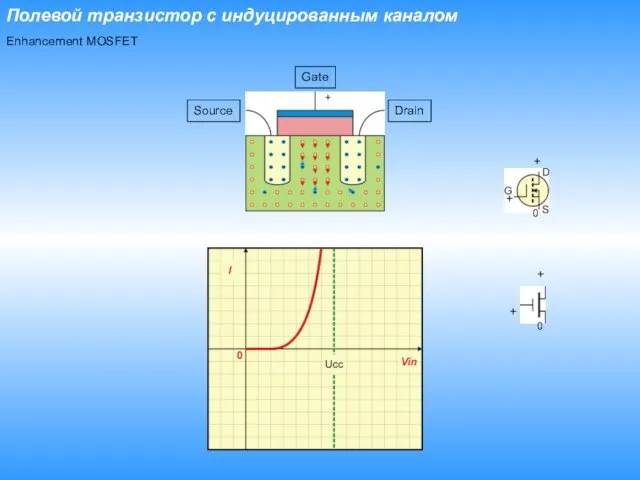

- 9. Полевой транзистор с индуцированным каналом Source Drain Gate Enhancement MOSFET

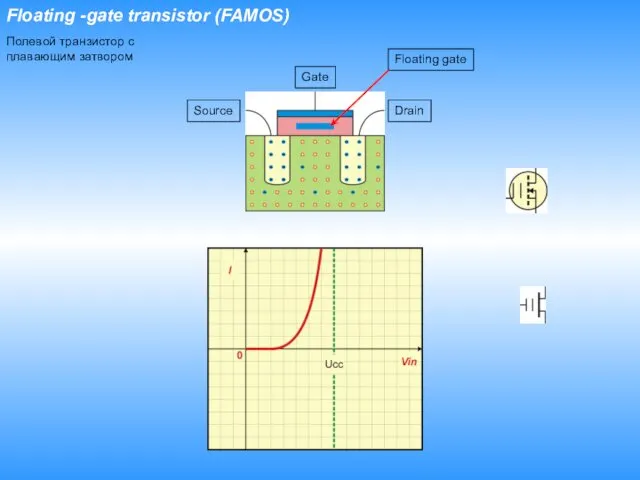

- 10. Floating -gate transistor (FAMOS) Source Drain Gate Полевой транзистор с плавающим затвором Floating gate

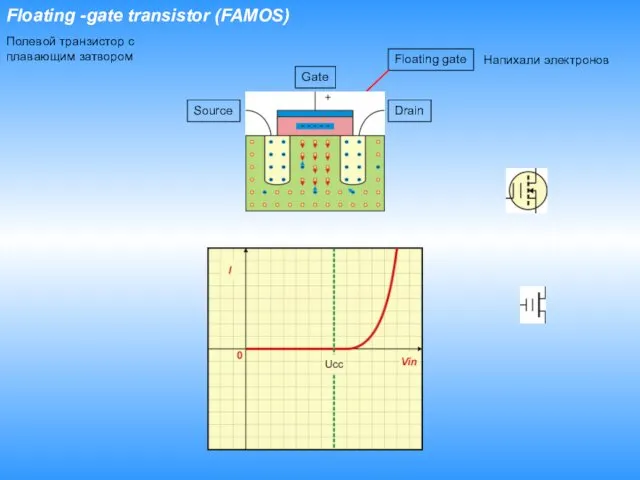

- 11. Floating -gate transistor (FAMOS) Source Drain Gate Полевой транзистор с плавающим затвором Floating gate Напихали электронов

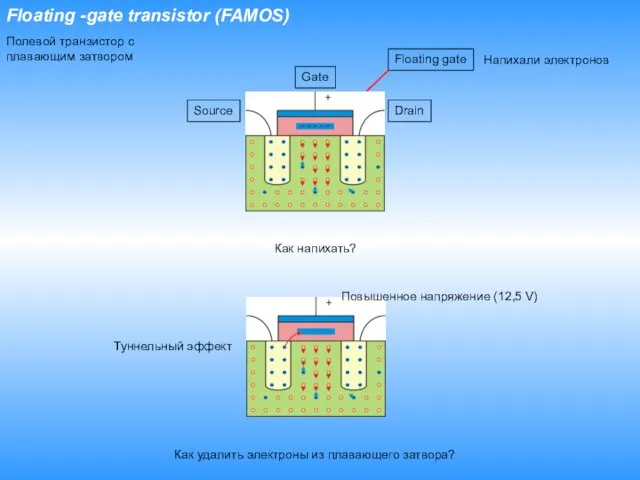

- 12. Floating -gate transistor (FAMOS) Source Drain Gate Полевой транзистор с плавающим затвором Floating gate Напихали электронов

- 13. EPROM 1971 Frohman’s UV-erasable EPROM UV Eerasable EPROM

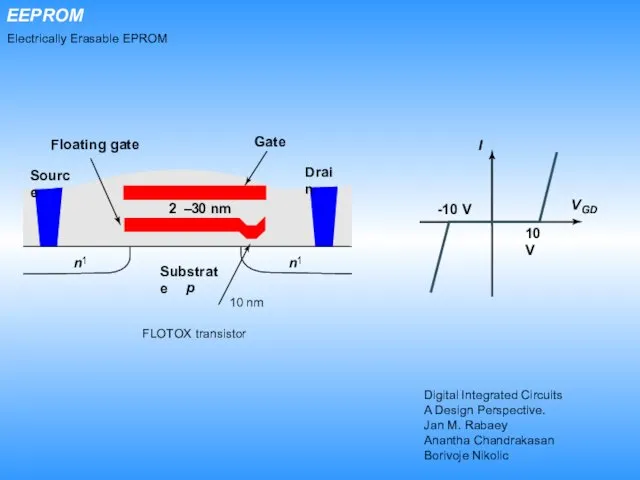

- 14. EEPROM Floating gate Source Substrate p Gate Drain n 1 n 1 20 – 30 nm

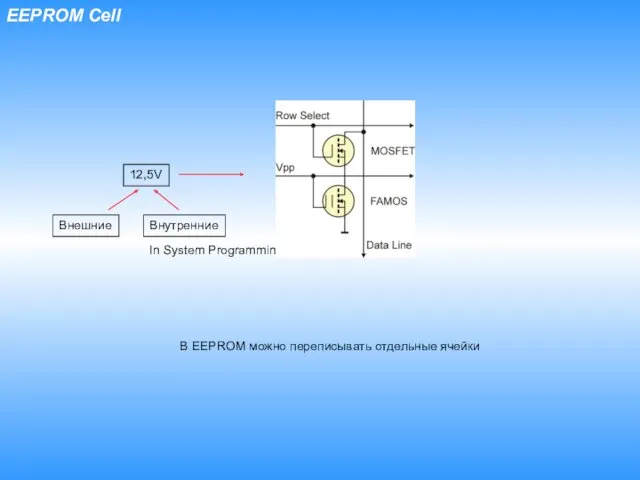

- 15. EEPROM Cell 12,5V Внешние Внутренние В EEPROM можно переписывать отдельные ячейки In System Programming

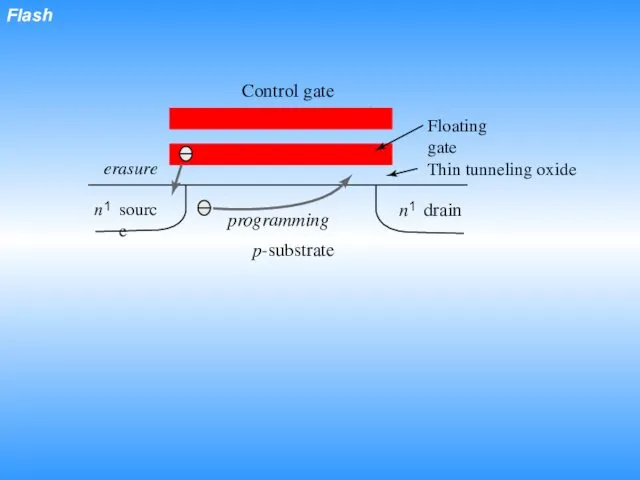

- 16. Flash

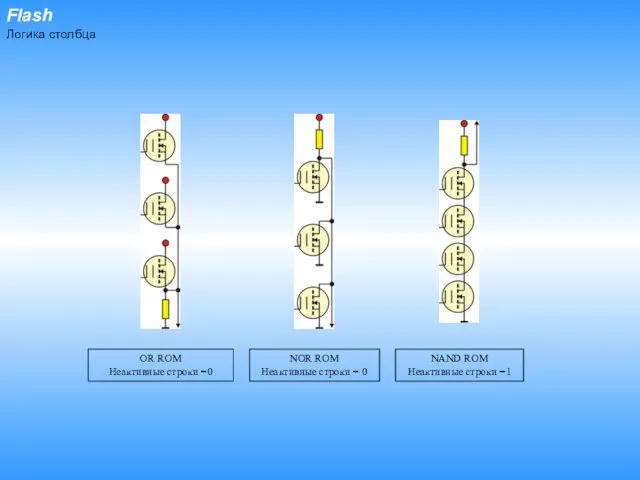

- 17. Flash OR ROM Неактивные строки =0 NOR ROM Неактивные строки = 0 NAND ROM Неактивные строки

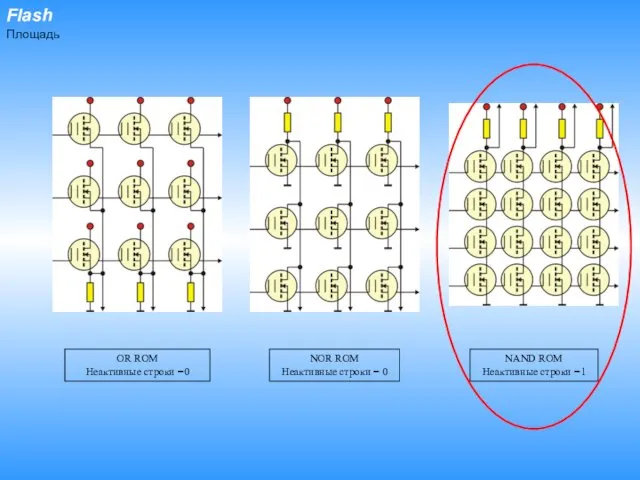

- 18. Flash OR ROM Неактивные строки =0 NOR ROM Неактивные строки = 0 NAND ROM Неактивные строки

- 20. Скачать презентацию

Монтаж комплектных трансформаторных подстанций

Монтаж комплектных трансформаторных подстанций Теплом своих рук школу озеленим вокруг!

Теплом своих рук школу озеленим вокруг! Презентация к сказке Снежная королева

Презентация к сказке Снежная королева СССР в 1970-1985 годах

СССР в 1970-1985 годах Эти удивительные металлы

Эти удивительные металлы Элементы дискурс анализа для обучения чтению при подготовке к международным экзаменам по английскому языку

Элементы дискурс анализа для обучения чтению при подготовке к международным экзаменам по английскому языку Виды спорта

Виды спорта CASE-технологии

CASE-технологии Подготовка к математическому тестированию Кенгуру-выпускникам Часть 1

Подготовка к математическому тестированию Кенгуру-выпускникам Часть 1 Квилинг

Квилинг Сочинение по картине Исаака Левитана Весна. Большая вода

Сочинение по картине Исаака Левитана Весна. Большая вода Микропроцессорная система сбора и распределения информации SAU 8800 (Signal Acquisition Units)

Микропроцессорная система сбора и распределения информации SAU 8800 (Signal Acquisition Units) Психические процессы. Структура психики

Психические процессы. Структура психики Классный часБереги здоровье смолоду

Классный часБереги здоровье смолоду Череп человека. Развитие, общая форма, изменчивость

Череп человека. Развитие, общая форма, изменчивость Через знания к звездам. Школьная газета

Через знания к звездам. Школьная газета Электрооборудование пассажирских вагонов в поездах

Электрооборудование пассажирских вагонов в поездах Технология выполнения высококачественной штукатурки

Технология выполнения высококачественной штукатурки Конкурс Самый классный классный

Конкурс Самый классный классный Рельеф Земли. Равнины

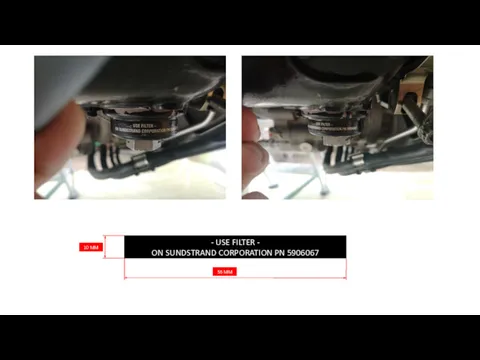

Рельеф Земли. Равнины Use filter on sundstrand corporation pn 5906067 55 mm

Use filter on sundstrand corporation pn 5906067 55 mm Автоматический радиокомпас АРК-15

Автоматический радиокомпас АРК-15 Процесс завершения проекта и мониторинг выгод. (Модуль 6)

Процесс завершения проекта и мониторинг выгод. (Модуль 6) Презентация Новогодние поделки

Презентация Новогодние поделки Курсовая работа здание спортивного комплекса

Курсовая работа здание спортивного комплекса Народная кукла-оберег. Травница.

Народная кукла-оберег. Травница. Путешествие в город Смехоград

Путешествие в город Смехоград Натюрморт

Натюрморт