Слайд 2

2013

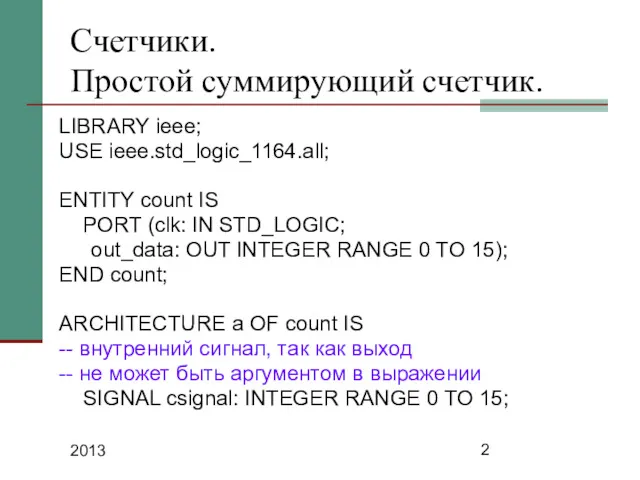

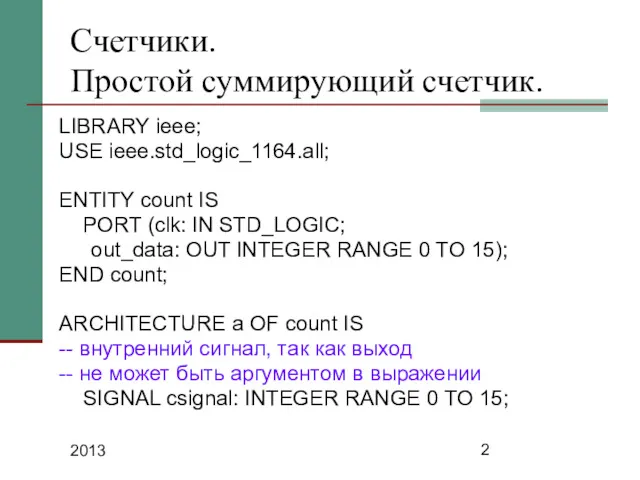

Счетчики.

Простой суммирующий счетчик.

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY count IS

PORT (clk: IN STD_LOGIC;

out_data: OUT INTEGER

RANGE 0 TO 15);

END count;

ARCHITECTURE a OF count IS

-- внутренний сигнал, так как выход

-- не может быть аргументом в выражении

SIGNAL csignal: INTEGER RANGE 0 TO 15;

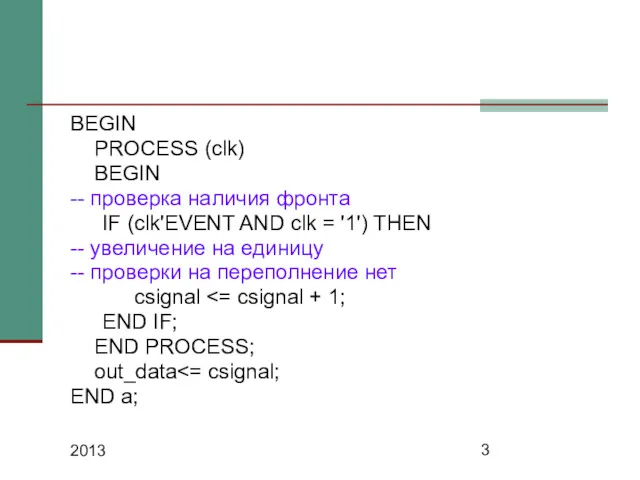

Слайд 3

2013

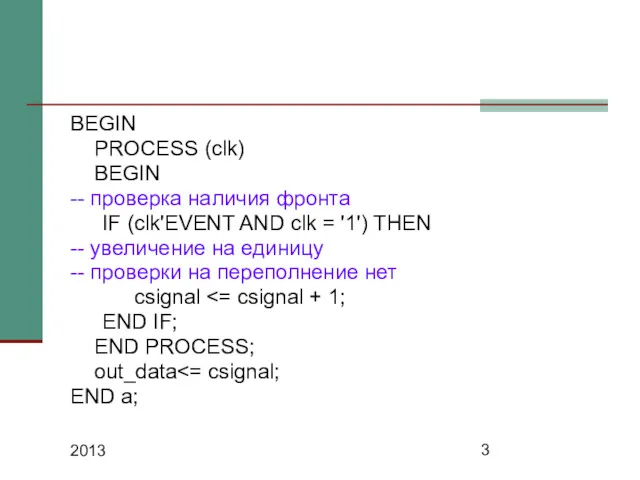

BEGIN

PROCESS (clk)

BEGIN

-- проверка наличия фронта

IF (clk'EVENT AND clk = '1') THEN

--

увеличение на единицу

-- проверки на переполнение нет

csignal <= csignal + 1;

END IF;

END PROCESS;

out_data<= csignal;

END a;

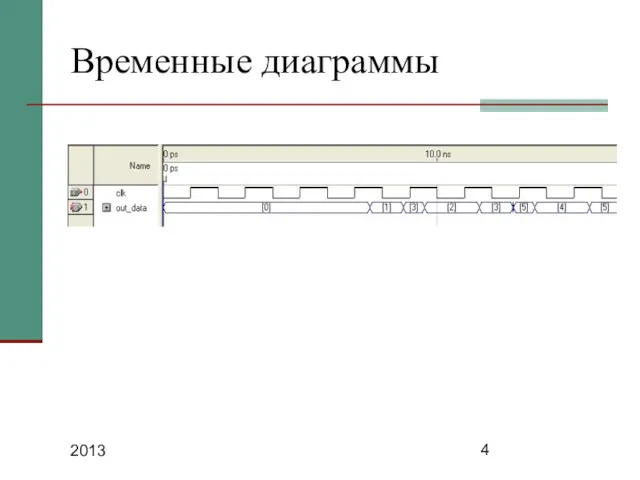

Слайд 4

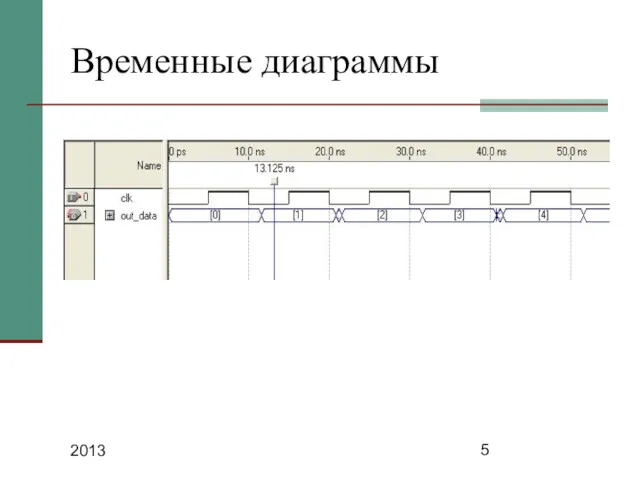

Слайд 5

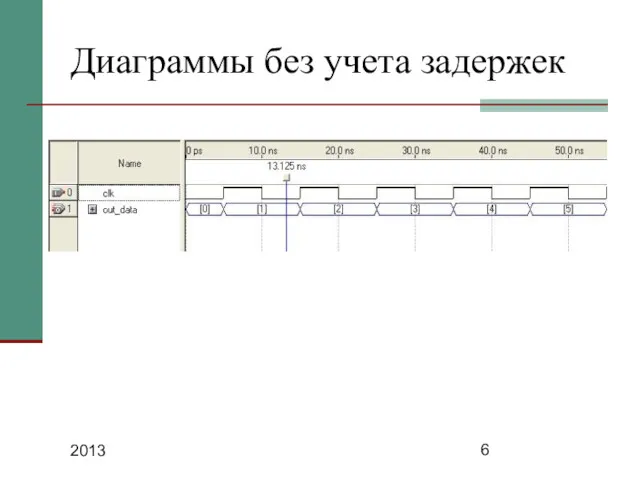

Слайд 6

2013

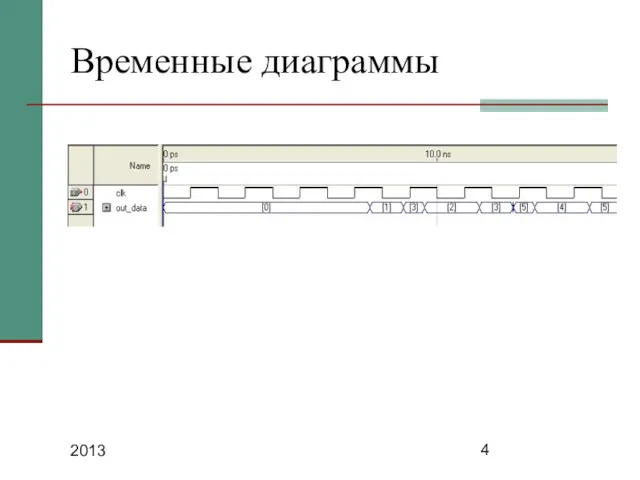

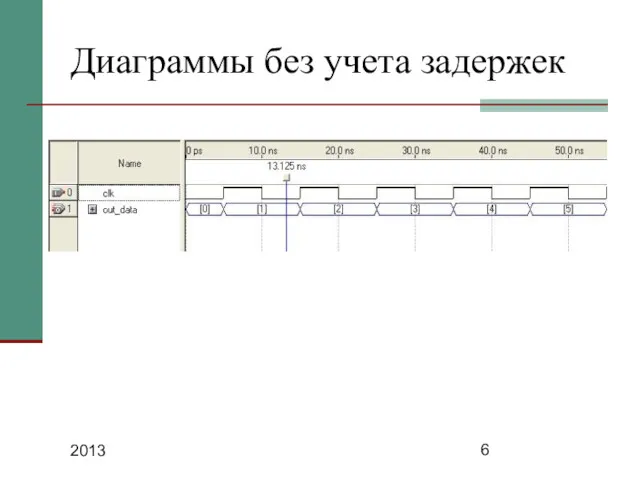

Диаграммы без учета задержек

Слайд 7

2013

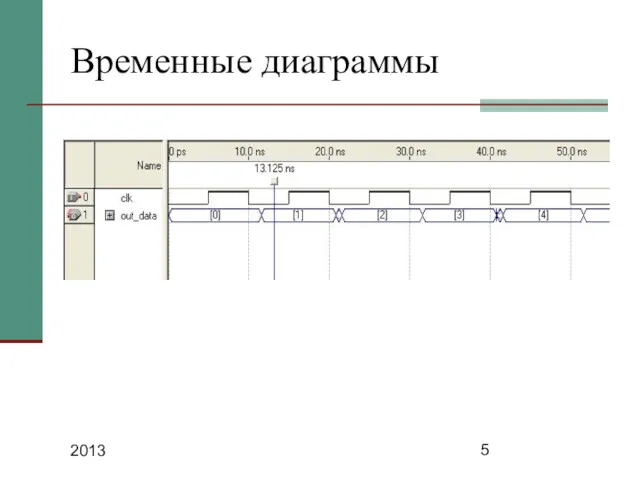

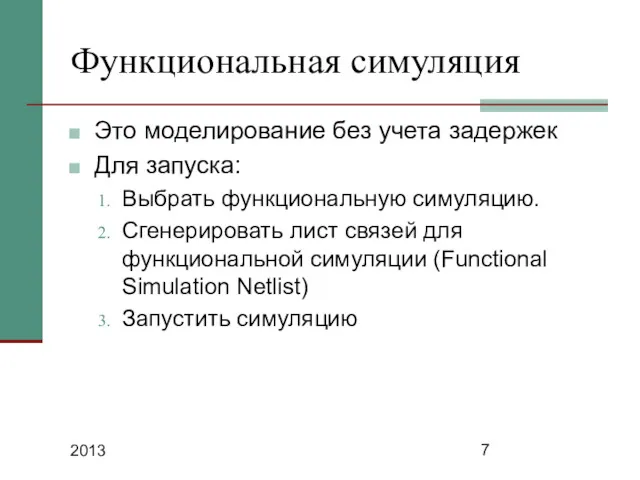

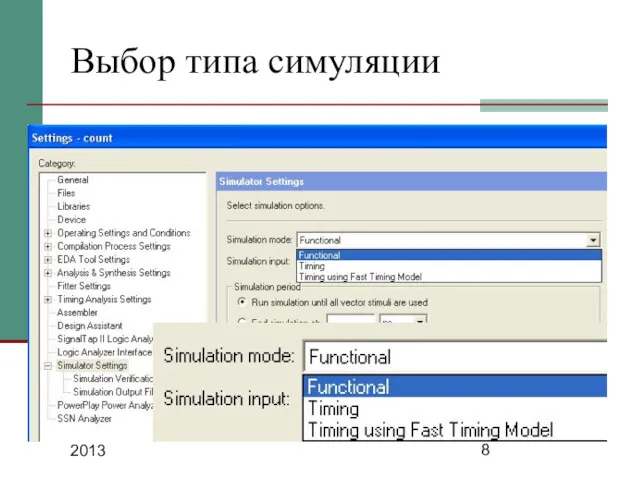

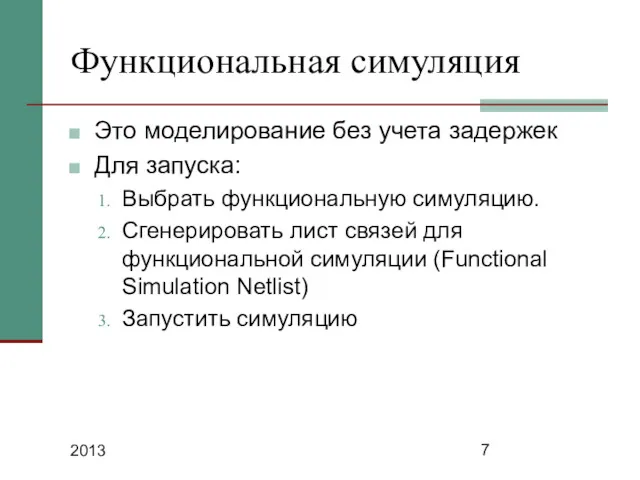

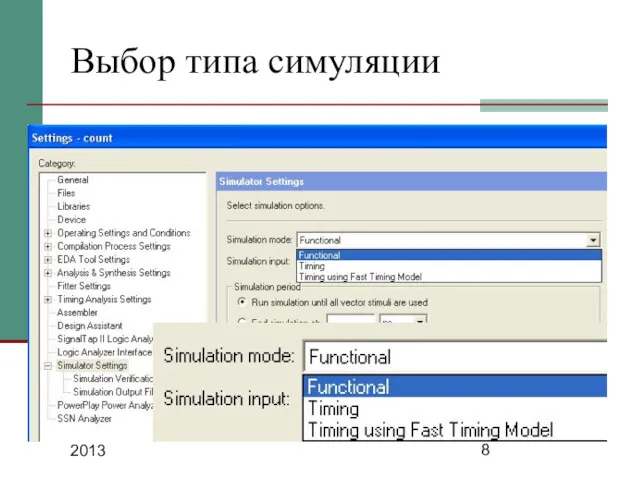

Функциональная симуляция

Это моделирование без учета задержек

Для запуска:

Выбрать функциональную симуляцию.

Сгенерировать лист связей

для функциональной симуляции (Functional Simulation Netlist)

Запустить симуляцию

Слайд 8

Слайд 9

2013

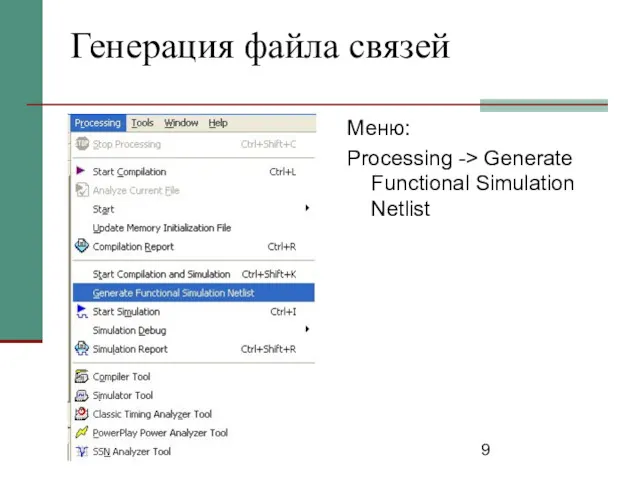

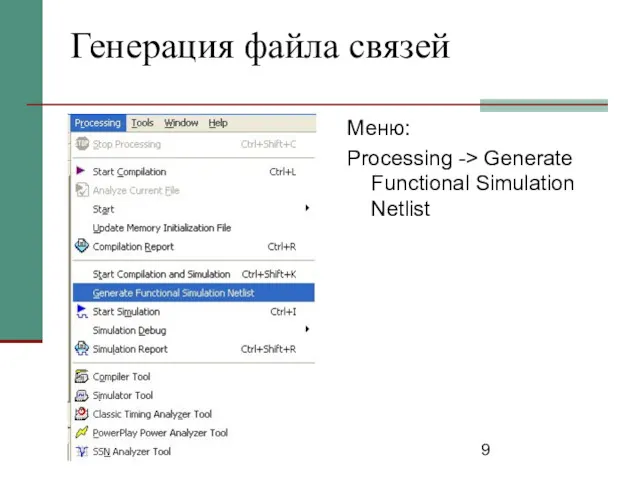

Генерация файла связей

Меню:

Processing -> Generate Functional Simulation Netlist

Слайд 10

2013

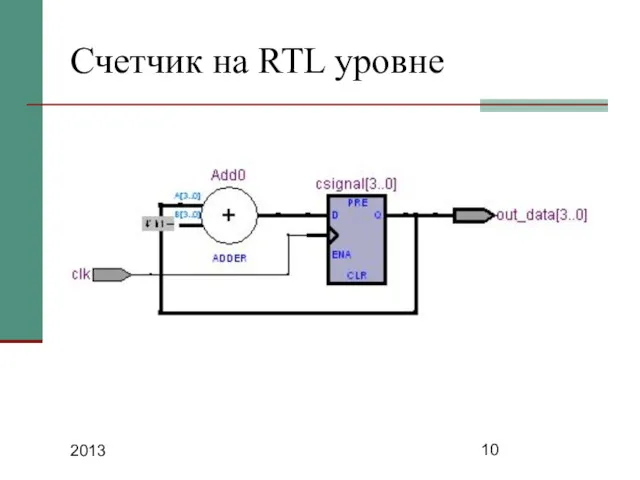

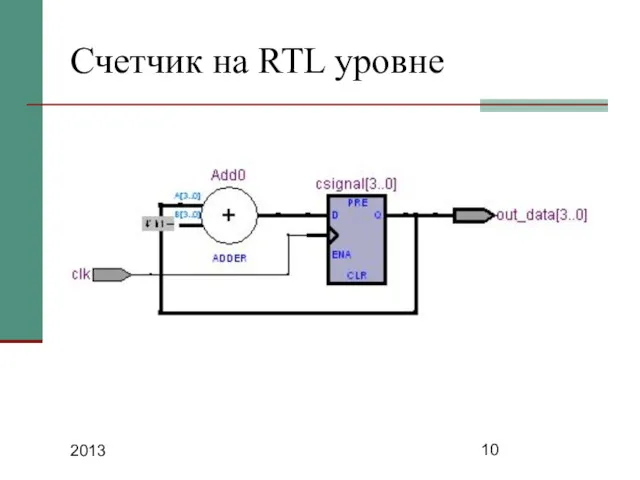

Счетчик на RTL уровне

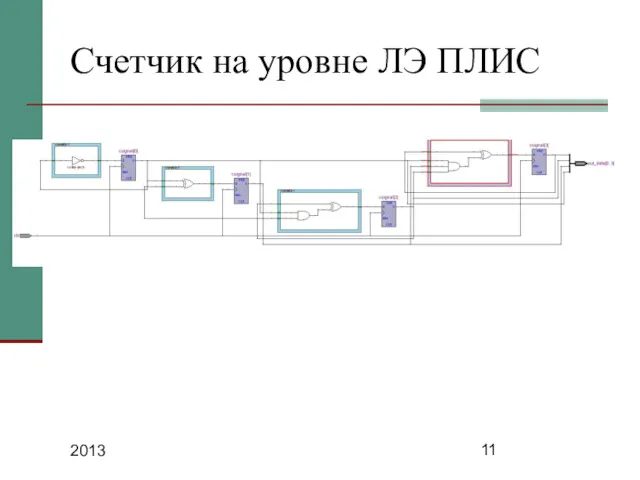

Слайд 11

2013

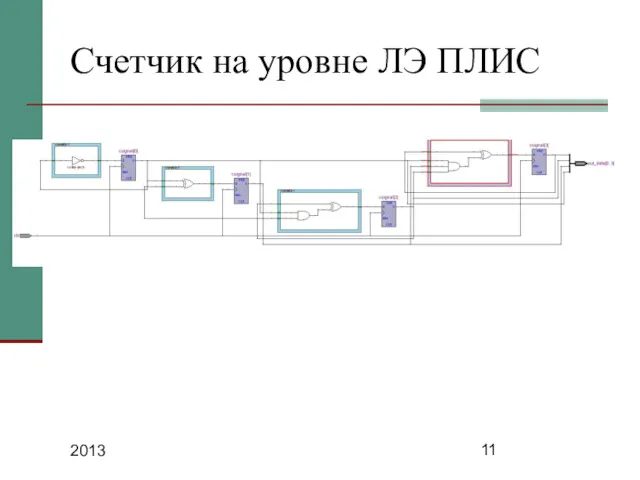

Счетчик на уровне ЛЭ ПЛИС

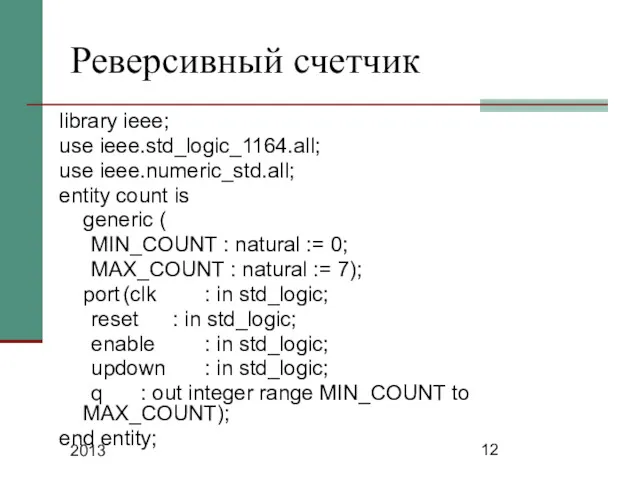

Слайд 12

2013

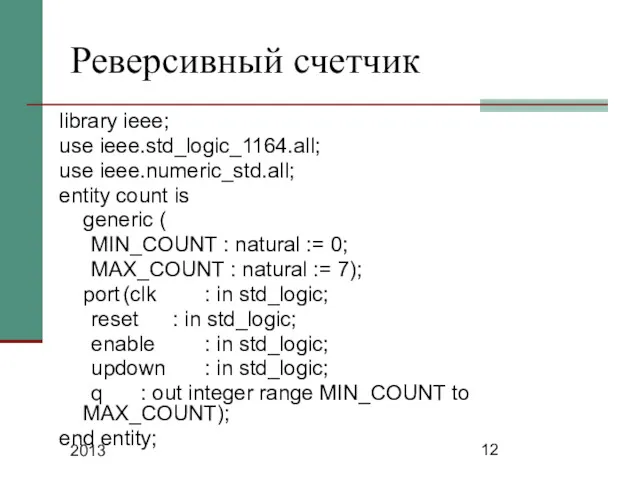

Реверсивный счетчик

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity count is

generic (

MIN_COUNT : natural :=

0;

MAX_COUNT : natural := 7);

port (clk : in std_logic;

reset : in std_logic;

enable : in std_logic;

updown : in std_logic;

q : out integer range MIN_COUNT to MAX_COUNT);

end entity;

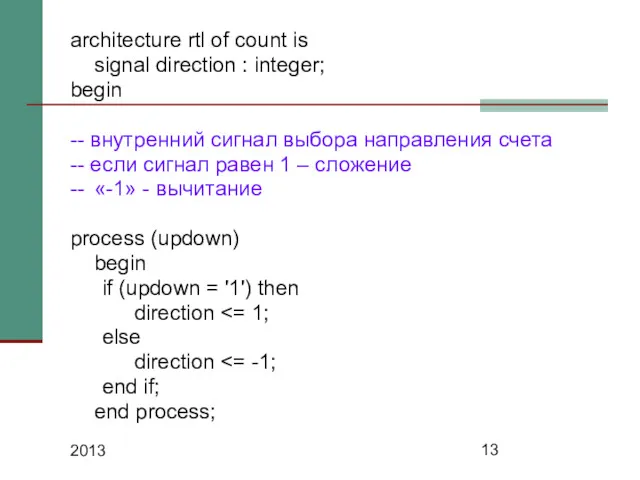

Слайд 13

2013

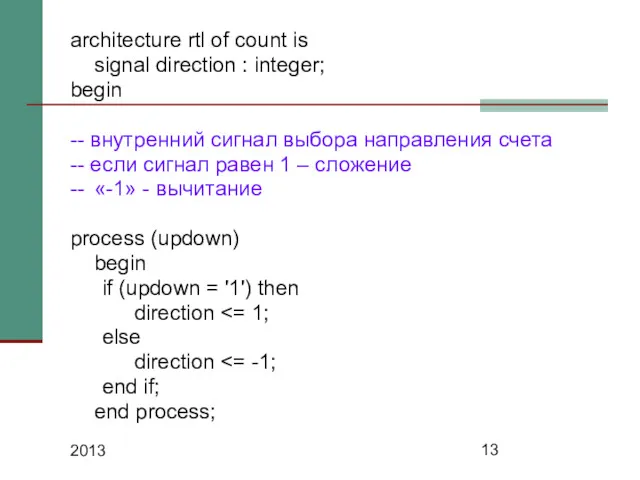

architecture rtl of count is

signal direction : integer;

begin

-- внутренний сигнал выбора

направления счета

-- если сигнал равен 1 – сложение

-- «-1» - вычитание

process (updown)

begin

if (updown = '1') then

direction <= 1;

else

direction <= -1;

end if;

end process;

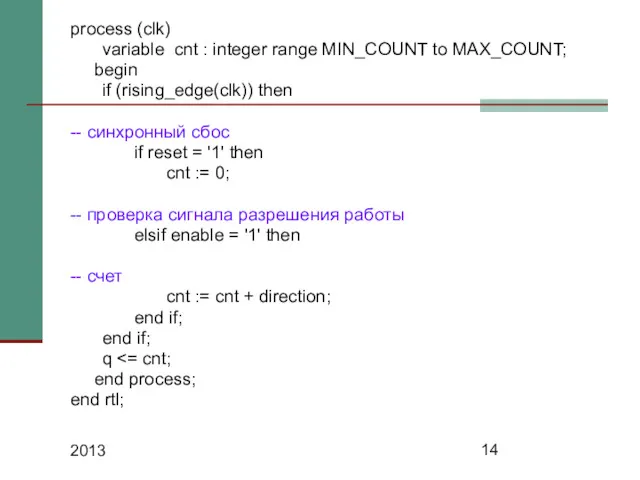

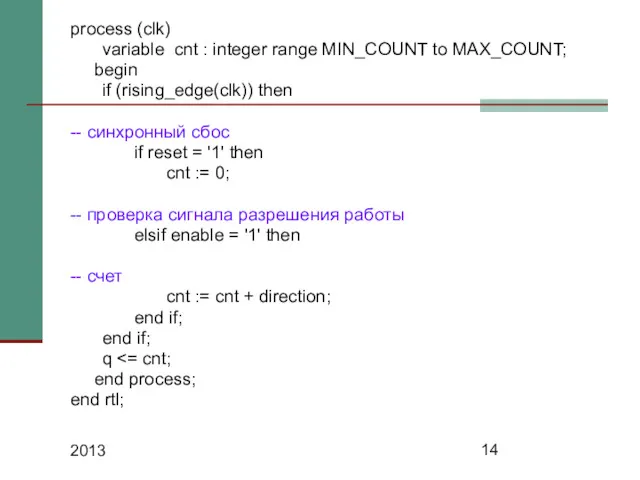

Слайд 14

2013

process (clk)

variable cnt : integer range MIN_COUNT to MAX_COUNT;

begin

if (rising_edge(clk)) then

--

синхронный сбос

if reset = '1' then

cnt := 0;

-- проверка сигнала разрешения работы

elsif enable = '1' then

-- счет

cnt := cnt + direction;

end if;

end if;

q <= cnt;

end process;

end rtl;

Слайд 15

2013

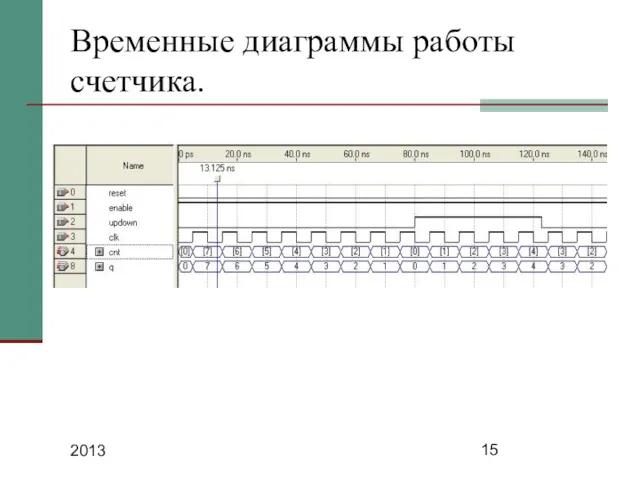

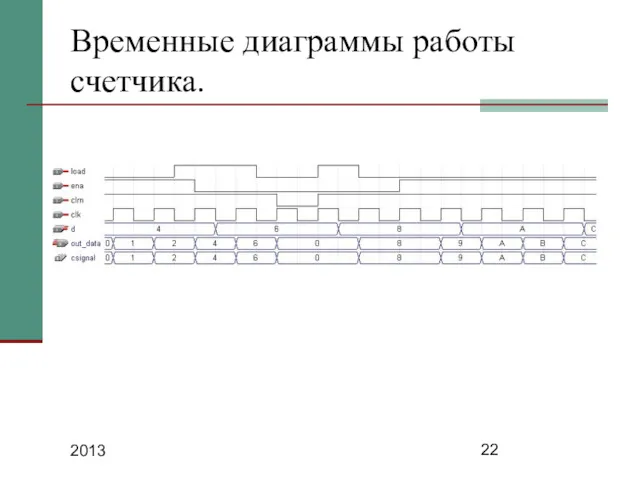

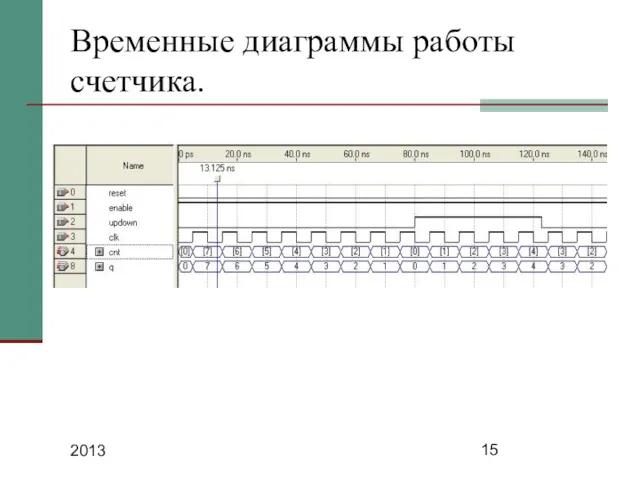

Временные диаграммы работы счетчика.

Слайд 16

2013

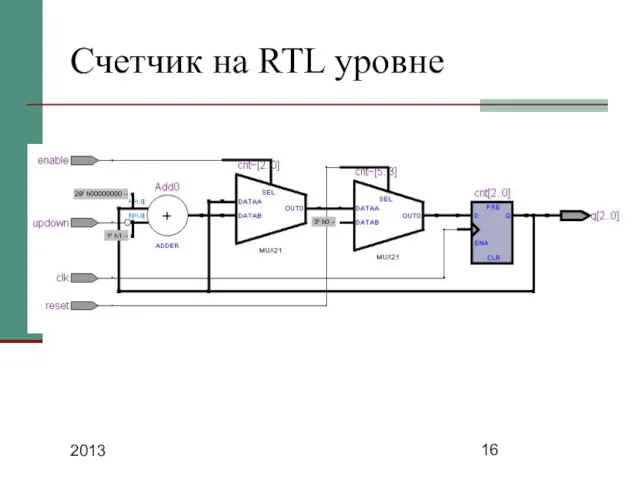

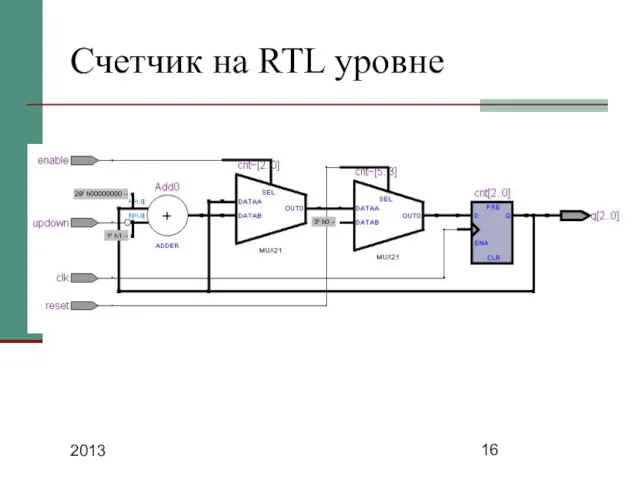

Счетчик на RTL уровне

Слайд 17

2013

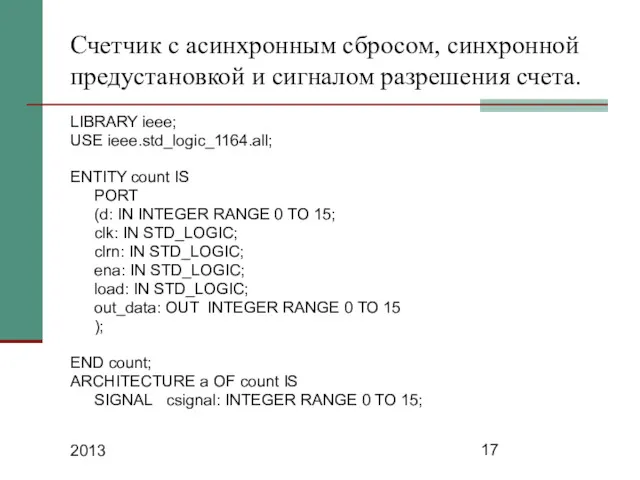

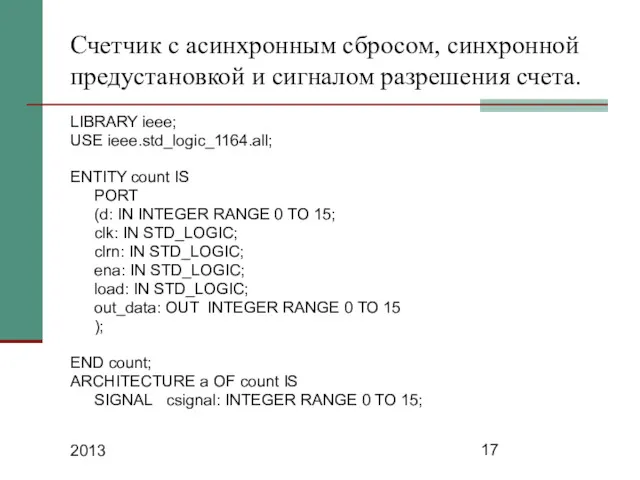

Счетчик с асинхронным сбросом, синхронной предустановкой и сигналом разрешения счета.

LIBRARY ieee;

USE

ieee.std_logic_1164.all;

ENTITY count IS

PORT

(d: IN INTEGER RANGE 0 TO 15;

clk: IN STD_LOGIC;

clrn: IN STD_LOGIC;

ena: IN STD_LOGIC;

load: IN STD_LOGIC;

out_data: OUT INTEGER RANGE 0 TO 15

);

END count;

ARCHITECTURE a OF count IS

SIGNAL csignal: INTEGER RANGE 0 TO 15;

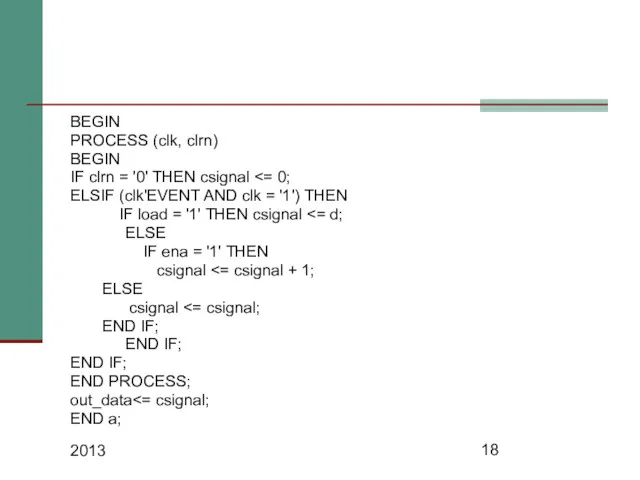

Слайд 18

2013

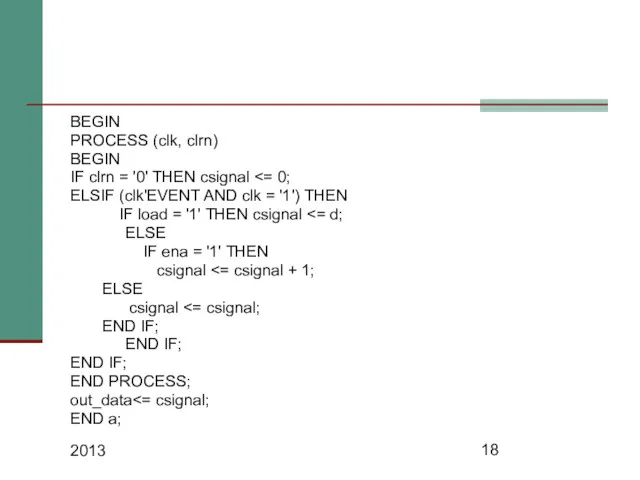

BEGIN

PROCESS (clk, clrn)

BEGIN

IF clrn = '0' THEN csignal <= 0;

ELSIF (clk'EVENT

AND clk = '1') THEN

IF load = '1' THEN csignal <= d;

ELSE

IF ena = '1' THEN

csignal <= csignal + 1;

ELSE

csignal <= csignal;

END IF;

END IF;

END IF;

END PROCESS;

out_data<= csignal;

END a;

Слайд 19

2013

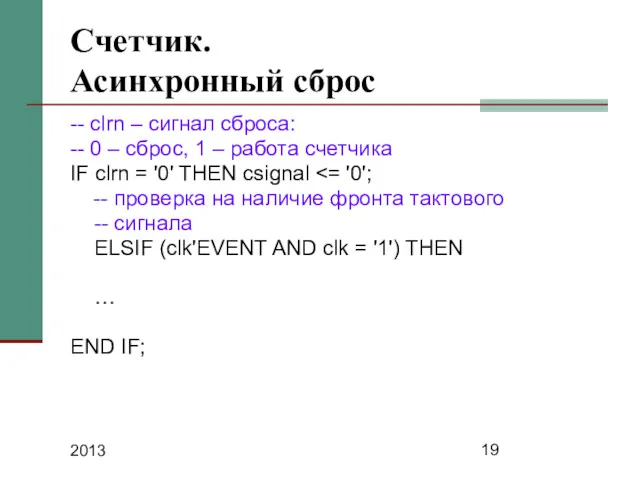

Счетчик.

Асинхронный сброс

-- clrn – сигнал сброса:

-- 0 – сброс,

1 – работа счетчика

IF clrn = '0' THEN csignal <= '0';

-- проверка на наличие фронта тактового

-- сигнала

ELSIF (clk'EVENT AND clk = '1') THEN

…

END IF;

Слайд 20

2013

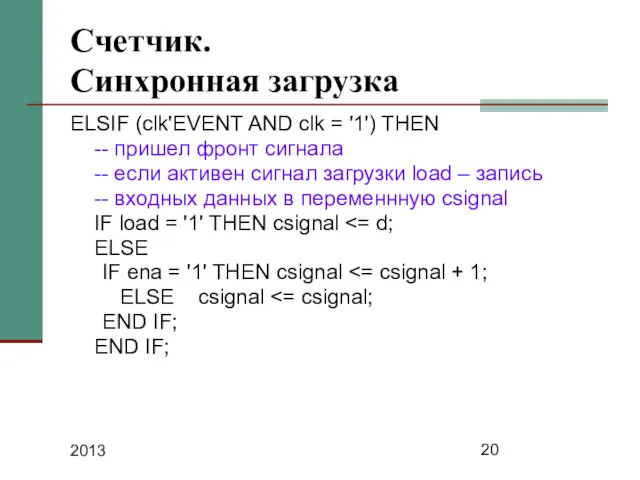

Счетчик.

Синхронная загрузка

ELSIF (clk'EVENT AND clk = '1') THEN

-- пришел фронт

сигнала

-- если активен сигнал загрузки load – запись

-- входных данных в переменнную csignal

IF load = '1' THEN csignal <= d;

ELSE

IF ena = '1' THEN csignal <= csignal + 1;

ELSE csignal <= csignal;

END IF;

END IF;

Слайд 21

2013

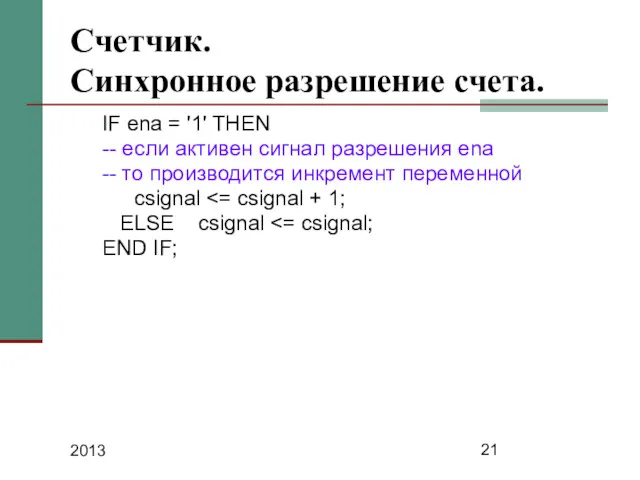

Счетчик.

Синхронное разрешение счета.

IF ena = '1' THEN

-- если активен сигнал

разрешения ena

-- то производится инкремент переменной

csignal <= csignal + 1;

ELSE csignal <= csignal;

END IF;

Слайд 22

2013

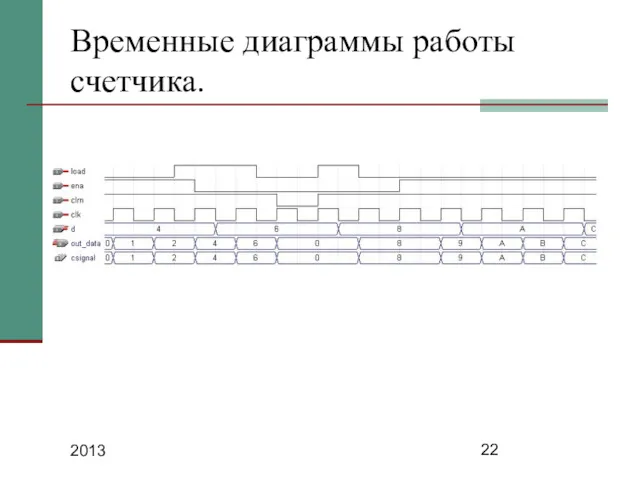

Временные диаграммы работы счетчика.

Слайд 23

2013

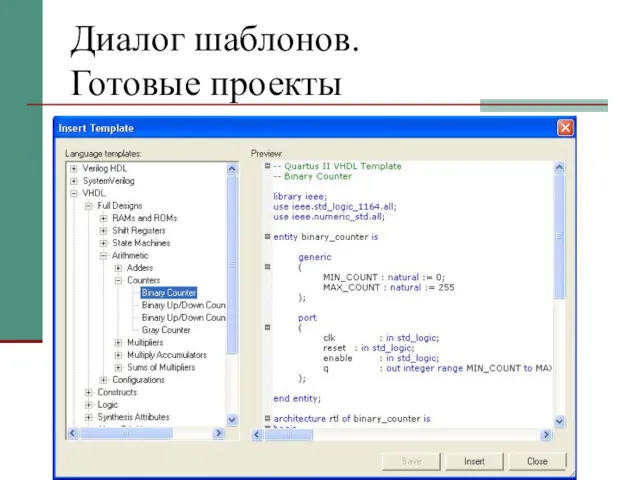

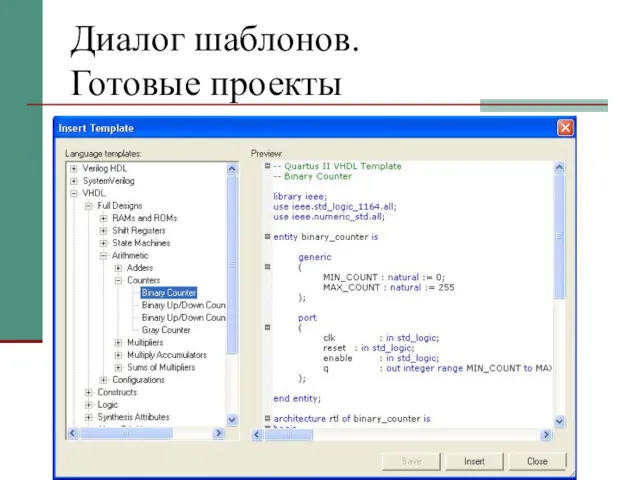

Диалог шаблонов.

Готовые проекты

Слайд 24

2013

Дополнительная литература

Quartus II Handbook. Vol. 1. Part 6. Recommended HDL Coding

Styles.

Xilinx HDL Coding Techniques. http://www.xilinx.com/itp/3_1i/data/fise/xst/chap02/xst02000.htm

Презентация о дружбе

Презентация о дружбе Игра - викторина Путешествие в историю вещей. Презентация.

Игра - викторина Путешествие в историю вещей. Презентация. Буква М

Буква М Рельеф Приморского края. Интерактивный тест

Рельеф Приморского края. Интерактивный тест Транспорт мира

Транспорт мира Проект Давайте жить дружно!

Проект Давайте жить дружно! Архимед

Архимед Энергосберегающие технологии домостроения

Энергосберегающие технологии домостроения Учим стихи.

Учим стихи. Стратегия продвижения в социальных сетях на примере ПРК ЭПЛ

Стратегия продвижения в социальных сетях на примере ПРК ЭПЛ Презентация к празднику Незнайка в гостях у ребят

Презентация к празднику Незнайка в гостях у ребят Обработка нижних срезов рукавов

Обработка нижних срезов рукавов Сухие строительные смеси. Общие понятия, проблемы и решения

Сухие строительные смеси. Общие понятия, проблемы и решения Дифференциальная диагностика и лечение кишечной диспепсии. (2)

Дифференциальная диагностика и лечение кишечной диспепсии. (2) Твёрдые и мягкие согласные звуки

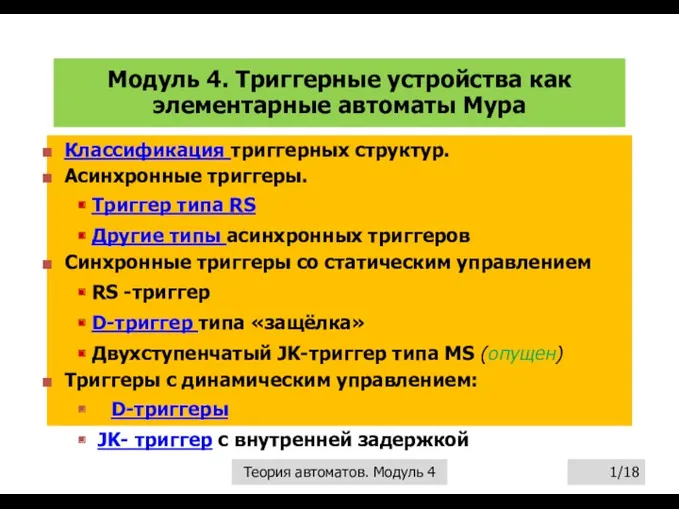

Твёрдые и мягкие согласные звуки Триггерные устройства как элементарные автоматы Мура

Триггерные устройства как элементарные автоматы Мура Изобретения, предсказанные в научной фантастике

Изобретения, предсказанные в научной фантастике Презентация - краеведческая викторина _Земля Ульяновская_

Презентация - краеведческая викторина _Земля Ульяновская_ Гидравлика. Гидростатика. Гидродинамика. Примеры расчета

Гидравлика. Гидростатика. Гидродинамика. Примеры расчета Индексы. Индексируемая величина

Индексы. Индексируемая величина Рослинні тканини

Рослинні тканини Памятка пользователя сервиса “Электронная регистрация”

Памятка пользователя сервиса “Электронная регистрация” Презентация История дзержинского аэроклуба им. Н.П.Каманина.

Презентация История дзержинского аэроклуба им. Н.П.Каманина. Інженерно-геологічні вишукування. Основні положення

Інженерно-геологічні вишукування. Основні положення Аксиологические и технологические компоненты организационно педагогической культуры, как фактор развития профессионализма педагога

Аксиологические и технологические компоненты организационно педагогической культуры, как фактор развития профессионализма педагога Влажно тепловая обработка ткани

Влажно тепловая обработка ткани Ознакомление с информацией об оказываемых услугах

Ознакомление с информацией об оказываемых услугах Производимая продукция. Технология производства. Основные виды оборудования

Производимая продукция. Технология производства. Основные виды оборудования