Содержание

- 2. Управление памятью Иерархия памяти Регистры Кэш Оперативная память Вторичная память Стоимость одного бита Время доступа Объем

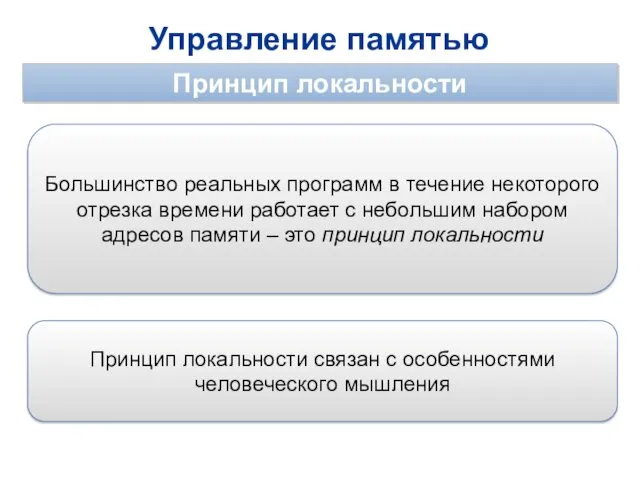

- 3. Принцип локальности связан с особенностями человеческого мышления Большинство реальных программ в течение некоторого отрезка времени работает

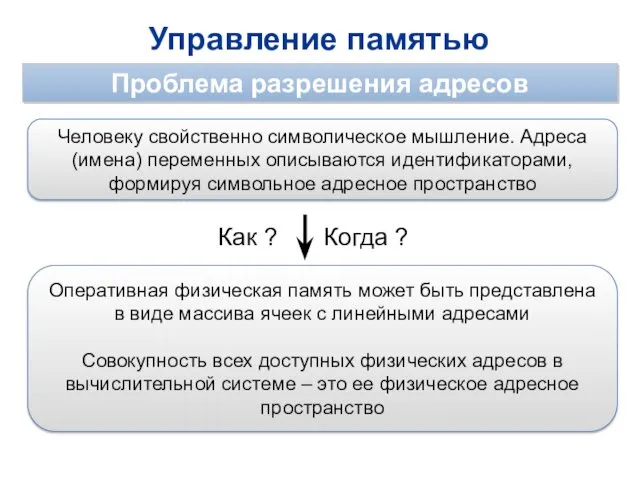

- 4. Оперативная физическая память может быть представлена в виде массива ячеек с линейными адресами Совокупность всех доступных

- 5. Управление памятью Связывание адресов Исходная программа Компилятор Объектный модуль Другие объектные модули Редактор связей Загрузочный модуль

- 6. Физическое адресное пространство – совокупность всех доступных физических адресов в вычислительной системе Символьное адресное пространство –

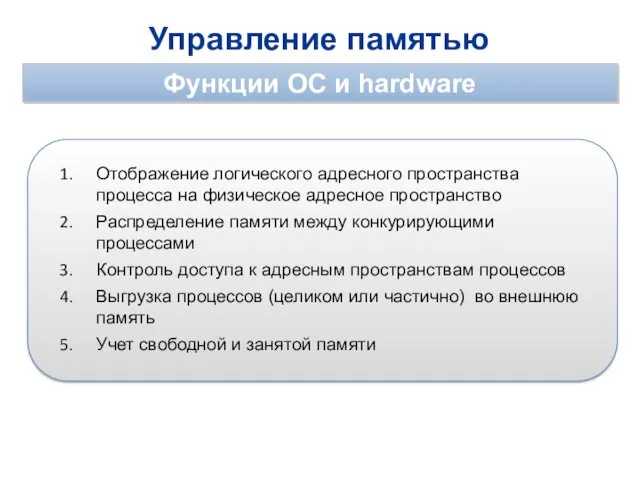

- 7. Управление памятью Функции ОС и hardware Отображение логического адресного пространства процесса на физическое адресное пространство Распределение

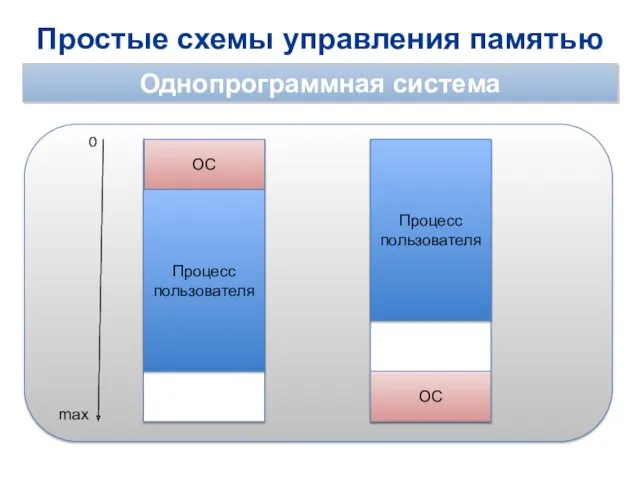

- 8. Простые схемы управления памятью Однопрограммная система 0 ОС max ОС Процесс пользователя Процесс пользователя

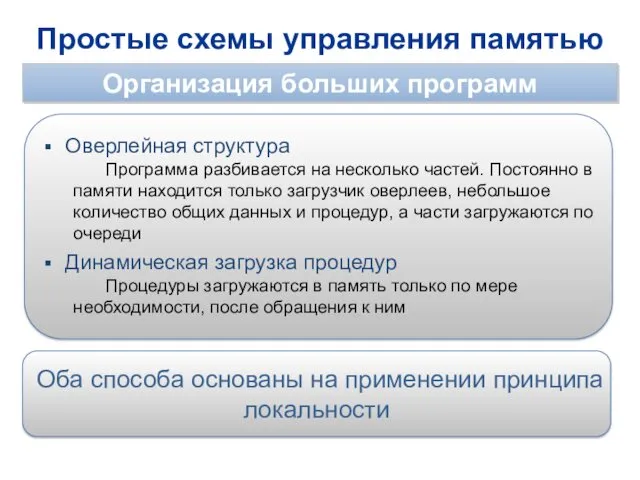

- 9. Оверлейная структура Программа разбивается на несколько частей. Постоянно в памяти находится только загрузчик оверлеев, небольшое количество

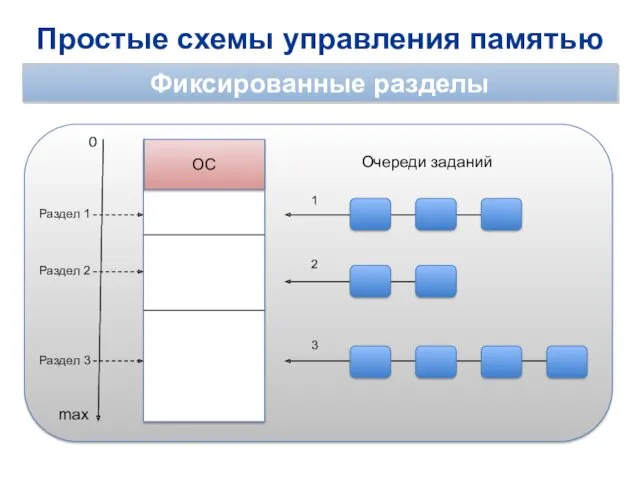

- 10. Простые схемы управления памятью Фиксированные разделы 0 ОС Раздел 1 max Раздел 2 Раздел 3 Очереди

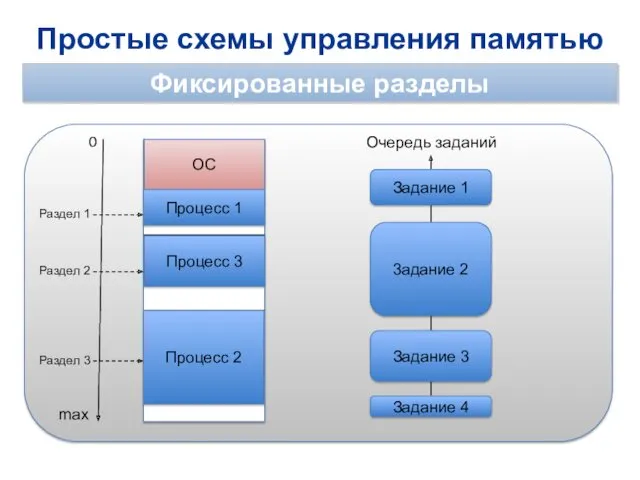

- 11. Простые схемы управления памятью Фиксированные разделы 0 ОС Раздел 1 max Раздел 2 Раздел 3 Очередь

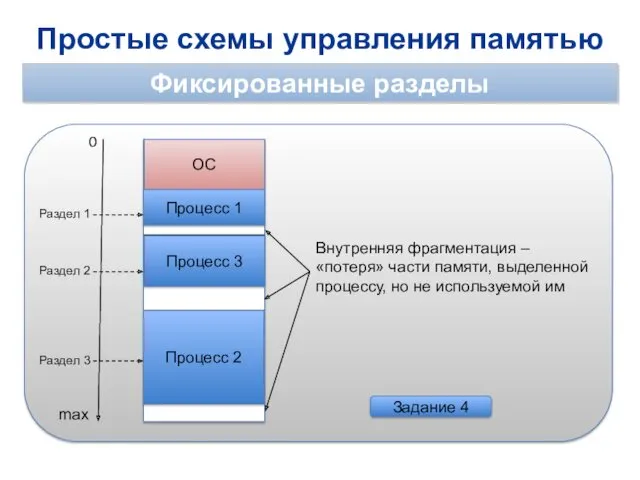

- 12. Простые схемы управления памятью Фиксированные разделы 0 ОС Раздел 1 max Раздел 2 Раздел 3 Задание

- 13. Простые схемы управления памятью Динамические разделы 0 1000 ОС 200 Очередь заданий Память 1 200 10

- 14. Простые схемы управления памятью Динамические разделы 0 1000 ОС 200 Очередь заданий Память 4 250 8

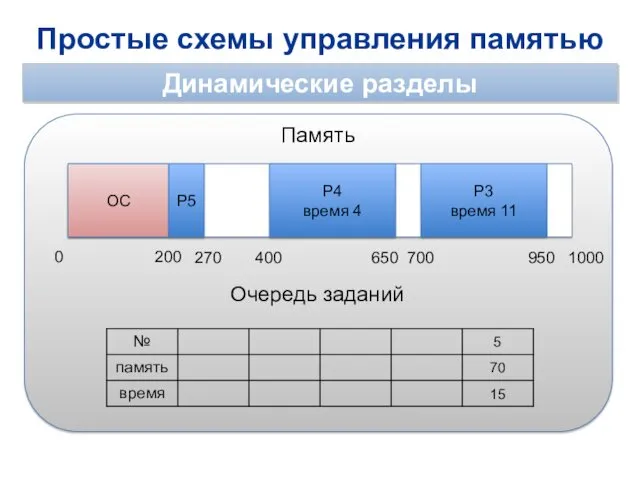

- 15. Простые схемы управления памятью Динамические разделы 0 1000 ОС 200 Очередь заданий Память 5 70 15

- 16. Простые схемы управления памятью Динамические разделы Стратегии размещения нового процесса в памяти Первый подходящий (first-fit). Процесс

- 17. Простые схемы управления памятью Динамические разделы 0 1000 ОС 200 Очередь заданий Память 5 70 15

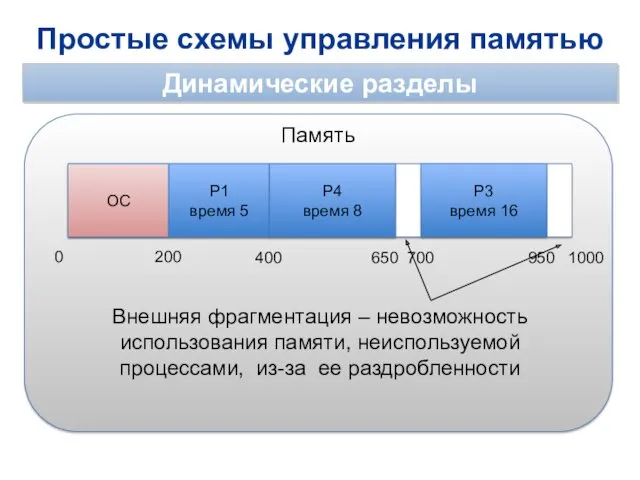

- 18. Простые схемы управления памятью Динамические разделы 0 1000 ОС 200 Внешняя фрагментация – невозможность использования памяти,

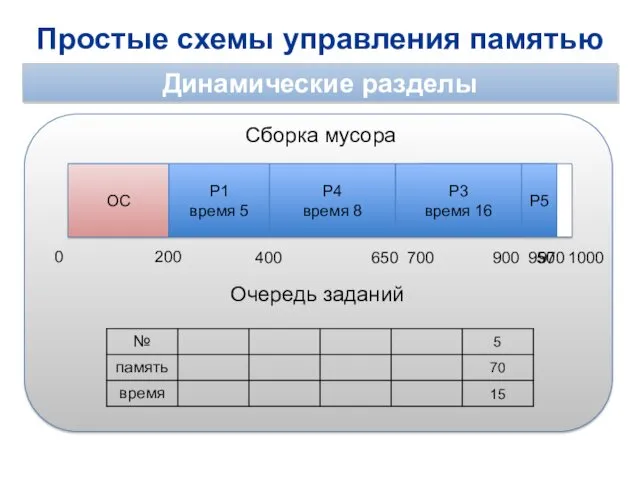

- 19. Простые схемы управления памятью Динамические разделы 0 1000 ОС 200 Очередь заданий Сборка мусора 5 70

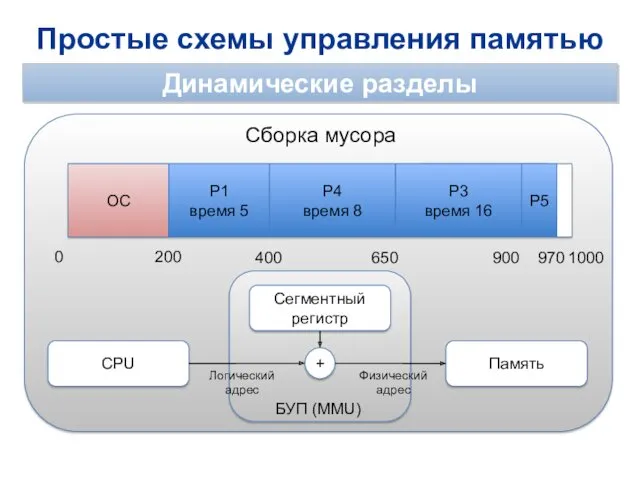

- 20. Простые схемы управления памятью Динамические разделы 0 1000 ОС 200 Сборка мусора P1 время 5 400

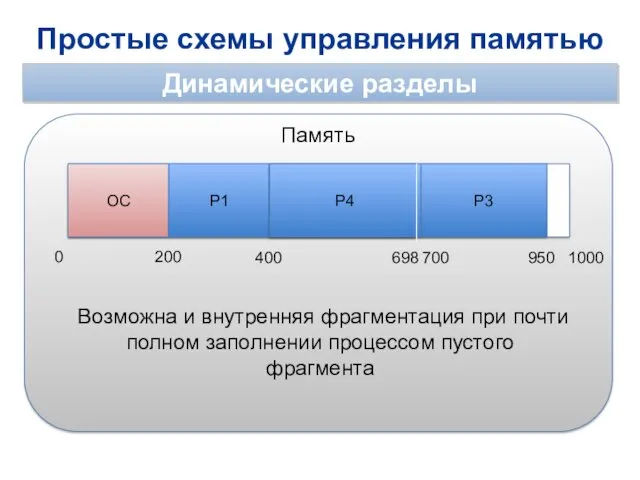

- 21. Простые схемы управления памятью Динамические разделы 0 1000 ОС 200 P1 400 700 P3 950 P4

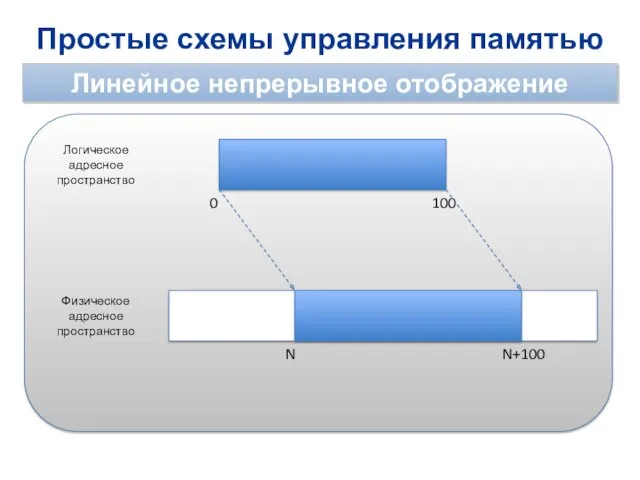

- 22. Простые схемы управления памятью Линейное непрерывное отображение Логическое адресное пространство 0 100 Физическое адресное пространство N

- 23. Кусочно-непрерывное отображение Страничная организация памяти Логическое адресное пространство Физическое адресное пространство Page 0 Page 1 Page

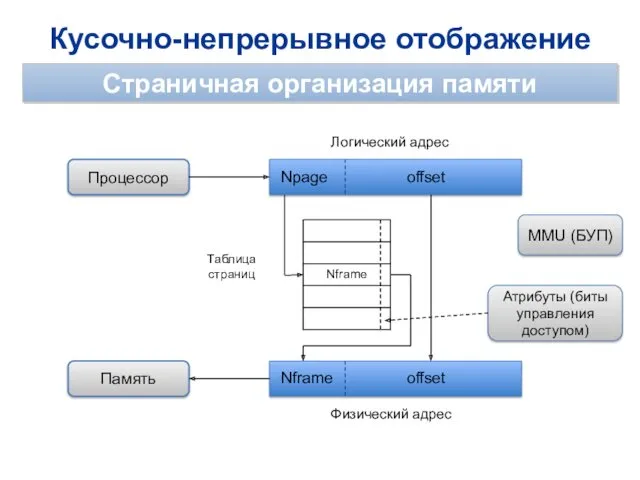

- 24. Кусочно-непрерывное отображение Страничная организация памяти Процессор Память Логический адрес Физический адрес offset offset Npage Nframe Таблица

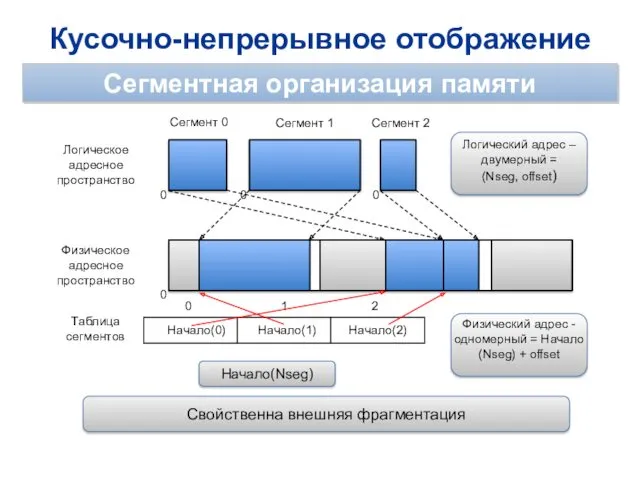

- 25. Кусочно-непрерывное отображение Сегментная организация памяти Логическое адресное пространство Физическое адресное пространство Логический адрес – двумерный =

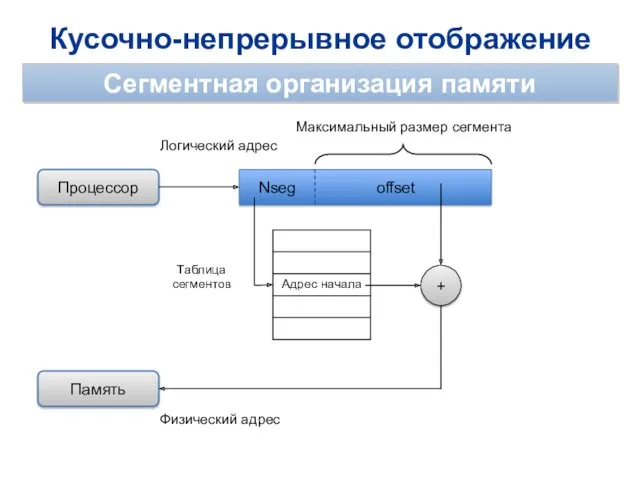

- 26. Кусочно-непрерывное отображение Сегментная организация памяти Процессор Память Логический адрес Физический адрес offset Nseg Таблица сегментов Максимальный

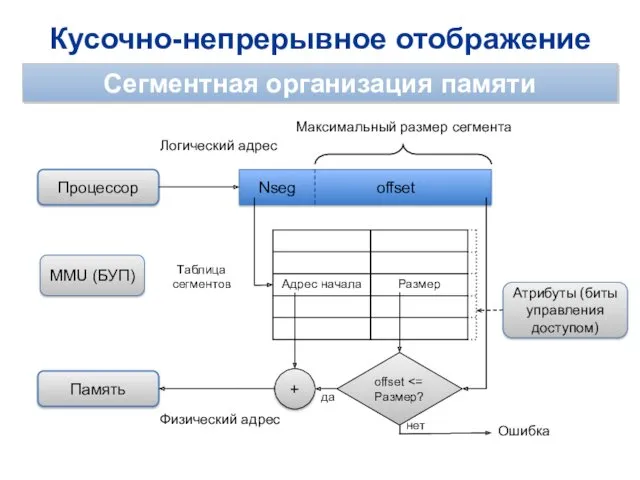

- 27. Кусочно-непрерывное отображение Сегментная организация памяти Процессор Память Логический адрес Физический адрес offset Nseg Таблица сегментов MMU

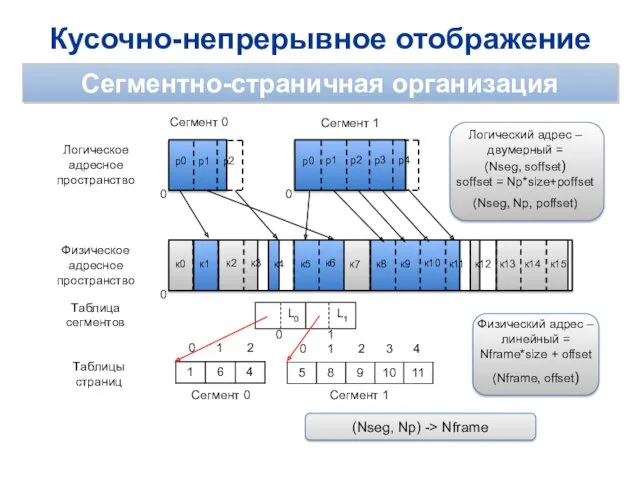

- 28. Кусочно-непрерывное отображение Сегментно-страничная организация Логическое адресное пространство Физическое адресное пространство Логический адрес – двумерный = (Nseg,

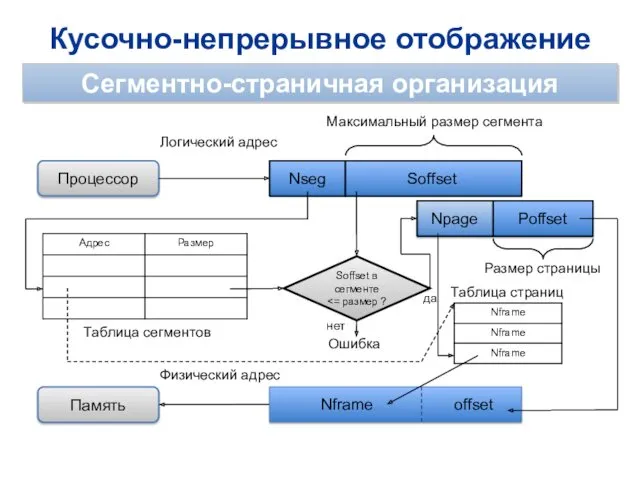

- 29. Soffset Poffset Кусочно-непрерывное отображение Сегментно-страничная организация Процессор Память Логический адрес Soffset Nseg Максимальный размер сегмента Физический

- 30. Кусочно-непрерывное отображение Многоуровневая таблица страниц Логическое адресное пространство процесса Физическое адресное пространство Page 0 Page 1

- 31. Кусочно-непрерывное отображение Многоуровневая таблица страниц Page 0 Page 1 Page 2 Page 3 0 1 2

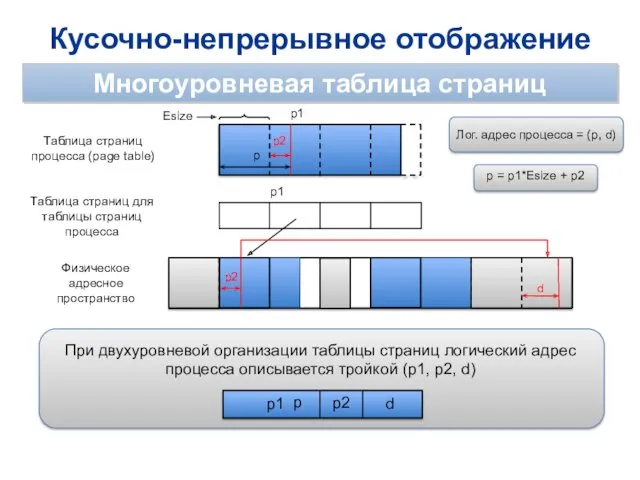

- 32. Кусочно-непрерывное отображение Многоуровневая таблица страниц p1 p1 При двухуровневой организации таблицы страниц логический адрес процесса описывается

- 33. Кусочно-непрерывное отображение Ассоциативная память (TLB) Процессор Память Логический адрес offset page Физический адрес offset Кадр TLB

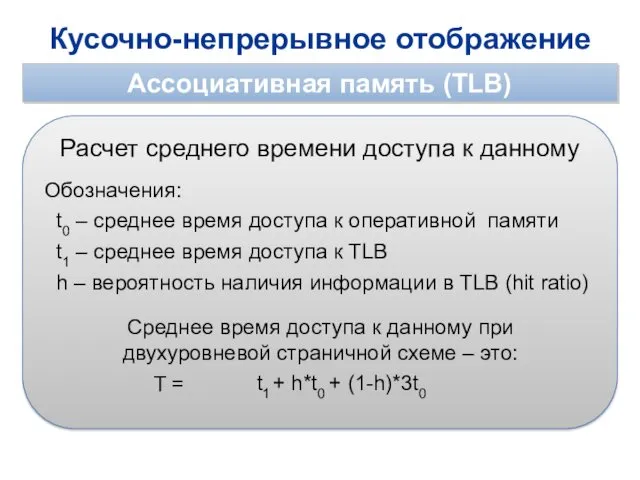

- 34. Кусочно-непрерывное отображение Ассоциативная память (TLB) Расчет среднего времени доступа к данному Обозначения: t0 – среднее время

- 36. Скачать презентацию

Показатели надежности невосстанавливаемых и восстанавливаемых объектов

Показатели надежности невосстанавливаемых и восстанавливаемых объектов Дидактические игры на уроках химии и биологии

Дидактические игры на уроках химии и биологии Микропротезирование. Вкладки, виниры. Штифтовый зуб

Микропротезирование. Вкладки, виниры. Штифтовый зуб Экологические зарисовки

Экологические зарисовки Масленица

Масленица Обобщение опыта: Развитие мелкой моторики и координации движений рук у детей младшего дошкольного возраста через игры и специальные упражнения

Обобщение опыта: Развитие мелкой моторики и координации движений рук у детей младшего дошкольного возраста через игры и специальные упражнения Анатомо-физиологические особенности дыхательной системы у детей

Анатомо-физиологические особенности дыхательной системы у детей Отравляющие вещества раздражающего действии. Клиника, диагностика, лечение

Отравляющие вещества раздражающего действии. Клиника, диагностика, лечение Металургiйний комплекс України

Металургiйний комплекс України Презентация Красная книга Саратовской области

Презентация Красная книга Саратовской области Современные гаджеты для дома

Современные гаджеты для дома Levi Strauss & Co. brand

Levi Strauss & Co. brand Обогащение бериллиевых руд. Обогащение руд и россыпей редкоземельных металлов и тория

Обогащение бериллиевых руд. Обогащение руд и россыпей редкоземельных металлов и тория Своя игра

Своя игра سياحة علاجية

سياحة علاجية Фибрилляция предсердий и её лечение

Фибрилляция предсердий и её лечение Химически опасные объекты

Химически опасные объекты преподавание регионального компонента в курсе экономической географии России

преподавание регионального компонента в курсе экономической географии России Оформление групповой комнаты

Оформление групповой комнаты Презентация к классному часу Великие женщины России

Презентация к классному часу Великие женщины России Формирование грамматически правильной речи. Дидактическая игра Чудесный мешочек

Формирование грамматически правильной речи. Дидактическая игра Чудесный мешочек Композицияның басты бөлігі

Композицияның басты бөлігі Проект Использование приёмов мультимедиа-технологий в логопедической работе. На примере занятия по развитию речи по теме: Зима

Проект Использование приёмов мультимедиа-технологий в логопедической работе. На примере занятия по развитию речи по теме: Зима Светодиоды. История создания светодиодов

Светодиоды. История создания светодиодов Windows Server 2012 R2

Windows Server 2012 R2 Основы логики

Основы логики класс Окружающий мир (1)

класс Окружающий мир (1) Сущность железобетонных конструкций

Сущность железобетонных конструкций