Содержание

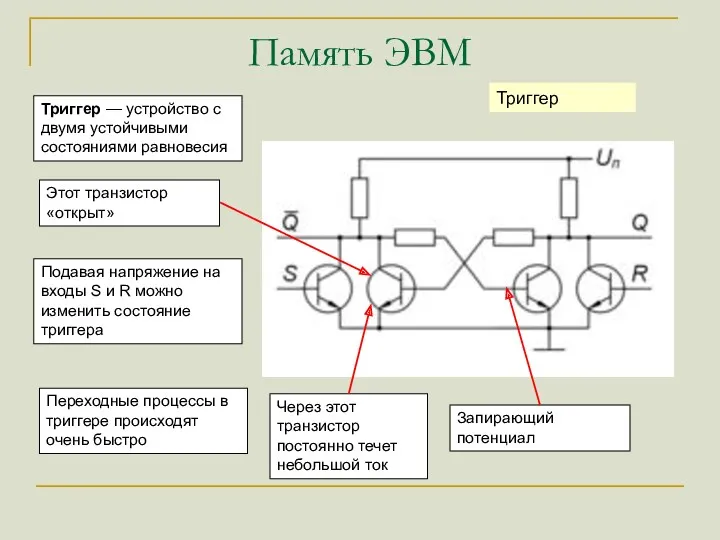

- 2. Память ЭВМ Триггер — устройство с двумя устойчивыми состояниями равновесия Триггер Этот транзистор «открыт» Запирающий потенциал

- 3. Память ЭВМ Статическая оперативная память с произвольным доступом (SRAM, static random access memory) Выполнена из триггеров.

- 4. Память ЭВМ DRAM (dynamic random access memory) DRAM-память представляет собой набор запоминающих ячеек, которые состоят из

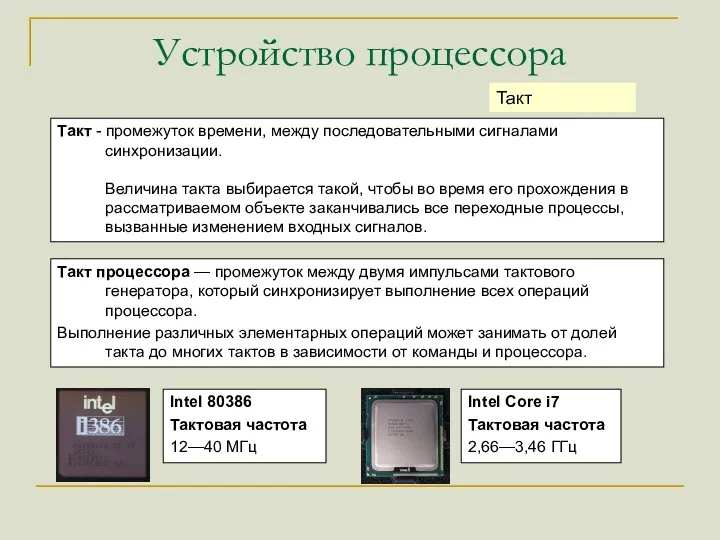

- 5. Устройство процессора Такт Такт процессора — промежуток между двумя импульсами тактового генератора, который синхронизирует выполнение всех

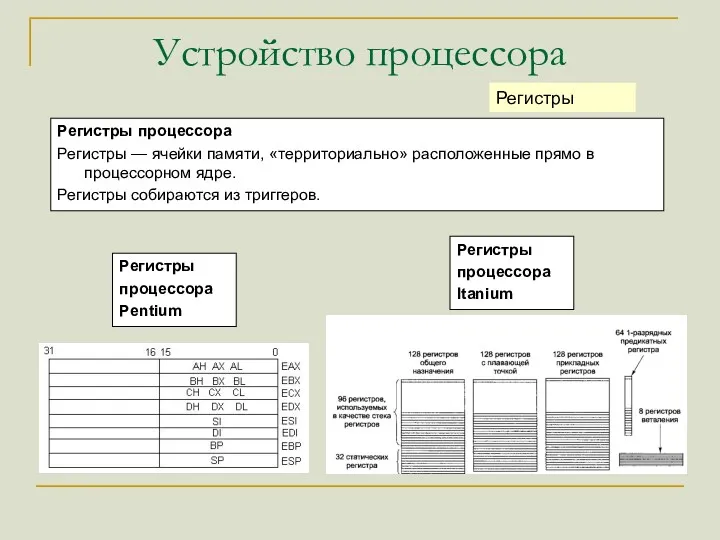

- 6. Устройство процессора Регистры Регистры процессора Pentium Регистры процессора Регистры — ячейки памяти, «территориально» расположенные прямо в

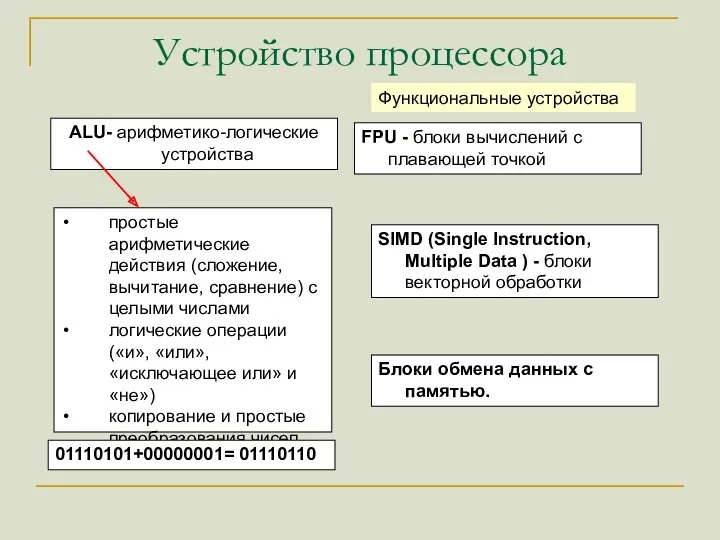

- 7. Устройство процессора Функциональные устройства простые арифметические действия (сложение, вычитание, сравнение) с целыми числами логические операции («и»,

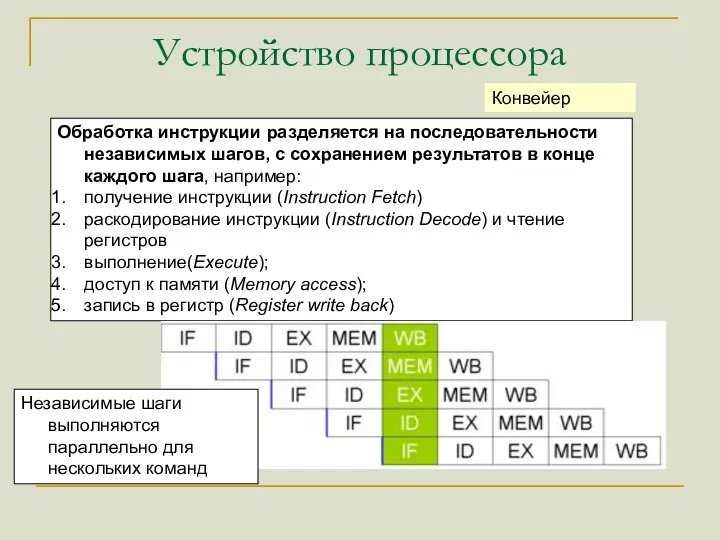

- 8. Устройство процессора Конвейер Обработка инструкции разделяется на последовательности независимых шагов, с сохранением результатов в конце каждого

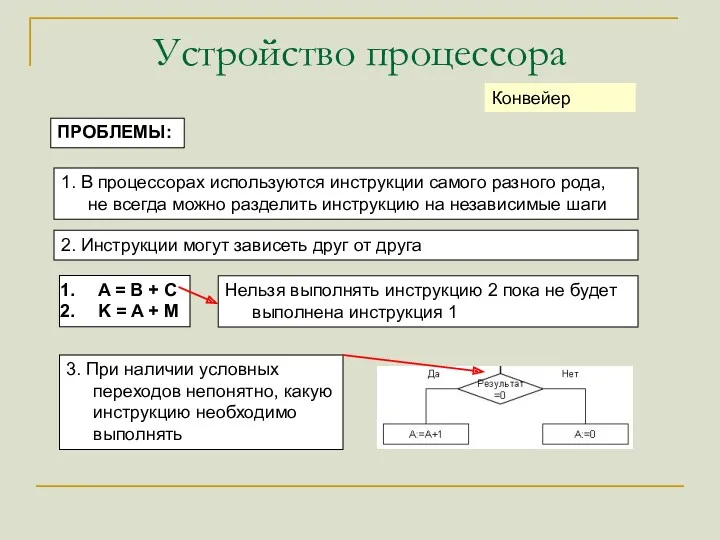

- 9. Устройство процессора Конвейер ПРОБЛЕМЫ: 1. В процессорах используются инструкции самого разного рода, не всегда можно разделить

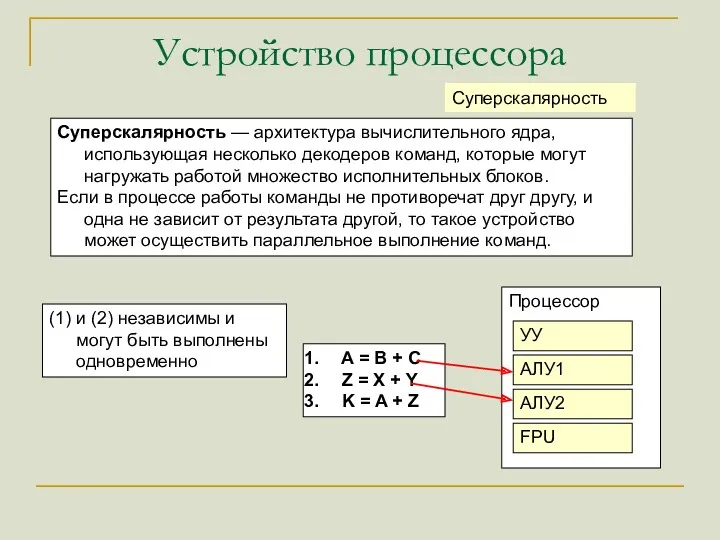

- 10. Процессор Устройство процессора Суперскалярность Суперскалярность — архитектура вычислительного ядра, использующая несколько декодеров команд, которые могут нагружать

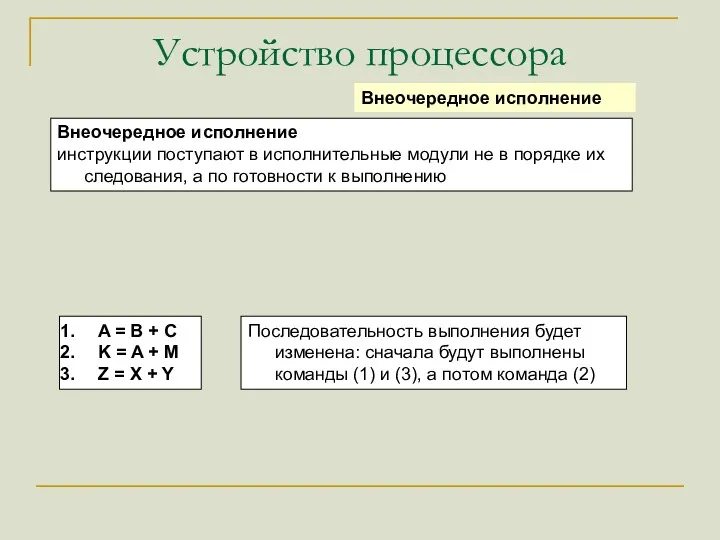

- 11. Устройство процессора Внеочередное исполнение Внеочередное исполнение инструкции поступают в исполнительные модули не в порядке их следования,

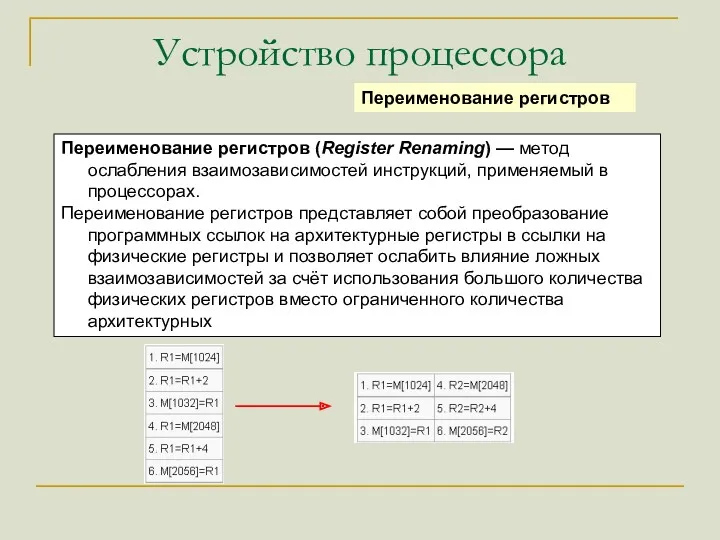

- 12. Устройство процессора Переименование регистров Переименование регистров (Register Renaming) — метод ослабления взаимозависимостей инструкций, применяемый в процессорах.

- 14. Скачать презентацию

Особенности рельефа территории России

Особенности рельефа территории России Презентация Дифференциация звуков Б - П

Презентация Дифференциация звуков Б - П Пожары и взрывы

Пожары и взрывы Красота планеты Земля

Красота планеты Земля Кремний и его соединения. 9 класс

Кремний и его соединения. 9 класс Презентация Семечковые плоды

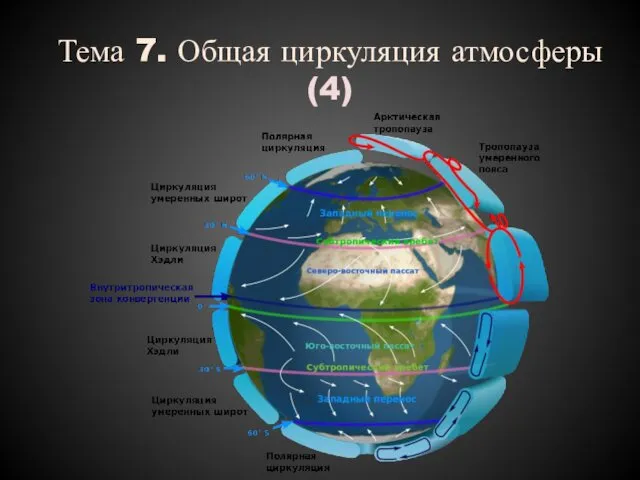

Презентация Семечковые плоды Общая циркуляция атмосферы ( часть 4)

Общая циркуляция атмосферы ( часть 4) Простые истины эндокринологии. Эндокринология в искусстве

Простые истины эндокринологии. Эндокринология в искусстве ЗАО СК Спецподземстрой

ЗАО СК Спецподземстрой Выступление по теме: Организация метапредметного урока в начальной школе в условиях технологии проблемно-диалогического обучения

Выступление по теме: Организация метапредметного урока в начальной школе в условиях технологии проблемно-диалогического обучения К. Троекуров и А. Дубровский

К. Троекуров и А. Дубровский Сельское хозяйство Мексики

Сельское хозяйство Мексики Особенности проекта НВАЭС-2

Особенности проекта НВАЭС-2 Закономерности наследования признаков

Закономерности наследования признаков Машины для укладки и обслуживания дорожных покрытий

Машины для укладки и обслуживания дорожных покрытий Правила оформления исследовательского проекта

Правила оформления исследовательского проекта Программное обеспечение компьютера

Программное обеспечение компьютера Дифференциальная диагностика менингиального синдрома

Дифференциальная диагностика менингиального синдрома Презентация программы второй младшей группы дошкольной организации, ориентированной на родителей (законных представителей) детей с учетом регионального компонента

Презентация программы второй младшей группы дошкольной организации, ориентированной на родителей (законных представителей) детей с учетом регионального компонента Организм и среда. Природные сообщества

Организм и среда. Природные сообщества Fruit-name, colours,count

Fruit-name, colours,count Экономика нефтегазовой отрасли

Экономика нефтегазовой отрасли Урок - аукцион по темеПодгруппа углерода

Урок - аукцион по темеПодгруппа углерода Cenotaph War Memorial, London

Cenotaph War Memorial, London Моя прабабушка на войне

Моя прабабушка на войне Показатели надежности невосстанавливаемых и восстанавливаемых объектов

Показатели надежности невосстанавливаемых и восстанавливаемых объектов Особенности государственного управления особыми экономическими зонами на примере Ульяновской ПОЭЗ

Особенности государственного управления особыми экономическими зонами на примере Ульяновской ПОЭЗ Структура строительных процессов и технологий

Структура строительных процессов и технологий