Содержание

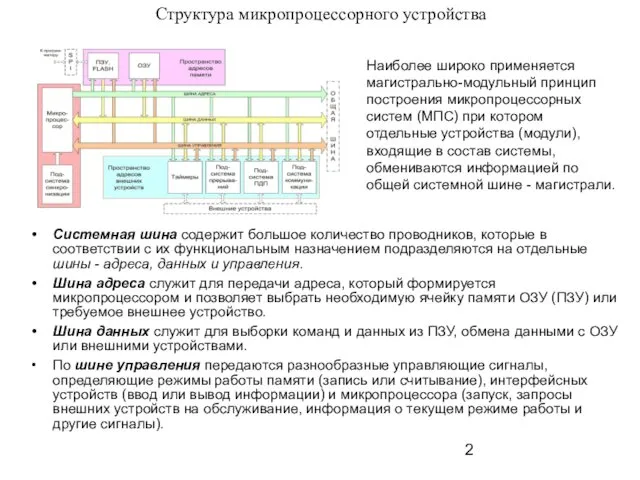

- 2. Структура микропроцессорного устройства Системная шина содержит большое количество проводников, которые в соответствии с их функциональным назначением

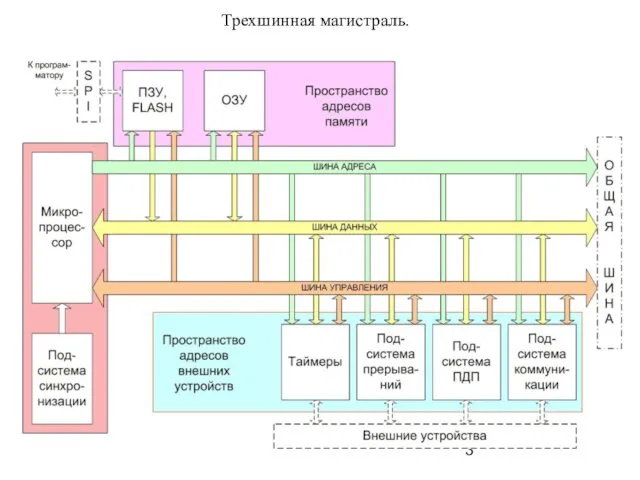

- 3. Трехшинная магистраль.

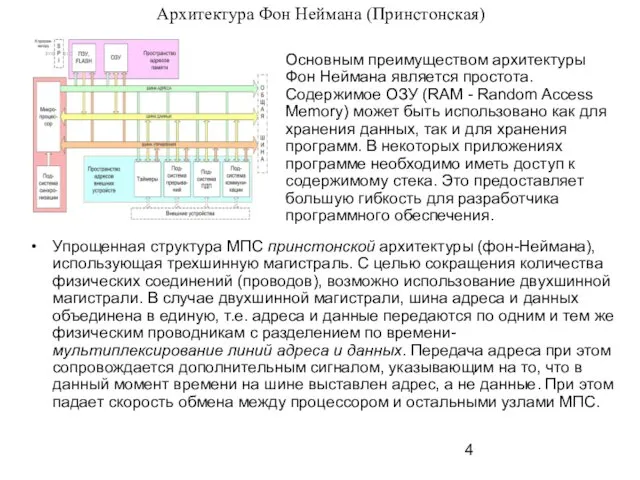

- 4. Архитектура Фон Неймана (Принстонская) Упрощенная структура МПС принстонской архитектуры (фон-Неймана), использующая трехшинную магистраль. С целью сокращения

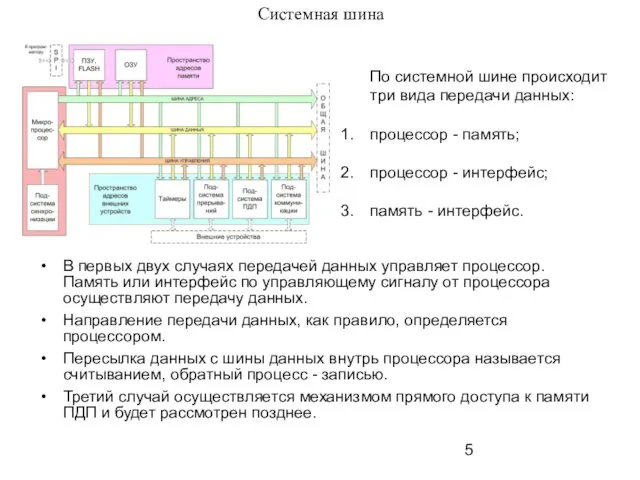

- 5. Системная шина В первых двух случаях передачей данных управляет процессор. Память или интерфейс по управляющему сигналу

- 6. ЦПУ, Синхронизация Центральным процессорным устройством (ЦПУ) в системе является микропроцессор (МП), выполняющий арифметические и логические операции

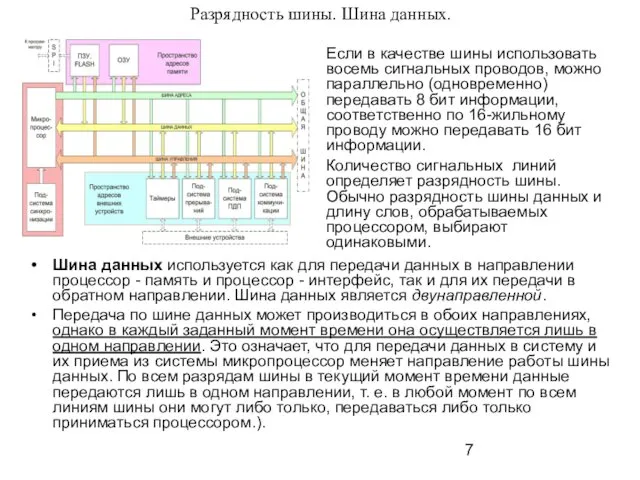

- 7. Разрядность шины. Шина данных. Шина данных используется как для передачи данных в направлении процессор - память

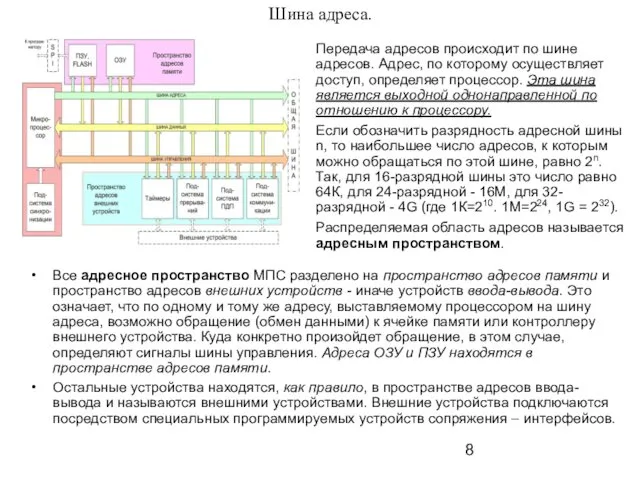

- 8. Шина адреса. Все адресное пространство МПС разделено на пространство адресов памяти и пространство адресов внешних устройств

- 9. Шина управления. Основными сигналами, передаваемыми по этой шине, являются сигналы управления записью-чтением из памяти и сигналы

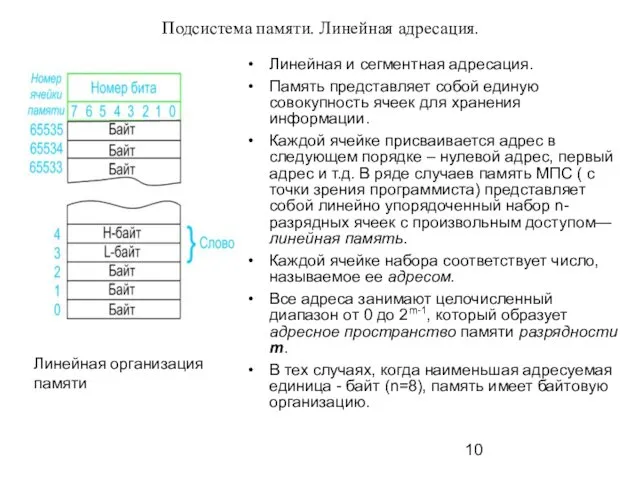

- 10. Подсистема памяти. Линейная адресация. Линейная и сегментная адресация. Память представляет собой единую совокупность ячеек для хранения

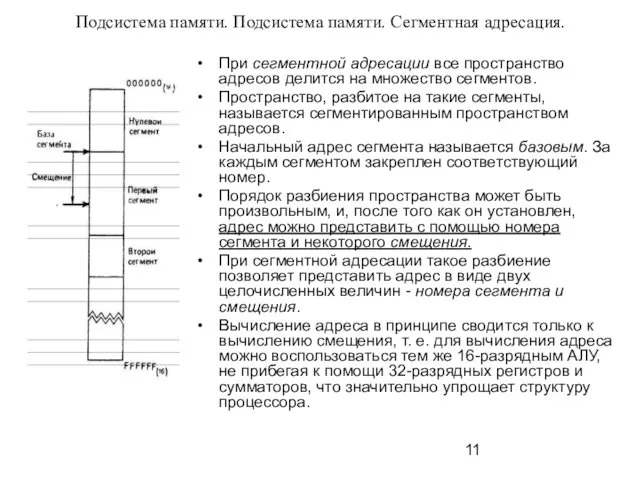

- 11. Подсистема памяти. Подсистема памяти. Сегментная адресация. При сегментной адресации все пространство адресов делится на множество сегментов.

- 12. Сегментация, логические и физические адреса. Программы «видят» пространство памяти как группу сегментов, определяемых самой программой. Сегмент

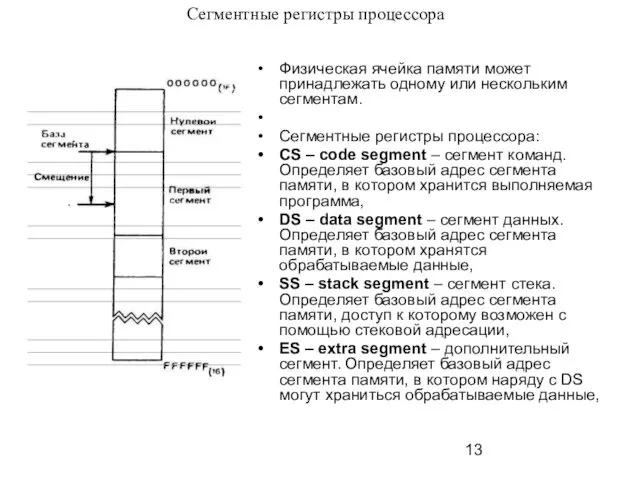

- 13. Сегментные регистры процессора Физическая ячейка памяти может принадлежать одному или нескольким сегментам. Сегментные регистры процессора: CS

- 14. Физические и логические адреса. Сегмент, смещение. Каждая ячейка памяти имеет два адреса: физический и логический. Физический

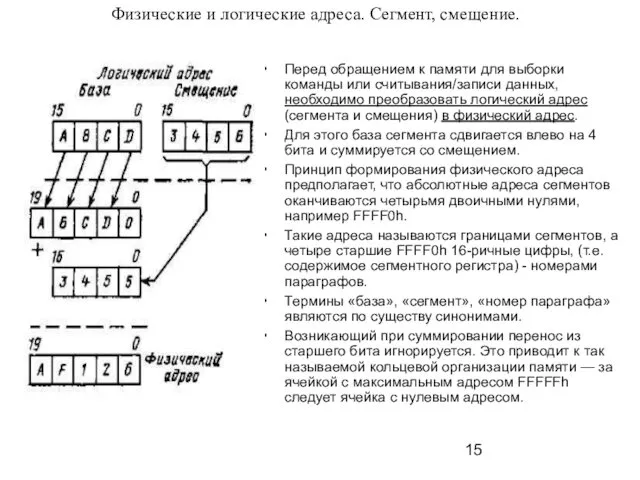

- 15. Физические и логические адреса. Сегмент, смещение. Перед обращением к памяти для выборки команды или считывания/записи данных,

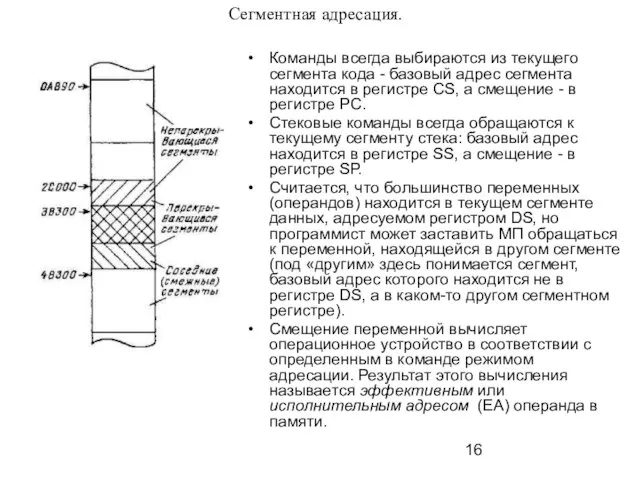

- 16. Сегментная адресация. Команды всегда выбираются из текущего сегмента кода - базовый адрес сегмента находится в регистре

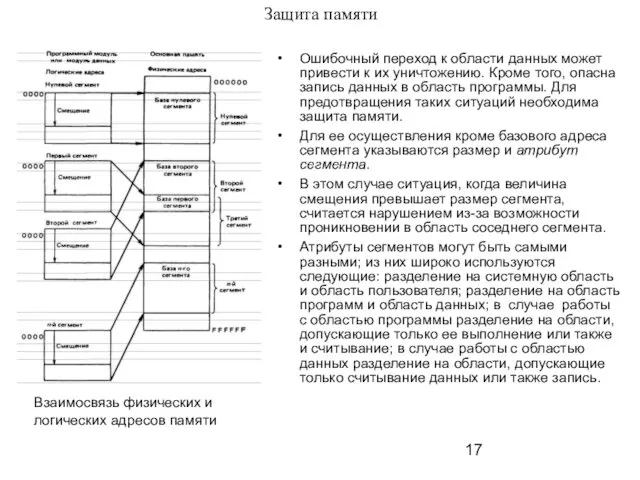

- 17. Защита памяти Ошибочный переход к области данных может привести к их уничтожению. Кроме того, опасна запись

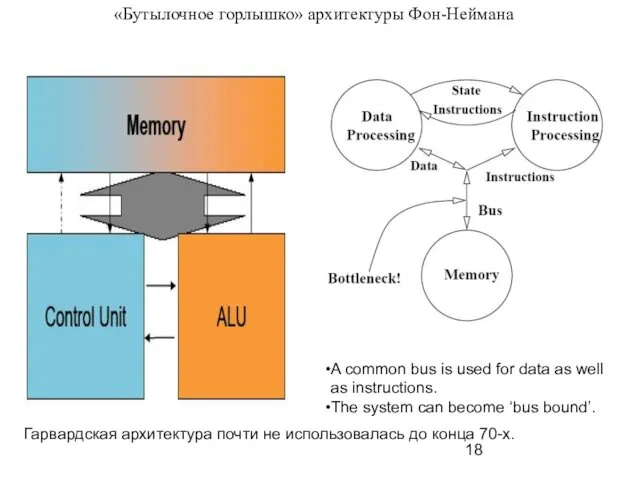

- 18. «Бутылочное горлышко» архитектуры Фон-Неймана A common bus is used for data as well as instructions. The

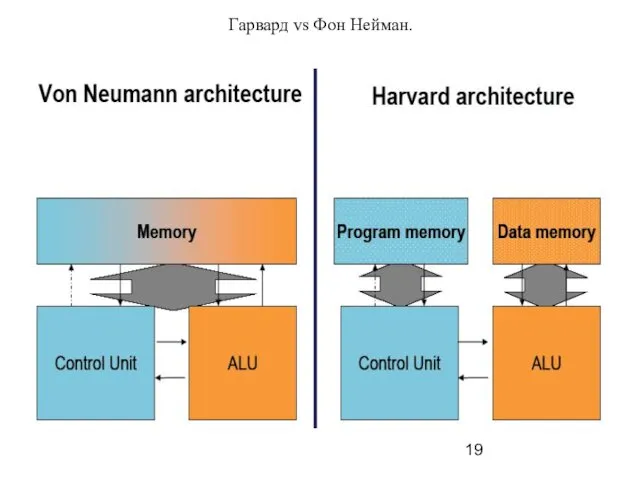

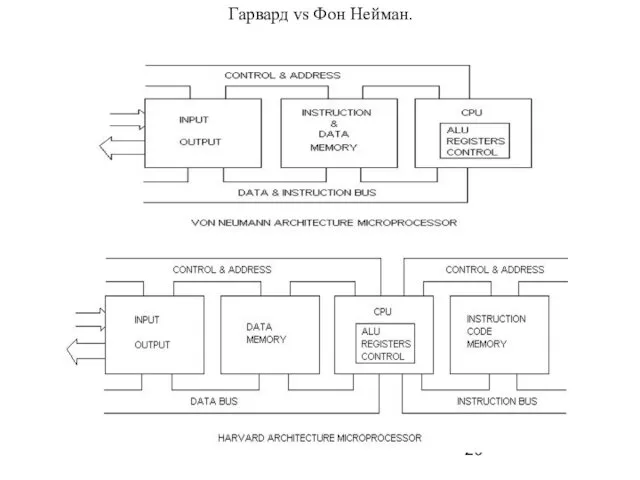

- 19. Гарвард vs Фон Нейман.

- 20. Гарвард vs Фон Нейман.

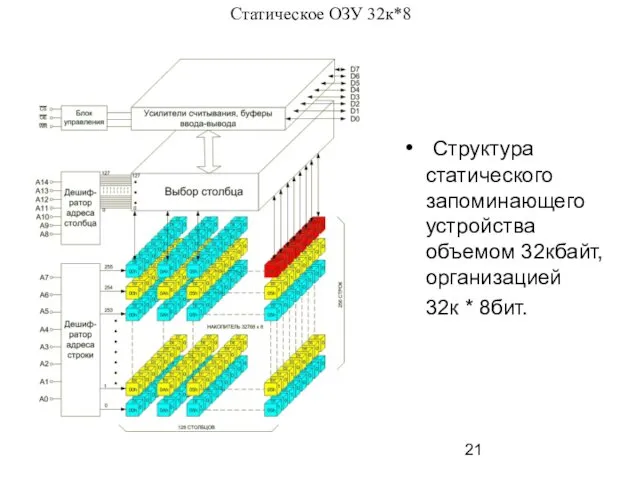

- 21. Статическое ОЗУ 32к*8 Структура статического запоминающего устройства объемом 32кбайт, организацией 32к * 8бит.

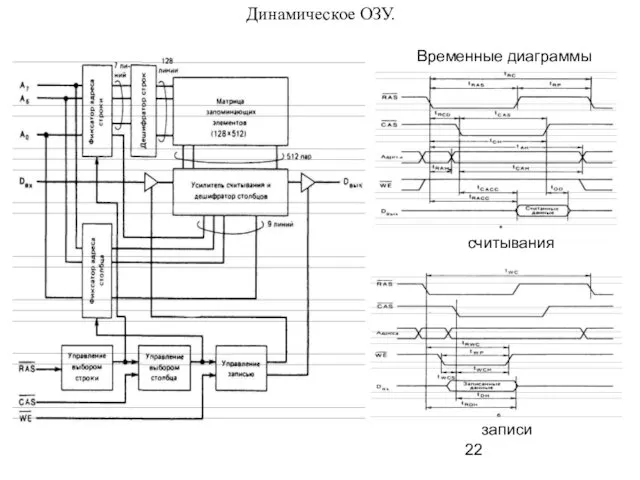

- 22. Динамическое ОЗУ. считывания Временные диаграммы записи

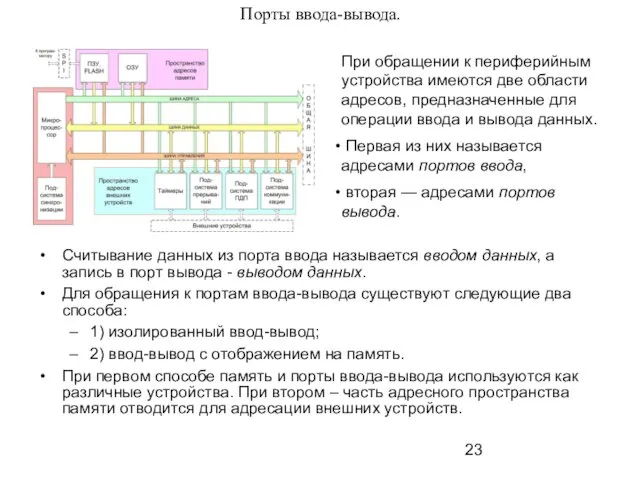

- 23. Порты ввода-вывода. Считывание данных из порта ввода называется вводом данных, а запись в порт вывода -

- 24. Порты ввода-вывода. Как правило, на практике используется первый способ. Для осуществления ввода-вывода при этом способе применяются

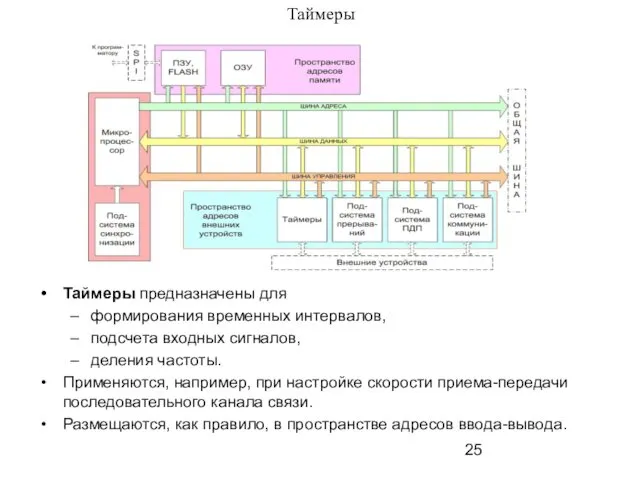

- 25. Таймеры Таймеры предназначены для формирования временных интервалов, подсчета входных сигналов, деления частоты. Применяются, например, при настройке

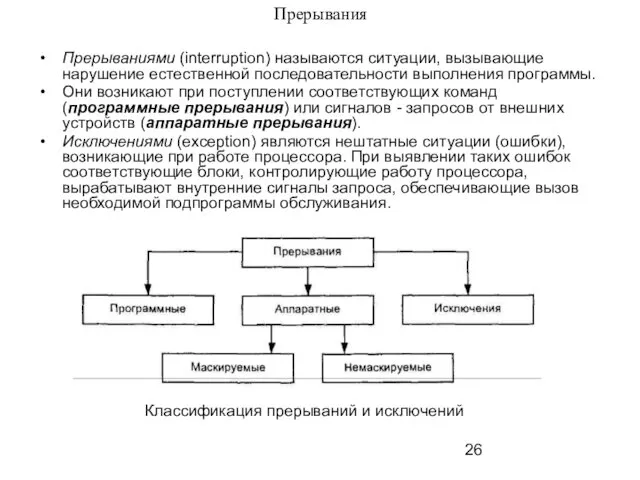

- 26. Прерывания Прерываниями (interruption) называются ситуации, вызывающие нарушение естественной последовательности выполнения программы. Они возникают при поступлении соответствующих

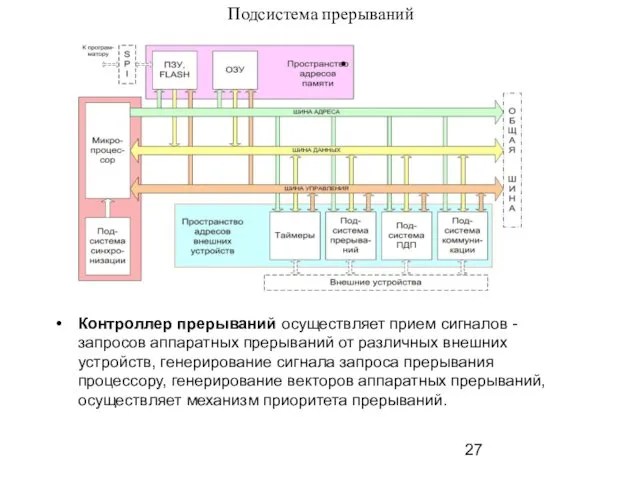

- 27. Подсистема прерываний Контроллер прерываний осуществляет прием сигналов - запросов аппаратных прерываний от различных внешних устройств, генерирование

- 28. Подсистема прерываний Во всех этих ситуациях микропроцессор завершает выполнение очередной команды и заносит в стек текущее

- 29. Прерывания Аппаратные прерывания могут быть маскируемые или немаскируемые. Запросы маскируемых прерываний обслуживаются только в том случае,

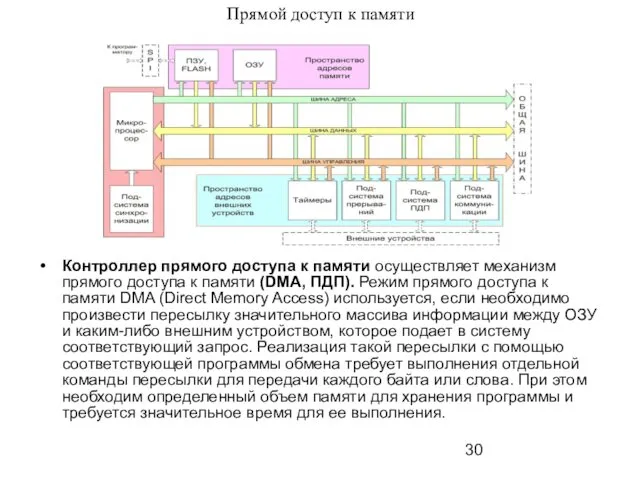

- 30. Прямой доступ к памяти Контроллер прямого доступа к памяти осуществляет механизм прямого доступа к памяти (DMA,

- 31. Механизм ПДП В большинстве современных микропроцессорных систем пересылка массивов информации обеспечивается с помощью специальных устройств -

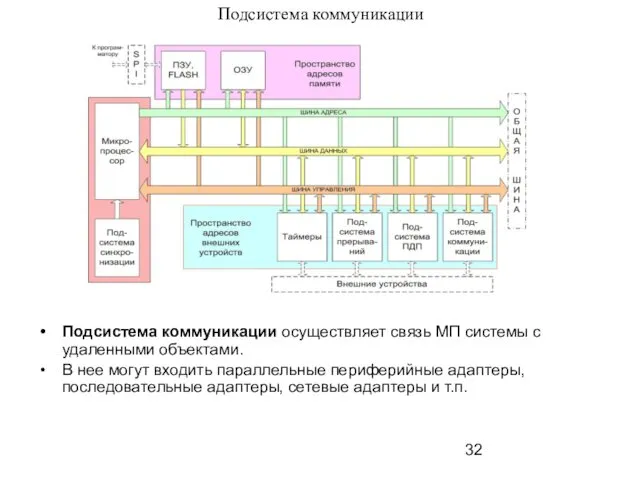

- 32. Подсистема коммуникации Подсистема коммуникации осуществляет связь МП системы с удаленными объектами. В нее могут входить параллельные

- 33. Архитектура Фон Неймана (Принстонская)

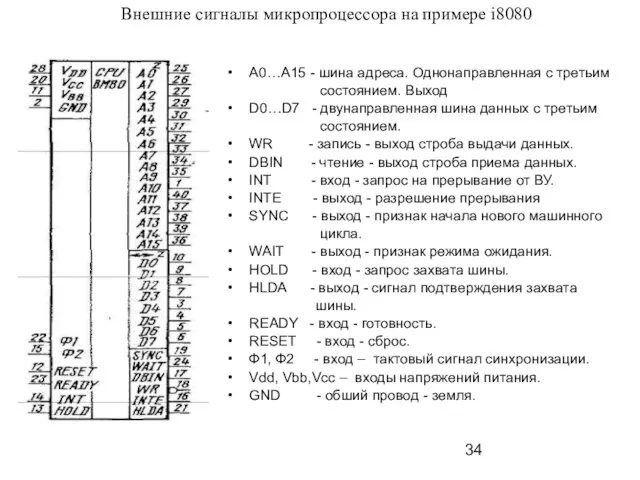

- 34. Внешние сигналы микропроцессора на примере i8080 А0…А15 - шина адреса. Однонаправленная с третьим состоянием. Выход D0…D7

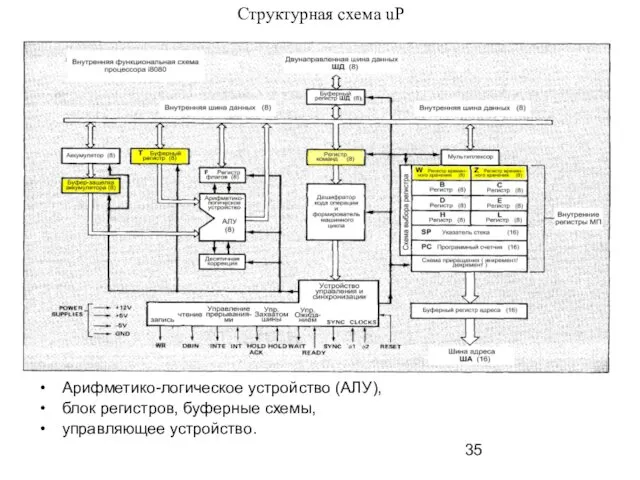

- 35. Структурная схема uP Арифметико-логическое устройство (АЛУ), блок регистров, буферные схемы, управляющее устройство.

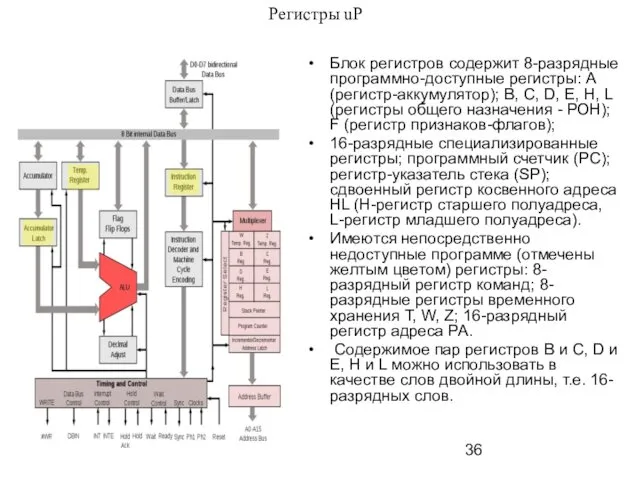

- 36. Регистры uP Блок регистров содержит 8-разрядные программно-доступные регистры: А (регистр-аккумулятор); В, С, D, Е, Н, L

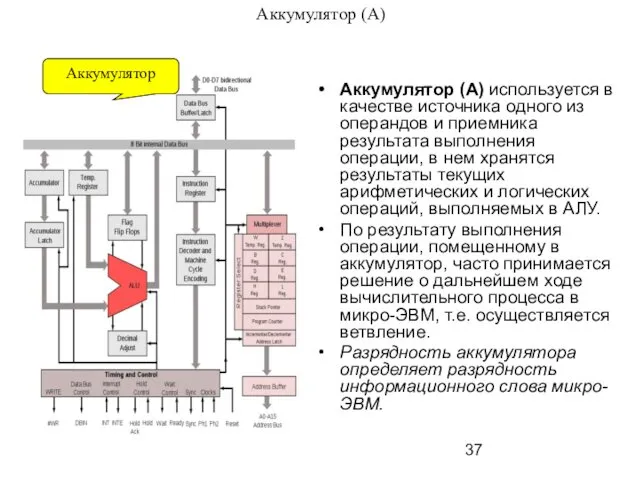

- 37. Аккумулятор (А) Аккумулятор (А) используется в качестве источника одного из операндов и приемника результата выполнения операции,

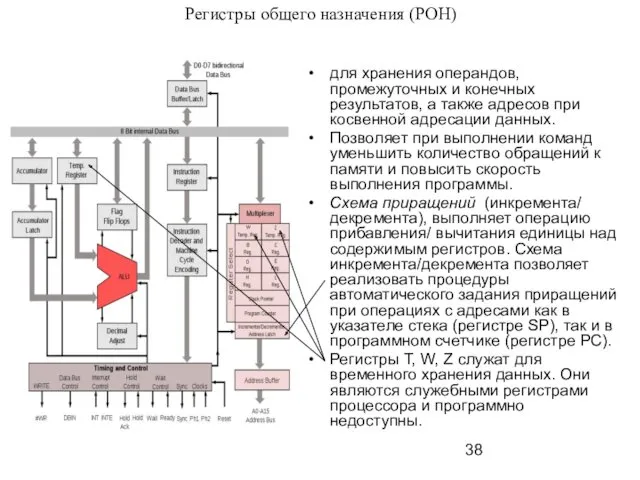

- 38. Регистры общего назначения (РОН) для хранения операндов, промежуточных и конечных результатов, а также адресов при косвенной

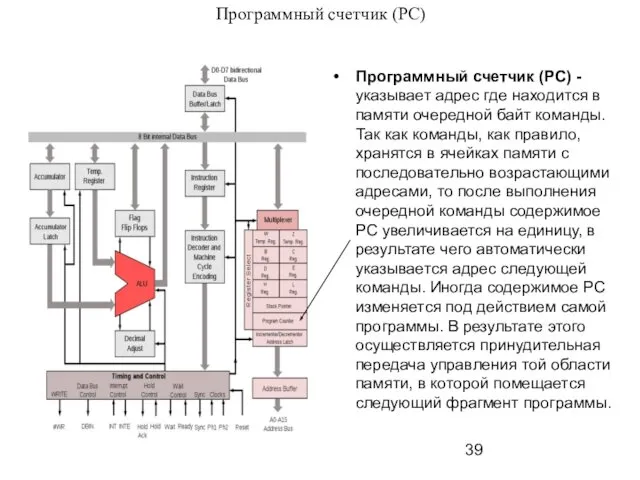

- 39. Программный счетчик (PC) Программный счетчик (PC) - указывает адрес где находится в памяти очередной байт команды.

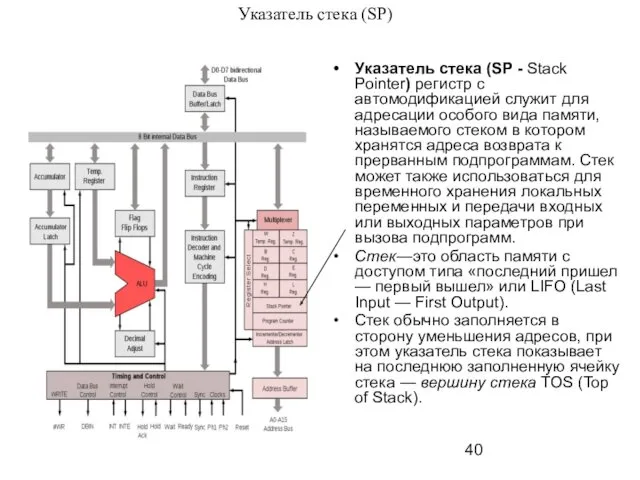

- 40. Указатель стека (SP) Указатель стека (SP - Stack Pointer) регистр с автомодификацией служит для адресации особого

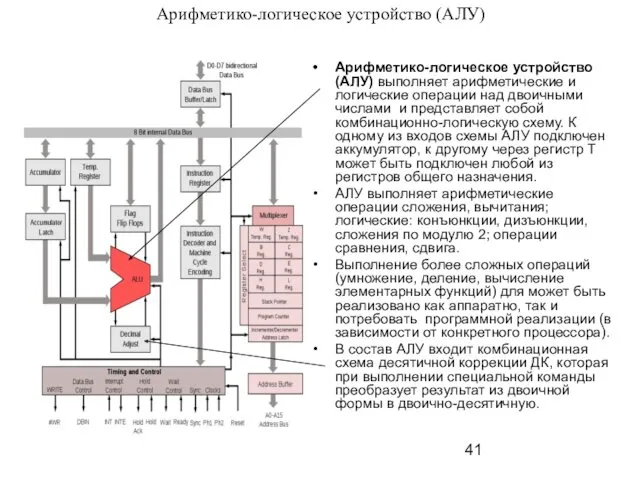

- 41. Арифметико-логическое устройство (АЛУ) Арифметико-логическое устройство (АЛУ) выполняет арифметические и логические операции над двоичными числами и представляет

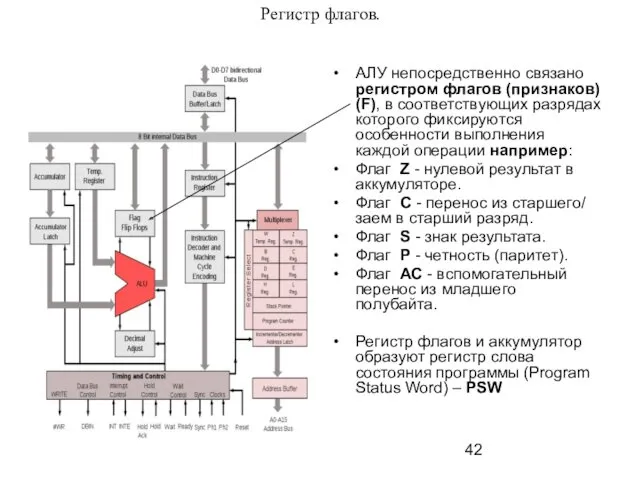

- 42. Регистр флагов. АЛУ непосредственно связано регистром флагов (признаков) (F), в соответствующих разрядах которого фиксируются особенности выполнения

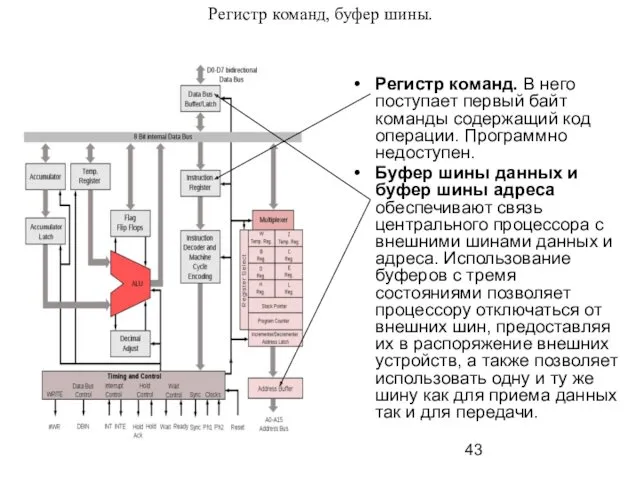

- 43. Регистр команд, буфер шины. Регистр команд. В него поступает первый байт команды содержащий код операции. Программно

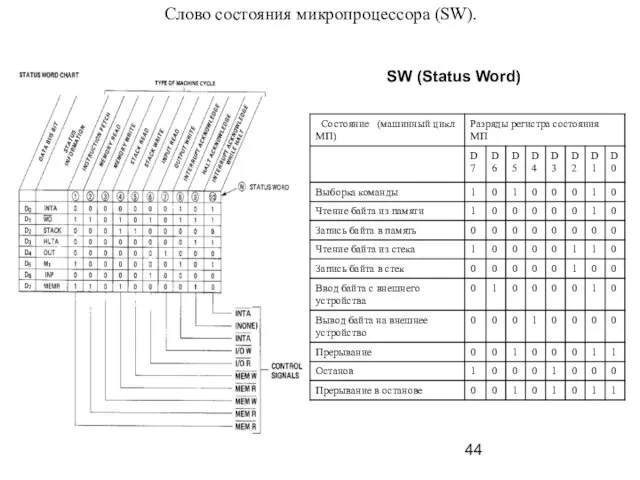

- 44. Слово состояния микропроцессора (SW). SW (Status Word)

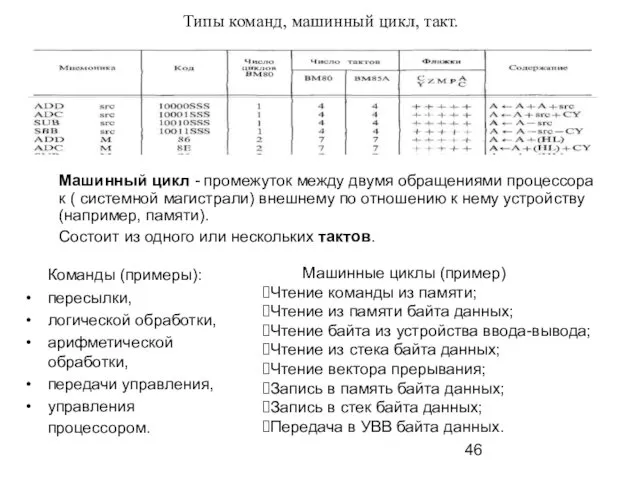

- 46. Типы команд, машинный цикл, такт. Команды (примеры): пересылки, логической обработки, арифметической обработки, передачи управления, управления процессором.

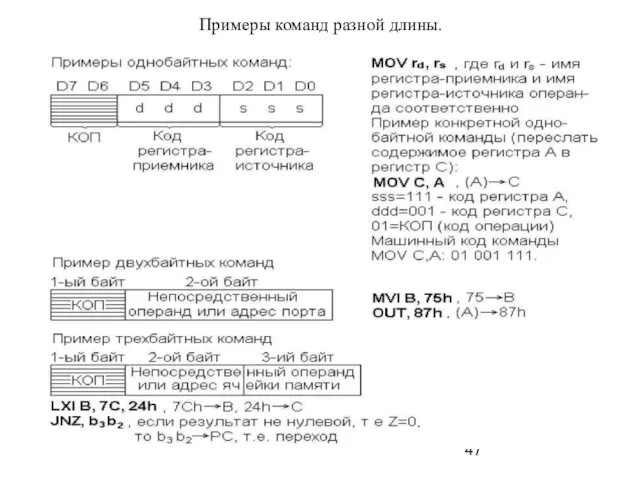

- 47. Примеры команд разной длины.

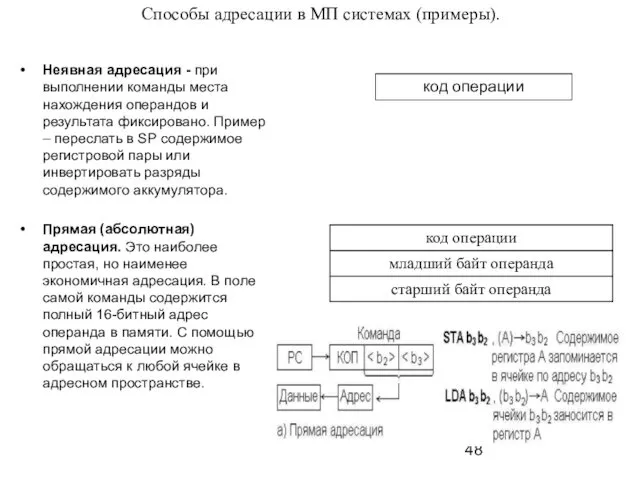

- 48. Способы адресации в МП системах (примеры). Неявная адресация - при выполнении команды места нахождения операндов и

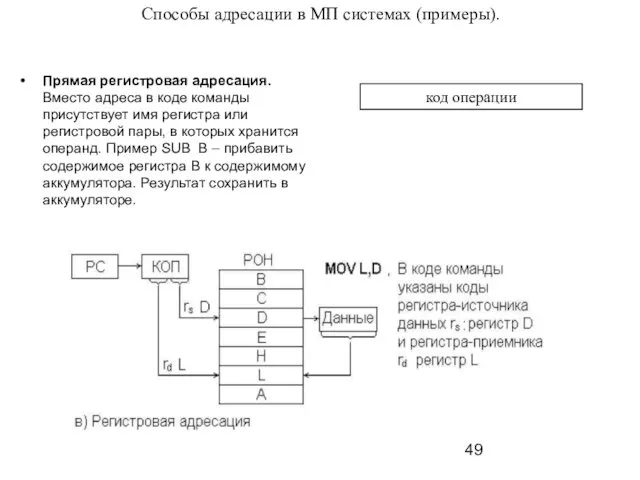

- 49. Способы адресации в МП системах (примеры). Прямая регистровая адресация. Вместо адреса в коде команды присутствует имя

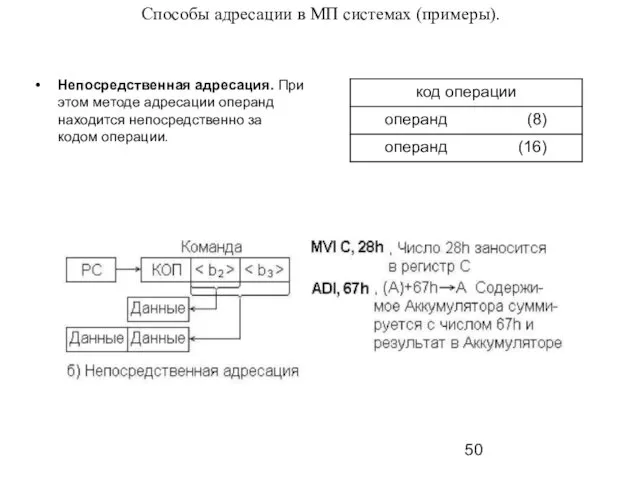

- 50. Способы адресации в МП системах (примеры). Непосредственная адресация. При этом методе адресации операнд находится непосредственно за

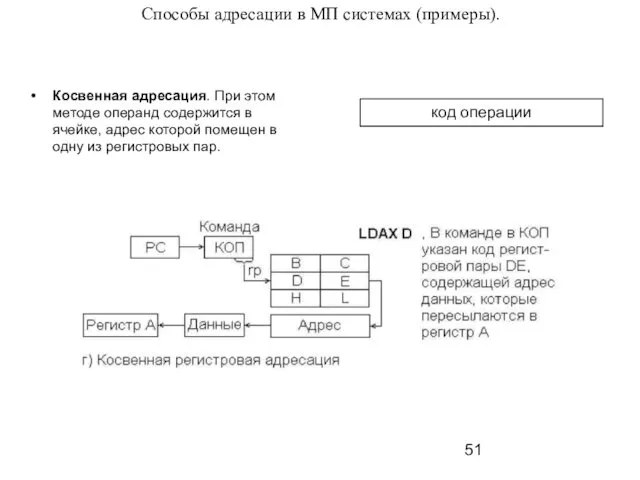

- 51. Способы адресации в МП системах (примеры). Косвенная адресация. При этом методе операнд содержится в ячейке, адрес

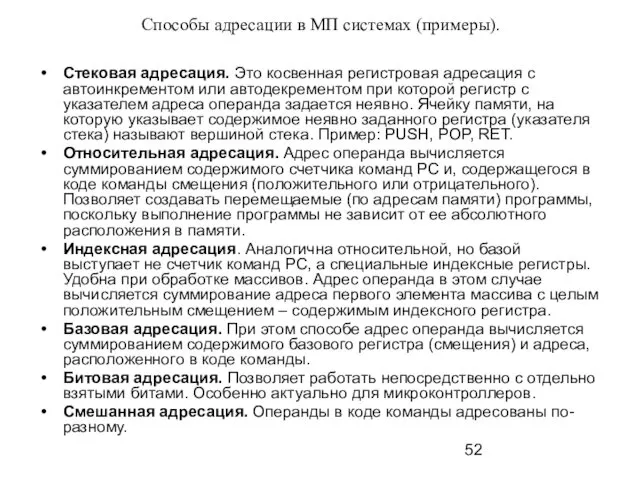

- 52. Способы адресации в МП системах (примеры). Стековая адресация. Это косвенная регистровая адресация с автоинкрементом или автодекрементом

- 54. Скачать презентацию

Память и внимание младших дошкольников 3-5 лет

Память и внимание младших дошкольников 3-5 лет Гражданские и сельскохозяйственные здания и сооружения. Основания и фундаменты

Гражданские и сельскохозяйственные здания и сооружения. Основания и фундаменты Гоголь

Гоголь Основы фотографии

Основы фотографии Ответственность в хозяйственном праве

Ответственность в хозяйственном праве Классный час Вредные привычки

Классный час Вредные привычки Этнический (национальный) состав населения России. 8 класс

Этнический (национальный) состав населения России. 8 класс Внеурочная работа с одарёнными детьми.

Внеурочная работа с одарёнными детьми. Влияние факторов окружающей среды на физическую работоспособность

Влияние факторов окружающей среды на физическую работоспособность Воспевание У. Шекспиром любви и дружбы. Сонет как форма лирической поэзии

Воспевание У. Шекспиром любви и дружбы. Сонет как форма лирической поэзии prezent_insp

prezent_insp Основы защиты населения и территорий в ЧС природного и техногенного характера. Тема 5. Занятие 5/1

Основы защиты населения и территорий в ЧС природного и техногенного характера. Тема 5. Занятие 5/1 Фоторепортаж из Маленькой страны. Диск

Фоторепортаж из Маленькой страны. Диск География России

География России Восход династии Романовых

Восход династии Романовых Международные стандарты финансовой отчетности МСФО (IAS) 10 События после отчётного периода

Международные стандарты финансовой отчетности МСФО (IAS) 10 События после отчётного периода Мастер-класс по изготовлению мягкой игрушки Божья коровка.

Мастер-класс по изготовлению мягкой игрушки Божья коровка. Музыка Кубани

Музыка Кубани Санитарно-гигиенические условия обеспечения учебного процесса

Санитарно-гигиенические условия обеспечения учебного процесса 华为手表表盘制作指导书

华为手表表盘制作指导书 Аутизм. Психолого - педагогическая коррекция аутизма

Аутизм. Психолого - педагогическая коррекция аутизма Модернизация секции 200 установки ЛК-6У №1 ОАО Мозырский НПЗ с целью увеличения выхода катализата

Модернизация секции 200 установки ЛК-6У №1 ОАО Мозырский НПЗ с целью увеличения выхода катализата Презентация к уроку технологии Аппликация Осень в лесу

Презентация к уроку технологии Аппликация Осень в лесу Материал о создании музея Остров Котлин в школе № 422 Кронштадта.

Материал о создании музея Остров Котлин в школе № 422 Кронштадта. Разработка алгоритма повышения помехоустойчивости канала связи с использованием технологии MIMO

Разработка алгоритма повышения помехоустойчивости канала связи с использованием технологии MIMO Проект Создаём портрет слова ябеда

Проект Создаём портрет слова ябеда Евгений Иванович Замятин (1884–1937)

Евгений Иванович Замятин (1884–1937) Готовая преза с триггерами

Готовая преза с триггерами