Слайд 2

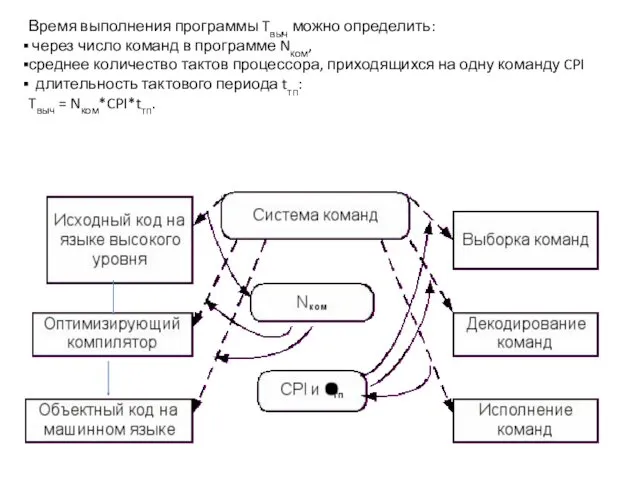

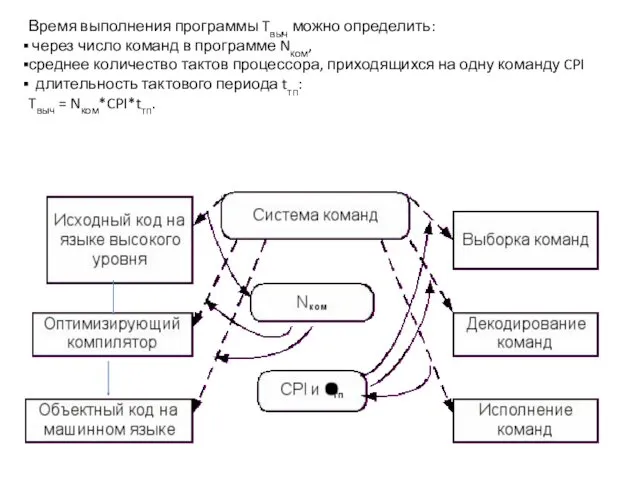

Время выполнения программы Tвыч можно определить:

через число команд в программе

Nком,

среднее количество тактов процессора, приходящихся на одну команду CPI

длительность тактового периода tтп:

Tвыч = Nком*CPI*tтп.

Слайд 3

Классификация архитектур системы команд

EDSAC,1950

IBM360, 1964

VAX,INTEL432,1977-80

CRAY1,1963-76

Mips,Sparc, 1987

Itanium, 1990-e

B5500,B6500,1963-66

IGNITE,2001

Слайд 4

Соотношение программ на ЯВУ и машинном языке

Слайд 5

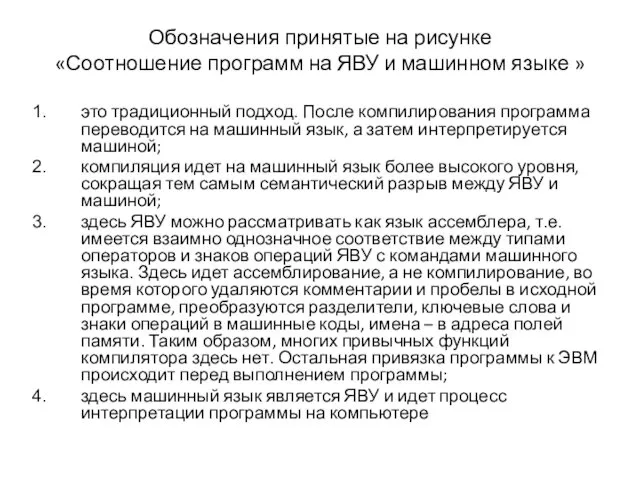

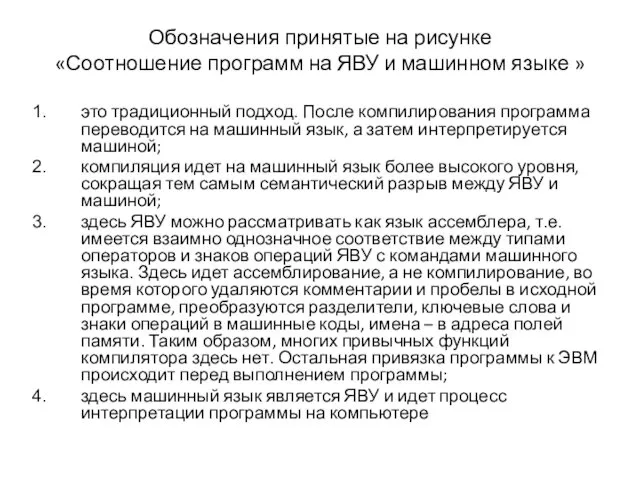

Обозначения принятые на рисунке

«Соотношение программ на ЯВУ и машинном языке »

это

традиционный подход. После компилирования программа переводится на машинный язык, а затем интерпретируется машиной;

компиляция идет на машинный язык более высокого уровня, сокращая тем самым семантический разрыв между ЯВУ и машиной;

здесь ЯВУ можно рассматривать как язык ассемблера, т.е. имеется взаимно однозначное соответствие между типами операторов и знаков операций ЯВУ с командами машинного языка. Здесь идет ассемблирование, а не компилирование, во время которого удаляются комментарии и пробелы в исходной программе, преобразуются разделители, ключевые слова и знаки операций в машинные коды, имена – в адреса полей памяти. Таким образом, многих привычных функций компилятора здесь нет. Остальная привязка программы к ЭВМ происходит перед выполнением программы;

здесь машинный язык является ЯВУ и идет процесс интерпретации программы на компьютере

Слайд 6

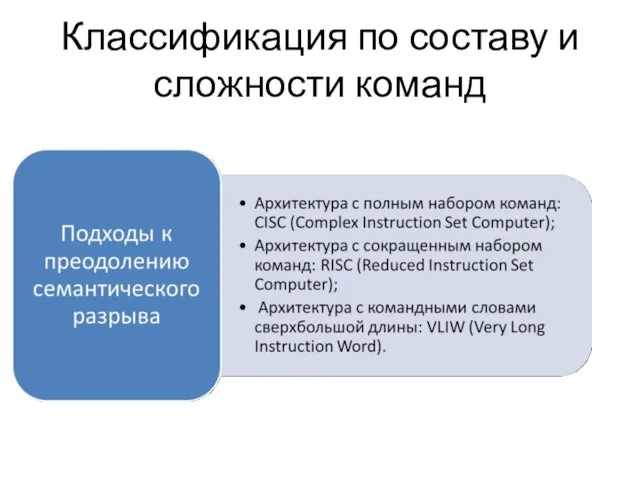

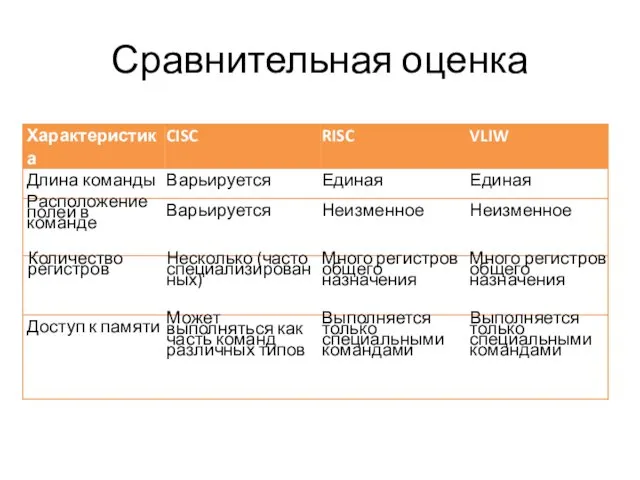

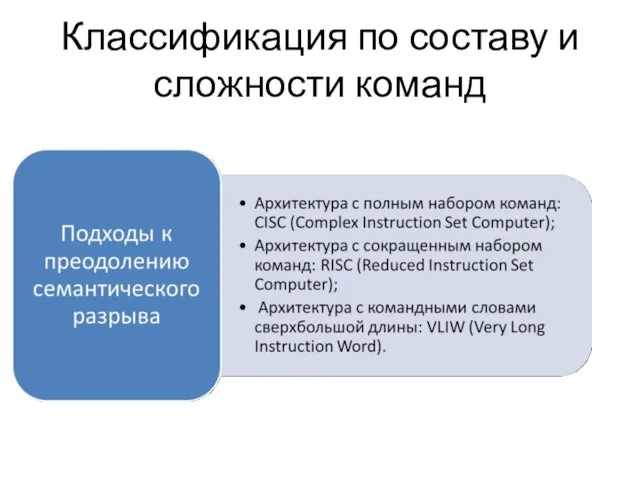

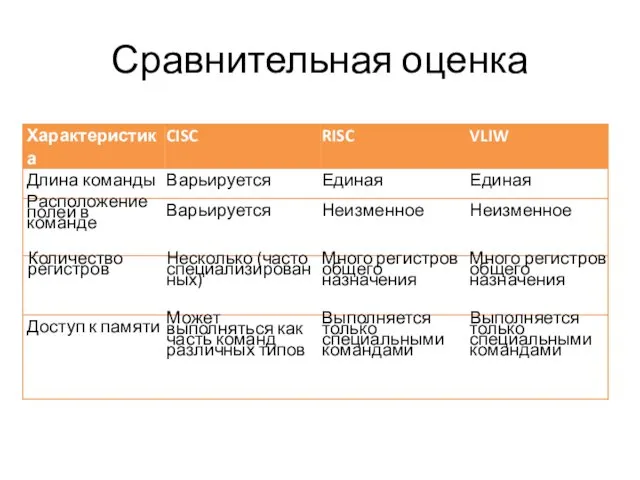

Классификация по составу и сложности команд

Слайд 7

Слайд 8

Классификация по месту хранения операндов

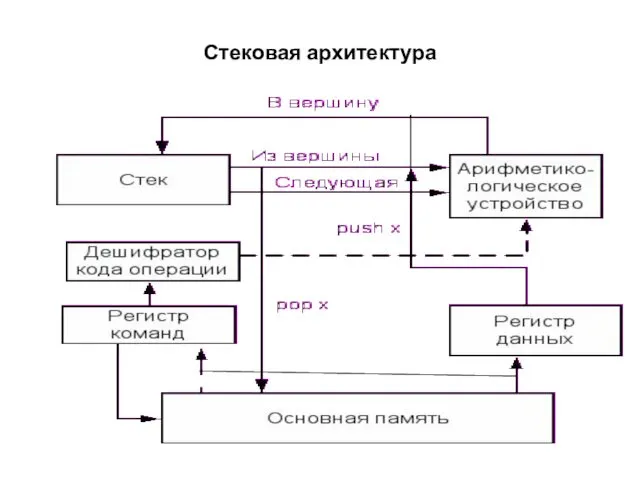

Стековая

Аккумуляторная

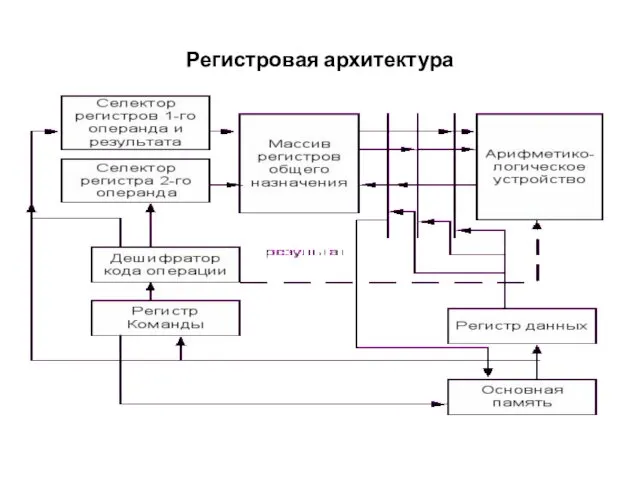

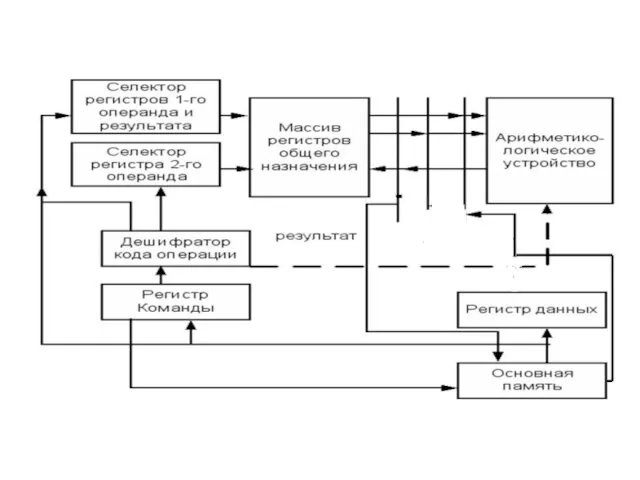

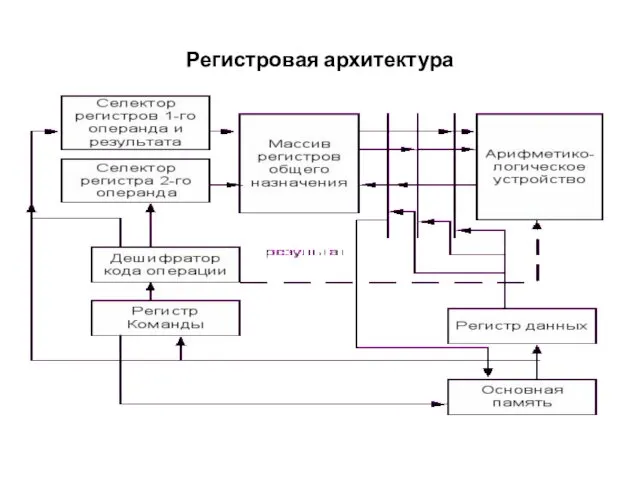

Регистровая

С выделенным доступом к памяти

Слайд 9

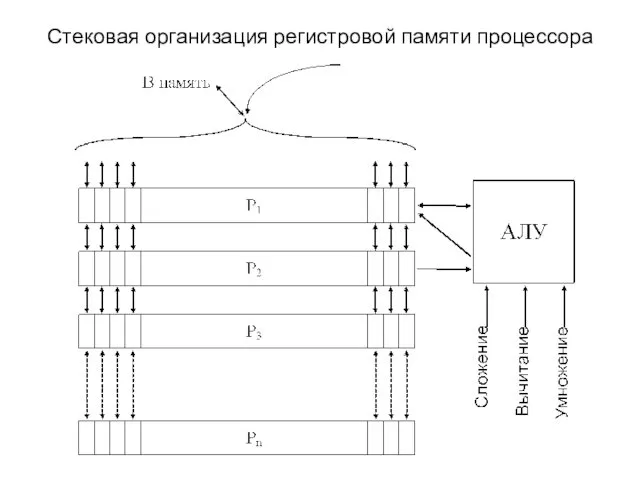

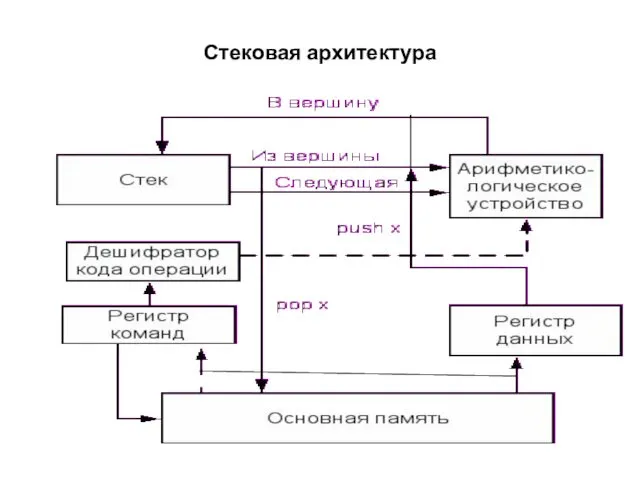

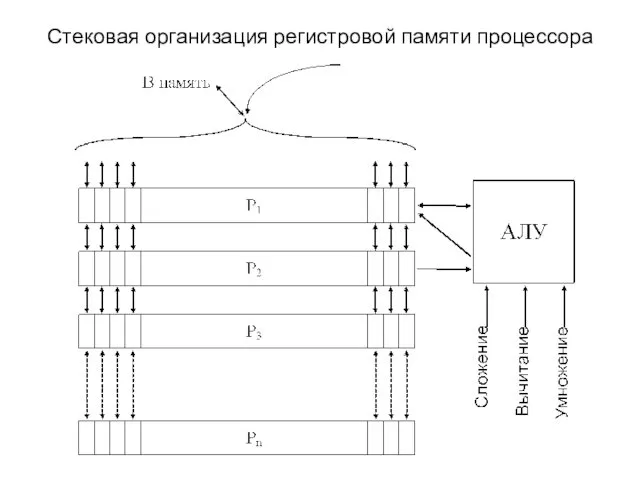

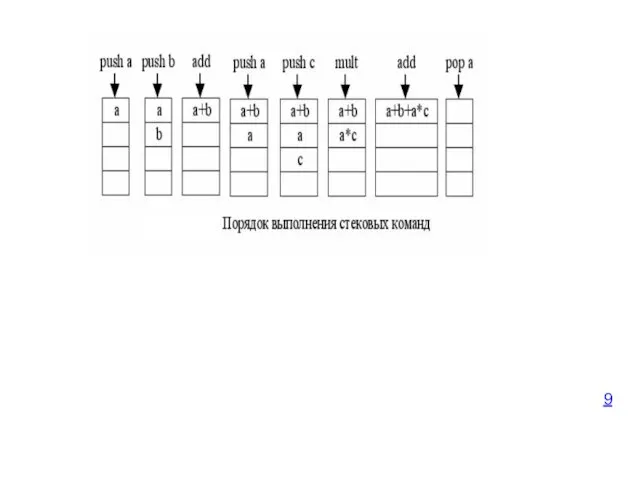

Стековая организация регистровой памяти процессора

Слайд 10

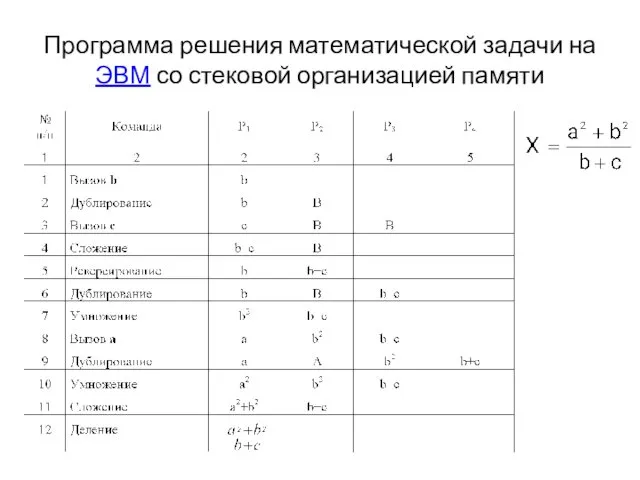

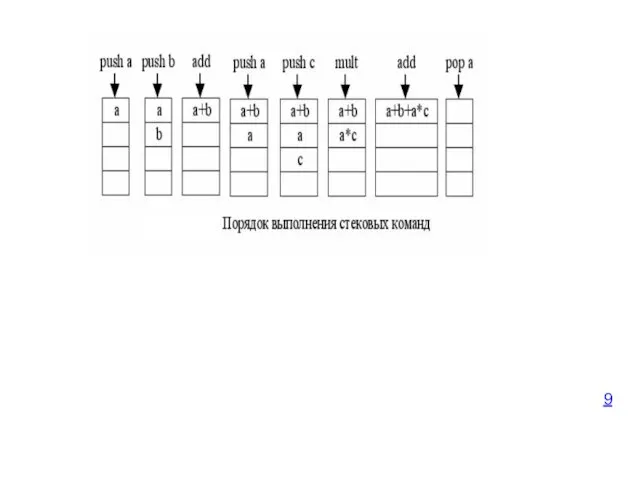

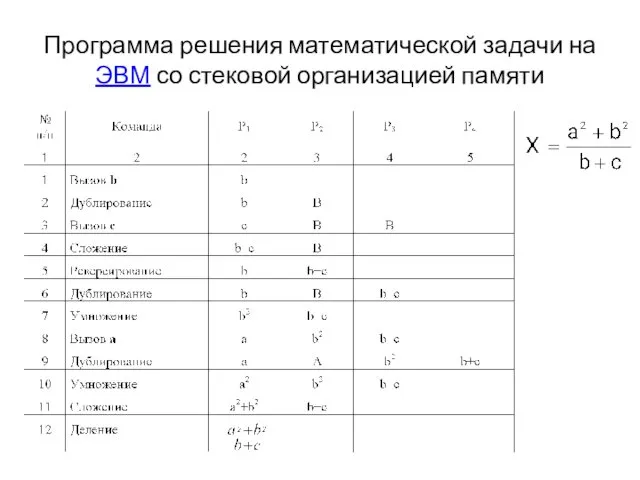

Программа решения математической задачи на ЭВМ со стековой организацией памяти

Слайд 11

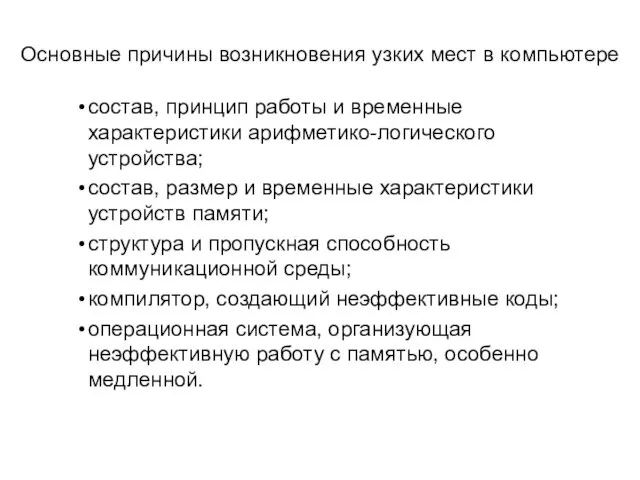

Основные причины возникновения узких мест в компьютере

состав, принцип работы и

временные характеристики арифметико-логического устройства;

состав, размер и временные характеристики устройств памяти;

структура и пропускная способность коммуникационной среды;

компилятор, создающий неэффективные коды;

операционная система, организующая неэффективную работу с памятью, особенно медленной.

Слайд 12

Слайд 13

Слайд 14

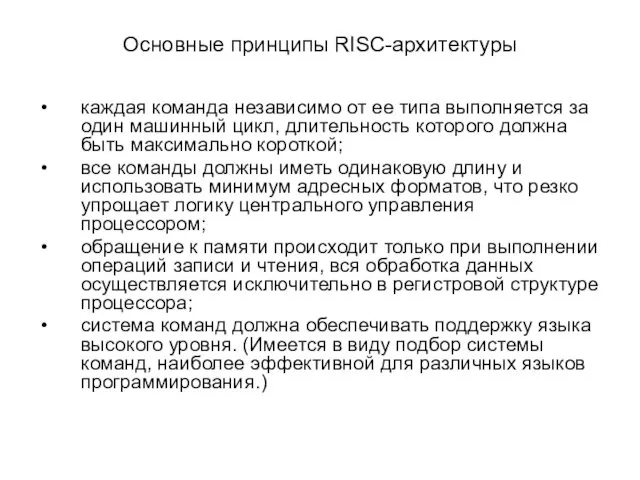

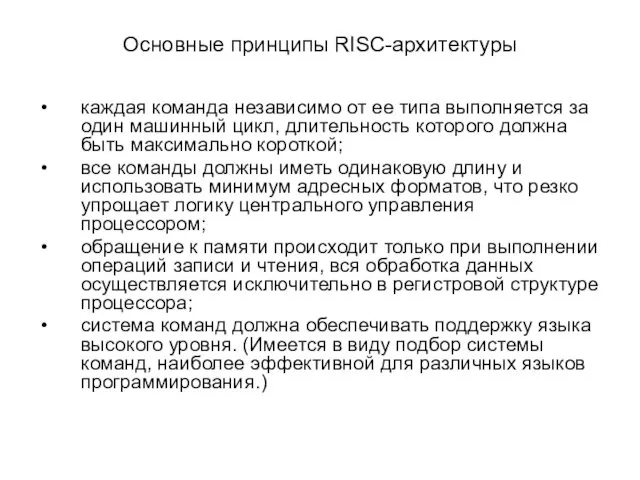

Основные принципы RISC-архитектуры

каждая команда независимо от ее типа выполняется за

один машинный цикл, длительность которого должна быть максимально короткой;

все команды должны иметь одинаковую длину и использовать минимум адресных форматов, что резко упрощает логику центрального управления процессором;

обращение к памяти происходит только при выполнении операций записи и чтения, вся обработка данных осуществляется исключительно в регистровой структуре процессора;

система команд должна обеспечивать поддержку языка высокого уровня. (Имеется в виду подбор системы команд, наиболее эффективной для различных языков программирования.)

Слайд 15

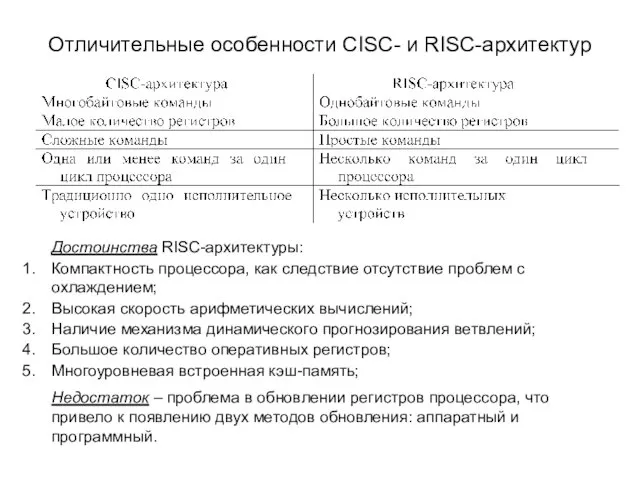

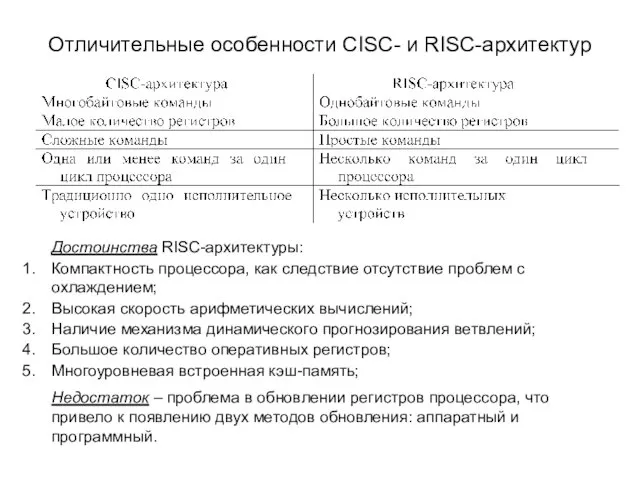

Отличительные особенности CISC- и RISC-архитектур

Достоинства RISC-архитектуры:

Компактность процессора, как следствие отсутствие проблем

с охлаждением;

Высокая скорость арифметических вычислений;

Наличие механизма динамического прогнозирования ветвлений;

Большое количество оперативных регистров;

Многоуровневая встроенная кэш-память;

Недостаток – проблема в обновлении регистров процессора, что привело к появлению двух методов обновления: аппаратный и программный.

Слайд 16

Слайд 17

Слайд 18

Слайд 19

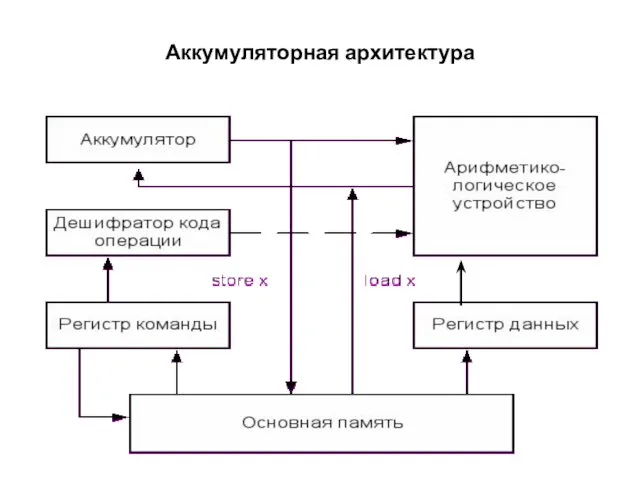

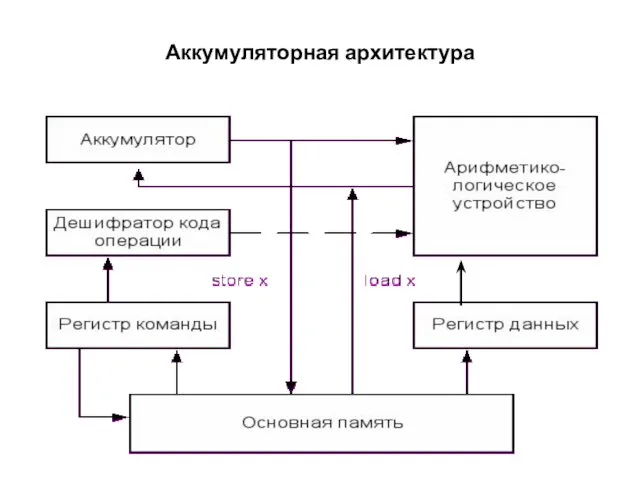

Аккумуляторная архитектура

Слайд 20

Слайд 21

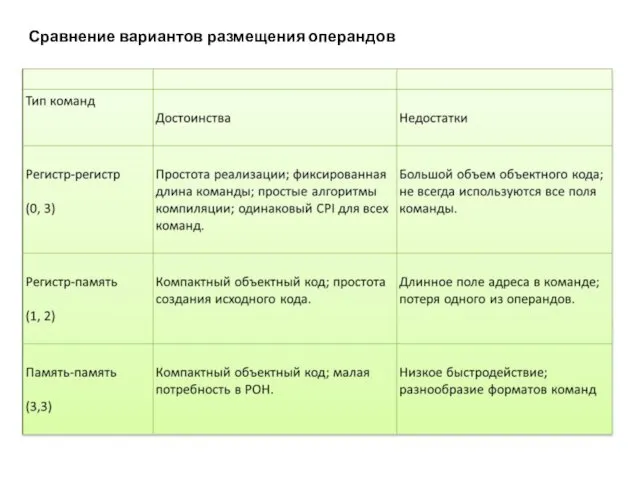

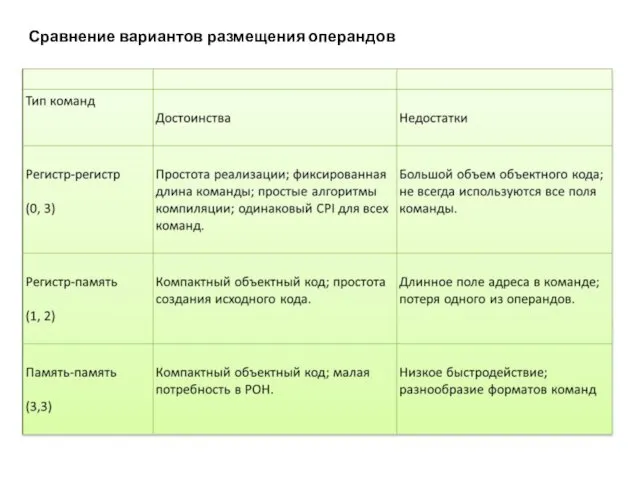

Сравнение вариантов размещения операндов

Слайд 22

Введение в PHP

Введение в PHP Методическая разработка урока информатики по теме Программное обеспечение компьютера.

Методическая разработка урока информатики по теме Программное обеспечение компьютера. Компьютерные сети

Компьютерные сети 04_ПЗ_27_Дз-21-11-1_Шиловская_ИОПД

04_ПЗ_27_Дз-21-11-1_Шиловская_ИОПД Молоко. Классификация молока по виду животного

Молоко. Классификация молока по виду животного Мое хобби

Мое хобби Инструкция по работе с TestRail

Инструкция по работе с TestRail Виды позиционных систем счисления

Виды позиционных систем счисления Медиатекст. Тексты и жанры

Медиатекст. Тексты и жанры Применение ИКТ на уроках математики

Применение ИКТ на уроках математики Как опубликовать научную статью

Как опубликовать научную статью History of Translation

History of Translation Алгоритм работы с программой IPHoto (авторская работа)

Алгоритм работы с программой IPHoto (авторская работа) Подростки в сети: современные медиа-угрозы

Подростки в сети: современные медиа-угрозы Виды противоправной информации

Виды противоправной информации Классы. Базовый класс

Классы. Базовый класс Разработка интеграционного модуля выгрузки данных о продажах фотосепараторов на корпоративный сайт ООО Сисорт

Разработка интеграционного модуля выгрузки данных о продажах фотосепараторов на корпоративный сайт ООО Сисорт Партицирование данных. Модели данных и нормализация таблиц. Урок 4

Партицирование данных. Модели данных и нормализация таблиц. Урок 4 Генетические алгоритмы

Генетические алгоритмы Основные этапы развития информационного общества. Этапы развития технических средств и информационных ресурсов

Основные этапы развития информационного общества. Этапы развития технических средств и информационных ресурсов Текстовые редакторы

Текстовые редакторы Разработка файловой системы

Разработка файловой системы презентация Устройства ПК

презентация Устройства ПК Комп’ютерна графіка

Комп’ютерна графіка Используем язык программирования Scratch во внеурочной деятельности

Используем язык программирования Scratch во внеурочной деятельности Лекция 5. Модели жизненного цикла программного обеспечения

Лекция 5. Модели жизненного цикла программного обеспечения Построение диаграмм с помощью табличного процессора MS Excel

Построение диаграмм с помощью табличного процессора MS Excel Искусственный интеллект и его применение в дизайне

Искусственный интеллект и его применение в дизайне